Fターム[5F110FF29]の内容

Fターム[5F110FF29]の下位に属するFターム

Fターム[5F110FF29]に分類される特許

2,861 - 2,878 / 2,878

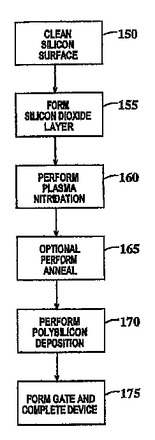

窒化シリコン酸化物ゲート誘電体を製造する方法

【課題】 ウェハ内における相対的に均一な厚さ及び窒素濃度を有するSiOxNy層を製造する方法を提供すること。

【解決手段】 基板を準備するステップと、該基板の上面に二酸化シリコン層を形成するステップと、還元雰囲気内でプラズマ窒化を実行し、該二酸化シリコン層を酸窒化シリコン層に変換するステップとを含む、ゲート誘電体層を製造する方法である。このように形成された誘電体層を、MOSFETの製造において用いることができる。

(もっと読む)

ナノワイヤ複合体およびこれらに由来する電子基板を作製するためのシステムおよび方法

本発明は、ナノワイヤ−材料複合体を生成するシステムおよび処理に関わる。ナノワイヤ(606)が少なくとも一つの表面の一部分(604)に取り付けられた基板が提供される。ナノワイヤ−材料複合体を生成するよう、当該部分上に材料が堆積される。処理は、独立したナノワイヤ−材料複合体を生成するよう基板からナノワイヤ−材料複合体を分離することを必要に応じて含む。独立したナノワイヤ−材料複合体は、必要に応じて、電子基板に更に処理される。様々な電子基板は本明細書記載の方法を用いて形成される。例えば、多色発光ダイオードは、それぞれの複合体層が異なる波長で光を発するナノワイヤ−材料複合体の多数の積層された層から形成され得る。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

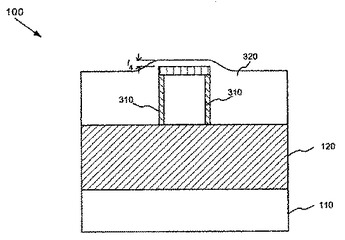

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

線パターン形成方法、デバイスとその製造方法及び電気光学装置並びに電子機器

【課題】複数の線パターンの形成領域から一時的に溢れ出した機能液同士が接触しないように機能液を吐出することによって短絡を防止すると共に、線パターンと線パターンとをより近接させる。

【解決手段】線パターンの形成方法であって、隣合うバンク間34から一時的に溢れ出した上記機能液X同士が接触しないように各上記バンク間34の幅方向の中央Aに対し当該幅方向に変位した位置を各々のバンク間34の吐出位置として上記機能液Xを吐出することによって複数の上記バンク間34に同時に機能液を配置する。

(もっと読む)

自己組織化単分子層を含む電子デバイスおよびこれを製造する方法

【課題】 電子特性が向上した分子層を有する電子デバイスを提供すること。

【解決手段】 電子デバイスは、ソース領域およびドレイン領域と、ソース領域およびドレイン領域に隣接して配置され、少なくとも1つの共役分子を含む自己組織化単分子層と、自己組織化単分子層に隣接した導電性基板と、を含む。

(もっと読む)

薄膜トランジスタを備えた平板表示装置

【課題】 薄膜トランジスタを備えた平板表示装置を提供する。

【解決手段】 各駆動薄膜トランジスタの活性層の結晶粒の差によって、そして、駆動薄膜トランジスタの活性層のサイズを変更せずホワイトバランスを合せ、各副画素に最適の電流を供給することによって適正な輝度を得、寿命を短縮させないようにするためのものであって、自己発光素子を備えた複数の副画素を含む画素と、前記各副画素に備えられて少なくともチャンネル領域を有する半導体活性層を備え、前記自己発光素子に各々接続されて電流を供給するものであって、前記活性層の少なくともチャンネル領域が前記副画素別にその結晶粒のサイズまたは形状が相異なるように備えられた駆動薄膜トランジスタと、を含むことを特徴とする平板表示装置。

(もっと読む)

薄膜トランジスタを具備したフラットパネルディスプレイ

【課題】 駆動用TFTの活性層の大きさを変更せずに、同じ駆動電圧を加えた状態でもホワイトバランスを合わせられるフラットパネルディスプレイを提供する。また、各副画素に最適の電流を供給することによって適正な輝度を実現し、寿命が長いフラットパネルディスプレイを提供する。

【解決手段】 自発光素子を具備する複数の副画素を含む画素と、前記副画素の各々に備えられた、少なくともチャンネル領域を有する半導体活性層を具備し、前記自発光素子に電流を供給するために前記自発光素子に接続されてなる、駆動用薄膜トランジスタ(20r、20g、20b)とを含むフラットパネルディスプレイであって、前記半導体活性層のチャンネル領域が、少なくとも2つの前記副画素に関して相異なる方向に配置されてなることを特徴とするフラットパネルディスプレイである。

(もっと読む)

有機薄膜トランジスタ

【課題】特殊な技術を要せず、簡単な製造方法でキャリア移動度が高い有機薄膜トランジスタを提供すること。

【解決手段】有機半導体層に重量平均分子量2000以上のπ共役系ポリマー及び分子量2000以下のπ共役系オリゴマーを含有することを特徴とする有機薄膜トランジスタ。

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

液晶表示装置用薄膜トランジスタ基板及びその製造方法並びに液晶表示装置

【課題】 本発明の目的は、液晶配向の不良を減少させ、開口率を高めることにある。

【解決手段】 第1絶縁基板と、第1絶縁基板上部に形成されており、ゲート電極を有するゲート線と、ゲート線を覆うゲート絶縁膜と、ゲート絶縁膜上部に形成されている半導体層と、半導体層上部に形成されているソース電極及びドレイン電極とソース電極に連結されており、ゲート線と交差するデータ線と、有機絶縁膜からなっており、ドレイン電極を露出する第1接触孔を有する保護膜と、第1接触孔を通じてドレイン電極と連結されている画素電極と、第1絶縁基板と対向する第2絶縁基板と、ゲート線またはデータ線と重なるブラックマトリックスと、第1絶縁基板と第2絶縁基板の間でブラックマトリックスと重なって位置し、写真エッチング工程で形成された基板スペーサとを含む液晶表示装置を提供する。

(もっと読む)

配線構造、その製造方法、および表示装置

【課題】 配線構造と他の電極間のショートを防ぐ。

【解決手段】 SiO2により構成されたゲート絶縁膜12およびその上に積層され、SiNにより構成された層間絶縁膜13に、緩衝フッ酸を用いたエッチングによりコンタクトホールを形成する。このコンタクトホールに、高融点金属により構成された第1の保護金属層170と、高融点金属よりも抵抗の低い金属により構成された配線層172と、および高融点金属により構成され、ゲート絶縁膜12よりも厚く形成された第2の保護金属層174とがこの順で積層された電極53を形成する。

(もっと読む)

液晶表示装置の製造方法

【課題】 画素電極近傍の光り抜けを防止できるアクティブマトリックス型液晶表示装置の製造方法を提供すること。

【解決手段】 アレイ基板に対して略平行な電界を発生させることにより、液晶分子の配列を変化させる、アクティブマトリックス型液晶表示装置において、アレイ基板10上に、配線を形成した後透明な絶縁膜20を成膜する工程と、該配線側面に、該配線の膜厚に対する比が0.5以上1.0以下の膜厚の前記絶縁膜を残すように、該絶縁膜をドライエッチングする工程と、前記配線の膜厚に対する比が0.2以下の膜厚の前記配線のみ、ウェットエッチングする工程とを含むようにした。

(もっと読む)

薄膜トランジスタアレイ及びその製造方法、液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法

【課題】 本発明は薄膜トランジスタアレイ及びその製造方法と液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法に関するものであり、均一性と性能に優れた薄膜トランジスタ及びその製造方法を生産性が高く低コストで提供することを目的とする。

【解決手段】 ゲート電極側面に側壁を形成することによって、自己整合的にLDDまたはオフセット領域を形成し、また、層間絶縁膜を複数の層で形成し、これら複数の層間絶縁膜上にソース・ドレイン電極とソースバス配線と画素電極を一括して形成する。

(もっと読む)

半導体膜形成方法及び薄膜半導体装置の製造方法

【課題】 本発明の目的は、基板上に高品質な半導体膜を形成するための半導体膜形成方法を提供することにある。

【解決手段】 本発明は、バイアス触媒CVD,高密度バイアス触媒CVD,バイアス減圧CVD,バイアス常圧CVDを利用して、基板に半導体膜を形成する半導体膜形成方法である。真空容器1に原料ガスを供給し、真空容器1中に配置された基板10と電極3aとの間にグロー放電開始電圧以下の電界を印加して、基板10上に、少なくとも錫、ゲルマニウム、鉛のいずれか一つ以上を含有する半導体膜と、絶縁膜と、を形成することを含む工程と、この半導体膜および絶縁膜にレーザーを照射してアニールする工程と、このアニールする工程の後工程であって、水蒸気でアニールを行う工程と、を備える。

(もっと読む)

薄膜トランジスタとその製造方法

【課題】 ソース/ドレイン電極材料に銅を用いた場合の加工時のバリアメタル層のアンダーカットに起因する特性不良を防止し、低抵抗配線が充分に実現できるTFTの構造とその製造方法を提供する。

【解決手段】 本発明のTFTの構造は、ガラス基板2上のゲート電極3と、ゲート絶縁膜4と、ゲート絶縁膜4上にゲート電極3に対向配置された半導体能動層5と、半導体能動層5の両端部上に設けられたオーミックコンタクト層6と、各オーミックコンタクト層6を介して半導体能動層5に電気的に接続されたソース電極7、ドレイン電極8とを有している。そして、ソース電極7およびドレイン電極8が銅で形成され、これらソース電極7、ドレイン電極8の下面のうち、各オーミックコンタクト層6の上面上に位置する領域にのみバリアメタル層9が設けられている。

(もっと読む)

積層金属配線及び薄膜トランジスタ基板、並びにそれらの製造方法

【課題】 IC等の半導体装置や、表示装置に用いられるTFT基板で使用される、Alを含む積層配線の信頼性を高める。

【解決手段】 上層の金属層22を下層のAl又はAlを含む合金材料層21の露出した側壁を少なくとも部分的に隠蔽するよう下方に湾曲させる。この積層配線は、エッチングによりこれを作製する際に、上層の金属層22よりも下層のAl又はAlを含む合金の材料層21の方のエッチング速度を大きくして、Al又はAlを含む合金の材料層21のサイドエッチングを多くし、上層の金属層22を下層のアルミニウム又はアルミニウムを含む合金材料層21の露出した側壁を少なくとも部分的に隠蔽するよう下方に湾曲させることで作製できる。

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

2,861 - 2,878 / 2,878

[ Back to top ]