Fターム[5F110FF29]の内容

Fターム[5F110FF29]の下位に属するFターム

Fターム[5F110FF29]に分類される特許

61 - 80 / 2,878

半導体装置およびその作製方法

【課題】酸化物半導体を用いたボトムゲート型のトランジスタにおいて、高いゲート電圧がゲート電極層に印加される場合、ドレイン電極層の端部近傍(及びソース電極層の端部近傍)に生じる恐れのある電界集中を緩和し、スイッチング特性の劣化を抑え、信頼性が向上された構造を提供する。

【解決手段】チャネル形成領域上に重なる絶縁層の断面形状を、テーパ形状とし、チャネル形成領域上に重なる絶縁層の膜厚は、0.3μm以下、好ましくは5nm以上0.1μm以下とする。チャネル形成領域上に重なる絶縁層の断面形状の下端部のテーパ角θを60°以下、好ましくは45°以下、さらに好ましくは30°以下とする。

(もっと読む)

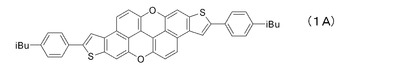

ジオキサアンタントレン系化合物及び電子デバイス

【課題】高い安定性を有し、プロセスに対する適応性が高い有機半導体材料に適する新規化合物、及び該化合物からなる半導体層を備えた電子デバイスの提供。

【解決手段】ジオキサアンタントレン系化合物であり、は、代表的なものとして、下記で示される化合物、及び

該化合物からなる半導体層を備えた電子デバイス。 (もっと読む)

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、インジウムを含む酸化物半導体膜、ゲート電極層と重畳する酸化物半導体膜上に接する絶縁層が順に積層され、酸化物半導体膜及び絶縁層に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、絶縁層表面における塩素濃度を1×1019/cm3以下とし、かつインジウム濃度を2×1019/cm3以下とする。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法及び画像表示装置

【課題】アライメント精度良く半導体層を形成し、かつ、プロセス数を増やすことなくトランジスタの素子分離を行うことのできる薄膜トランジスタ、薄膜トランジスタの製造方法及び画像表示装置を提供する。

【解決手段】薄膜トランジスタ50は、基板1と、基板1上に形成されたゲート電極2と、基板1とゲート電極2とにわたって、これらの上に形成されたゲート絶縁体層4と、ゲート絶縁体層4上に形成された半導体層5と、半導体層5上に形成された保護層6と、ゲート絶縁体層4と半導体層5と保護層6とにわたって、これらの上に形成された、ソース電極7及びドレイン電極8と、を有し、半導体層5における、ソース電極7とドレイン電極8との間のチャネル部を流れる電流の方向の一端5aは、ソース電極7の一端7aと一致し、半導体層5における他端5bは、ドレイン電極8の一端8aと一致している。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

表示装置

【課題】高開口率を有し、容量の大きな保持容量を有する表示装置を提供する。

【解決手段】第1導電膜によるゲート電極と、第1導電膜上の第1絶縁層によるゲート絶縁膜と、第1絶縁層上にゲート電極と重なる第1半導体層と、第1半導体層上かつゲート電極に重なる第2絶縁層によるチャネル保護膜と、第1半導体層と重なりソース領域及びドレイン領域に分離された導電性の第2半導体層と、第2半導体層上の第2導電膜によるソース電極及びドレイン電極とを含む薄膜トランジスタと、第2導電膜上に形成された第3絶縁層と、第3絶縁層上の第3導電膜により形成され、ソース電極またはドレイン電極の一方と接続する画素電極と、第1絶縁層上の容量配線と、容量配線上の第3絶縁層を挟んで、画素電極の重畳領域に形成される保持容量とを有する表示装置及びその作製方法。

(もっと読む)

半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】ソース電極層405a及びドレイン電極層405bの端部と、ゲート電極層401の端部とを重畳させ、更に酸化物半導体層403のチャネル形成領域となる領域に対して、ゲート電極層401を確実に重畳させることで、トランジスタのオン特性を向上させる。また、絶縁層491中に埋め込み導電層を形成し、埋め込み導電層481a,481bと、ソース電極層405a及びドレイン電極層405bとの接触面積を大きくとることで、トランジスタのコンタクト抵抗を低減する。ゲート絶縁層402のカバレッジ不良を抑制することで、酸化物半導体層403を薄膜化し、トランジスタの微細化を実現する。

(もっと読む)

透明バイオセンサ

【課題】TFTを有するバイオセンサを用いて顕微鏡観察と同時に生体関連物質の信号情報を取得する場合に、その信号情報を正確に取得することができる透明バイオセンサを提供する。

【解決手段】透明基材1と、透明基材1上に設けられた透明な薄膜トランジスタ素子部A及び透明な生体関連物質感応部Bとを有し、その薄膜トランジスタ素子部Aが有するゲート電極2を、薄膜トランジスタ素子部Aを構成する酸化物半導体膜4に対する紫外線カット機能を有するように構成して、上記課題を解決した。このゲート電極2を、(i)紫外線カット材料を含む透明電極、(ii)紫外線カット材料からなる透明電極、及び、(iii)前記酸化物半導体膜のバンドギャップよりも小さいバンドギャップを持つ透明電極、のいずれかであるように構成する。

(もっと読む)

半導体装置

【課題】良好な特性を備えた、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、ソース電極およびドレイン電極は、その側面が酸化された酸化領域を有する半導体装置である。なお、ソース電極およびドレイン電極の酸化領域は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理により形成されたものであることが望ましい。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

薄膜トランジスタアレイ及びその製造方法、並びに電気泳動ディスプレイ

【課題】画素電極間の距離が大きくて印刷に適し、しかも画素電極間の距離が大きい場合でも所望の表示を行うことができること。

【解決手段】薄膜トランジスタアレイは、絶縁基板1上に、少なくともゲート電極2と、ゲート絶縁膜3と、ソース電極4と、ドレイン電極5と、前記ドレイン電極5に接続された画素電極9と、ソース電極4とドレイン電極5との間に形成された半導体層6と、を有する薄膜トランジスタを、複数のゲート電極2がゲート配線2aに接続され、複数のソース電極4がソース配線4aに接続された状態でマトリクス状に配置した薄膜トランジスタアレイであって、隣り合う画素電極9の間の部分を線とし、複数の前記線が交わる部分を節として表したときに、画素電極9の配置が、1つの前記節に3本の前記線がつながる配置となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ドレイン−ソース間のリーク電流が少なく、かつ、ノーマリーオフの半導体装置を提供する。

【解決手段】基板11の上に形成された不純物元素を含む第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層16と、第2の半導体層16の上に形成された第3の半導体層17と、第3の半導体層17の上に形成されたゲート電極21、ソース電極22及びドレイン電極23と、を有し、第2の半導体層16において、ゲート電極21の直下には、第1の半導体層13と接し、第1の半導体層13に含まれる不純物元素が拡散している不純物拡散領域15が形成されており、不純物元素は、不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

(もっと読む)

薄膜トランジスタ、その製造方法、および表示装置

【課題】酸化物半導体を用いた低温プロセスで形成する信頼性の高い薄膜トランジスタ、その製造方法、および表示装置を提供する。

【解決手段】薄膜トランジスタ1は、基板100と、前記基板上の一部に設けられたゲート電極110と、前記ゲート電極を覆う第1の絶縁膜120と、前記第1の絶縁膜を介して前記ゲート電極上に設けられた酸化物半導体膜130と、前記酸化物半導体膜上の一部に設けられた第2の絶縁膜150と、前記酸化物半導体膜から露出する酸化物半導体膜の一部と接続されたソース電極140Sおよびドレイン電極140Dと、を備え、前記酸化物半導体膜はInと、Gaと、Znのうち少なくとも一つの元素を含む酸化物半導体を有し、前記第1の絶縁膜中に含有される水素濃度が5×1020atm/cm−3以上であり、かつ、前記第2の絶縁膜中に含有される水素濃度が1019atm/cm−3以下である。

(もっと読む)

熱処理方法

【課題】シリコンゲルマニウム層の弛緩を抑制しつつ、高誘電率膜の結晶化を促進することができる熱処理方法を提供する。

【解決手段】ゲルマニウム濃度が相対的に低濃度のシリコンゲルマニウムの両側を高濃度のシリコンゲルマニウムにて挟み込んだシリコンゲルマニウム層を半導体ウェハー上に形成する。その低濃度のシリコンゲルマニウムの上に二酸化ケイ素の膜を挟んで高誘電率膜を形成する。この半導体ウェハーにフラッシュランプから第1照射を行ってその表面温度を予備加熱温度T1から目標温度T2にまで3ミリ秒以上1秒以下にて昇温する。続いて、フラッシュランプから第2照射を行って半導体ウェハーの表面温度を目標温度T2から±25℃以内の範囲内に3ミリ秒以上1秒以下維持する。これにより、シリコンゲルマニウム層の歪みの緩和を抑制しつつ、高誘電率膜の結晶化を促進することができる。

(もっと読む)

半導体装置

【課題】電子走行層にFeが入り込むことを抑制し、半導体層等にクラックの発生が抑制される電界効果型トランジスタを提供する。

【解決手段】基板11の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層14と、高抵抗層14の上に形成された多層中間層15と、多層中間層15の上に半導体材料により形成された電子走行層16と、電子走行層の上に半導体材料により形成された電子供給層17と、を有し、多層中間層15は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

(もっと読む)

薄膜トランジスタ、画像表示装置

【課題】酸化物半導体層のバックチャネル部を半導体層成膜後の薄膜トランジスタ作製工程によるダメージから保護し、良好なトランジスタ特性を得ると共に、薄膜トランジスタ作製の工程数を削減することである。

【解決手段】基板1と、基板1上に設けられたゲート電極2と、基板1上に設けられ、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上に設けられ、アモルファス酸化物からなる半導体層4と、半導体層4上に設けられた保護膜5と、ゲート絶縁膜3上に設けられたソース電極6、及びドレイン電極7と、を備え、保護膜5を、金属材料の化成処理、又は陽極酸化によって形成する。

(もっと読む)

CMOS半導体装置の製造方法及びCMOS半導体装置

【課題】マイクロコンタクト印刷の版を凹版として使用し、微細な電気回路と高生産性のCMOS半導体装置の製造方法を提供するものである。

【解決手段】Pチャネル型電界効果トランジスタのPチャネル領域101とNチャネル型電界効果トランジスタのNチャネル領域102とを、凹版601を用いた印刷によって形成するようにし、凹版601が、第1凹部602と第2凹部603とを備え、インクジェット法によって、第1凹部602にP型半導体インク111を供給し、第2凹部603にN型半導体インク112を供給する工程と、インク供給後に、凹版601を被印刷基板001に押しつけて、第1凹部602に供給したP型半導体インク111と第2凹部603に供給したN型半導体インク112とを一括して被印刷基板001に転写する工程と、を含むCMOS半導体装置の製造方法を提供する事により、上記課題を解決する。

(もっと読む)

61 - 80 / 2,878

[ Back to top ]