Fターム[5F110FF29]の内容

Fターム[5F110FF29]の下位に属するFターム

Fターム[5F110FF29]に分類される特許

21 - 40 / 2,878

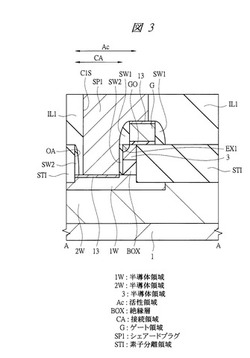

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

薄膜トランジスタ

【課題】バックライトの間接光に起因するリーク電流を低減可能な薄膜トランジスタを提供する。

【解決手段】表示装置用のボトムゲート型の薄膜トランジスタであって、基板1と、ゲート電極配線2と、ゲート絶縁膜3と、チャネルとなる第1の半導体層4と、第1及び第2のコンタクト層5a、5bとなる第2の半導体層と、ソース又はドレイン電極配線7a、7bとを有し、ソース又はドレイン電極配線7a、7bに対して露出する第2の半導体層の露出部に、絶縁性半導体層6a、6bが形成されている。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜のソース領域およびドレイン領域の導電率を高めることで、高いオン特性を有する酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】第1の領域および第2の領域を有し、少なくともインジウム(In)を含む酸化物半導体膜と、少なくとも酸化物半導体膜の第1の領域と重畳して設けられたゲート電極と、酸化物半導体膜およびゲート電極の間に設けられたゲート絶縁膜と、少なくとも一部が酸化物半導体膜の第2の領域と接して設けられた電極と、を有し、酸化物半導体膜は、酸化物半導体膜と電極との界面近傍のInの濃度が高く、界面から15nmの範囲で遠ざかるに従いInの濃度が低くなる。なお、酸化物半導体膜の第1の領域はトランジスタのチャネル領域として機能し、第2の領域はトランジスタのソース領域、ドレイン領域として機能する。

(もっと読む)

半導体素子基板の製造方法および半導体素子基板並びに表示装置

【課題】結晶異方性を有する領域と結晶異方性を有さない領域とを含む結晶化半導体膜を用いて薄膜トランジスタの集積化を容易に行なうことができる半導体素子基板の製造方法および半導体素子基板を提供する。

【解決手段】絶縁基板上に成膜した非晶質半導体膜56の下方に加熱促進層30を形成した領域と、加熱促進層30を形成しない領域とを設け、非晶質半導体膜56にレーザビーム18を照射する。このとき、加熱促進層30によってレーザビーム18が反射または吸収されることにより、非晶質半導体膜56は裏面側からも結晶化が促進される。これにより、加熱促進層30が形成された領域には結晶の配向が揃った第1の結晶性半導体膜54が形成され、形成されない領域には結晶の配向がランダムな第2の結晶性半導体膜55が形成される。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供する。該半導体装置を作製する。半導体装置を歩留まりよく作製し、生産性を向上させる。

【解決手段】ゲート電極層、ゲート絶縁膜、酸化物半導体膜が順に積層され、酸化物半導体膜に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、エッチング工程によりゲート電極層、又はソース電極層及びドレイン電極層を形成後、ゲート電極層又は酸化物半導体膜表面及び該近傍に存在するエッチング工程起因の残留物を除去する工程を行う。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、半導体層として機能する酸化物半導体膜と、酸化物半導体膜上のシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有し、少なくともゲート電極と重畳する酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%以下の濃度で分布する領域を有する構造とする。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極や走査線(ゲート線)及びデータ線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供する。

【解決手段】半導体膜107と基板との間に第1の絶縁膜を介して設けられた第1の配線102を、半導体膜107と重ねて設け、遮光膜として用いる。さらに半導体膜上にゲート絶縁膜として用いる第2の絶縁膜を形成し、第2の絶縁膜上にゲート電極と第2の配線134を形成する。第1及び第2の配線は、第1及び第2の絶縁膜を介して交差する。第2の配線134の上層には、層間絶縁膜として第3の絶縁膜を形成し、その上に画素電極147を形成する。画素電極147は、第1の配線及び第2の配線とオーバーラップさせて形成することが可能であり、反射型の表示装置において画素電極147の面積を大型化できる。

(もっと読む)

半導体装置、及びその作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置を提供する。また、微細化された半導体装置を歩留まりよく提供する。

【解決手段】絶縁表面を有する基板上に設けられた酸化物半導体膜と、酸化物半導体膜の側面に接して設けられ、かつ酸化物半導体膜よりも膜厚が大きいソース電極層及びドレイン電極層と、酸化物半導体膜、ソース電極層、及びドレイン電極層上に設けられたゲート絶縁膜と、酸化物半導体膜の上面と、ソース電極層及びドレイン電極層の上面との間に生じた段差により生じた凹部に設けられたゲート電極層と、を有する構造である。

(もっと読む)

配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置

【課題】透明導電膜上における絶縁膜の膜浮きの発生を抑え、且つ、透明導電膜と金属膜との良好な電気的接続性を得ることができる配線構造を提供する。

【解決手段】それぞれ配線として機能する第1の導電膜2と第2の導電膜5と接続する配線変換部45において、第2の導電膜5の内側には刳り抜き部13が形成される。第2の導電膜5の上に設けられる第2の導電膜5は、第2の導電膜5の上面および刳り抜き部13に露出した端面を覆い、且つ、第2の導電膜5の外周の端面を覆わないように形成される。第1の透明導電膜6の上層の第2の透明導電膜7が、第2の導電膜5と第1の導電膜2とに接続することにより、第1の導電膜2と第2の導電膜5とが電気的に接続される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】ソース電極層及びドレイン電極層上を覆うように酸化物半導体層を成膜した後、ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を研磨により除去する。ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜の水素濃度および酸素欠損を低減する。また、酸化物半導体膜を用いたトランジスタを有する半導体装置の信頼性を向上させる。

【解決手段】下地絶縁膜と下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜に重畳して設けられたゲート電極と、を有し、下地絶縁膜は、電子スピン共鳴にてg値が2.01で信号を表し、酸化物半導体膜は、電子スピン共鳴にてg値が1.93で信号を表さない半導体装置である。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜近傍の酸化物半導体膜に含まれる不純物元素濃度を低減する。また、ゲート絶縁膜近傍の酸化物半導体膜の結晶性を向上させる。また、当該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたソース電極、及びドレイン電極と、酸化物半導体膜、ソース電極、及びドレイン電極上に形成されたシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記酸化物半導体膜と重畳する領域に設けられたゲート電極と、を有し、酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度である領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

SOI基板の作製方法および作製装置

【課題】単結晶半導体基板とベース基板の界面に空気層が残ることに起因した、ベース基板から単結晶半導体基板を引き剥がした際に生じる転載不良領域の発生が抑制された、高品位なSOI基板の作製方法および作製に用いる貼り合わせ装置を提供することを課題とする。

【解決手段】ボンド基板を、ベース基板の設置面に対して傾斜角を持たせた状態で貼り合わせる。これにより、貼り合わせ開始箇所を限定できる。また、ボンド基板の一部が支持台からはみ出し、且つ、支持台からはみ出した部分がベース基板に最も近くなる状態にボンド基板を設置した。これにより、ボンド基板とベース基板の接触箇所下部には支持台がなく、ボンド基板の一部は支持台の端部を支点として支持台から浮かんだ状態となり、ベース基板に近づいた部分から順次貼り合わせが進むため、ボンド基板とベース基板の界面に空気層残りが生じることなく安定した貼り合わせを行うことができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタを具備する画素において、開口率の向上を図る。

【解決手段】酸化物半導体を用いたトランジスタ881は、リーク電流が小さいため、画素880内の容量素子を設ける必要がなくなる。または容量素子を小さくすることができ、たとえば液晶容量よりも小さくすることができる。これらによって、画素880の開口率を向上することができる。前記トランジスタのチャネル形成領域は、酸化物半導体を有し、前記容量素子の容量は、前記液晶素子の容量よりも小さい。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタでは、酸化物半導体膜への水素原子の混入が信頼性に悪影響を与える。製造後の半導体装置に混入しうる、水素原子を有する物質として代表的なものは、水である。そこで酸化物半導体を用いた半導体装置に混入する、水素原子を有する物質、特に水を低減することとする。

【解決手段】高密度な酸化窒化シリコン膜は水を含む雰囲気下であっても水の侵入を防ぐ効果が高く、膨潤が少ないことが明らかとなった。そこで高密度な酸化窒化シリコン膜を保護膜として設け、酸化物半導体を用いた半導体装置への水の侵入を防ぐ。具体的には、密度が2.32g/cm3以上、またはプレッシャークッカー試験前後において膨潤率が4体積%以下、またはフーリエ変換型赤外分光法によるスペクトルのピーク(極大吸収波数)が1056cm−1以上に現れる、酸化窒化シリコン膜を保護膜として用いる。

(もっと読む)

酸化物薄膜用スパッタリングターゲットおよびその製造法

【課題】スパッタリング法を用いた酸化物半導体膜の成膜時の異常放電の発生が抑制され、連続して安定な成膜が可能なスパッタリングターゲットを提供すること。希土類酸化物C型の結晶構造を持つ、表面にホワイトスポット(スパッタリングターゲット表面上に生じる凹凸などの外観不良)がないスパッタリングターゲット用の酸化物を提供すること。

【解決手段】ビックスバイト構造を有し、酸化インジウム、酸化ガリウム、酸化亜鉛を含有する酸化物焼結体であって、インジウム(In) 、ガリウム(Ga)および亜鉛(Zn)の組成量が原子比で以下の式を満たす組成範囲にある焼結体を提供する。

In/(In+Ga+Zn)<0.75

(もっと読む)

21 - 40 / 2,878

[ Back to top ]