Fターム[5F110GG13]の内容

Fターム[5F110GG13]に分類される特許

81 - 100 / 3,760

液晶表示装置の製造方法

【課題】本発明は、製造工程を単純化して透明導電膜上に金属膜が積層された積層構造を有する共通電極配線を製造することができる液晶表示装置の製造方法を提供する。

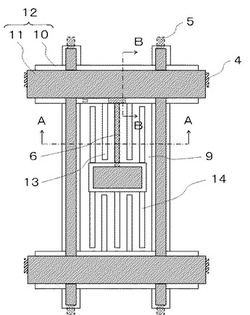

【解決手段】液晶表示装置の製造方法であって、透明導電膜10上に金属膜11が積層された積層構造を有する枠状の共通電極配線12と、透明導電膜10の配線幅よりも小さい配線幅を有する共通電極13と、共通電極配線12の透明導電膜10の配線幅よりも小さい配線幅を有する画素電極14とからなる横電界方式において、感光性樹脂膜15をエッチングマスクにして等方性エッチングにより、共通電極13および画素電極14となる透明導電膜10上に積層された、感光性樹脂膜15の下側に位置する金属膜11を除去するとともに、共通電極配線12となる透明導電膜上10に積層された、感光性樹脂15の下側に位置する金属膜11の側面の一部を除去する工程を含む。

(もっと読む)

薄膜トランジスタ、画像表示装置

【課題】酸化物半導体層のバックチャネル部を半導体層成膜後の薄膜トランジスタ作製工程によるダメージから保護し、良好なトランジスタ特性を得ると共に、薄膜トランジスタ作製の工程数を削減することである。

【解決手段】基板1と、基板1上に設けられたゲート電極2と、基板1上に設けられ、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上に設けられ、アモルファス酸化物からなる半導体層4と、半導体層4上に設けられた保護膜5と、ゲート絶縁膜3上に設けられたソース電極6、及びドレイン電極7と、を備え、保護膜5を、金属材料の化成処理、又は陽極酸化によって形成する。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

スパッタリングターゲット

【課題】高密度かつ低抵抗のスパッタリングターゲット、電界効果移動度の高い薄膜トランジスタを提供する。

【解決手段】Gaをドープした酸化インジウム、又はAlをドープした酸化インジウムを含み、正4価の原子価を示す金属を、Gaとインジウムの合計又はAlとインジウムの合計に対して100原子ppm超1100原子ppm以下含み、結晶構造が、実質的に酸化インジウムのビックスバイト構造からなる焼結体を含むスパッタリングターゲット。

(もっと読む)

半導体装置、薄膜トランジスタ基板および表示装置

【課題】金属酸化物を用いた絶縁膜を低温プロセスで結晶化することが可能で、これによりガラス基板やプラスチック基板上に特性の向上が図られた素子を設けることが可能な半導体装置を提供する。

【解決手段】基板上に、金属酸化物を用いた絶縁膜と半導体薄膜とが積層形成された半導体装置であって、絶縁膜はゲート絶縁膜として用いられ、ゲート絶縁膜に接する側にゲート電極が積層形成され、絶縁膜および半導体薄膜は結晶化され、かつ、ゲート電極と重なる部分の結晶性が他の部分の結晶性よりも高いものである。

(もっと読む)

酸化物半導体、これを含む薄膜トランジスタ、及び薄膜トランジスタ表示板

【課題】理論的根拠に基づいて酸化物半導体の母材料に添加される物質を使用することによって、優れた特性を有する酸化物半導体、これを含む薄膜トランジスタ、及び薄膜トランジスタ表示板を提供する。

【解決手段】 本発明の一実施形態に係る酸化物半導体は、亜鉛(Zn)及び錫(Sn)のうちの少なくとも一つの元素を含む第1物質、及び前記第1物質に添加される第2物質を含み、前記第1物質と酸素(O)との電気陰性度差値から前記第2物質と酸素(O)との電気陰性度差値を引いた値が1.3以下であることを特徴とする。

(もっと読む)

スパッタリングターゲット、トランジスタ、焼結体の製造方法、トランジスタの製造方法、電子部品または電気機器、液晶表示素子、有機ELディスプレイ用パネル、太陽電池、半導体素子および発光ダイオード素子

【課題】WS2を主成分とするスパッタリングターゲットを提供する。

【解決手段】本発明の一態様は、Hf,Re,Ta,W,Nb,Zr,V,Al,In,Sn,Ga,Zn,Si,Ge,Mn,Ni,Fe,Co,Cu,Ag,Y,Sc,Mg,Caからなる群から選ばれた少なくとも一種類以上の元素を合計で0.1〜10.0wt%含有し、残部がWS2および不可避的不純物からなることを特徴とするスパッタリングターゲットである。

(もっと読む)

表示装置及び表示装置の作製方法

【課題】TFTの特性ばらつきに起因する、画素間における発光素子の輝度のばらつきを低減し、信頼性が高く、画質の優れた表示装置を提供することを目的とする。

【解決手段】発光素子に接続するTFTを複数個、少なくとも2つ設け、それぞれのTFTの活性層を形成する半導体領域の結晶性を異ならせるものである。

当該半導体領域は、非晶質半導体膜をレーザーアニールにより結晶化させたものが適用されるが、結晶性を異ならせるために、連続発振レーザービームの走査方向を変えて、結晶成長の方向を互いに異ならせる方法を適用する。或いは、連続発振レーザービームの走査方向は同じとしても、個々の半導体領域間でTFTのチャネル長方向を変えて、結晶の成長方向と電流の流れる方向を異ならせる方法を適用する。

(もっと読む)

積層配線、該積層配線を用いた半導体装置及びその製造方法

【課題】マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制して、マイクロクリスタルシリコン薄膜の膜剥れを防止する。

【解決手段】半導体装置20の配線として備えられ、マイクロクリスタルシリコン薄膜8と該薄膜上に形成された金属薄膜9とから成る積層配線であって、マイクロクリスタルシリコン薄膜8の結晶組織を構成している結晶粒には、半導体装置の製造時の熱処理で生じた金属薄膜9とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である柱状の結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6%以上15%以下となるように形成されている。

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】チャネル領域にシリコンを含まない材料を用いる半導体装置であって、微細化に伴いゲート絶縁層が薄膜化されても、ゲートリーク電流が抑制された半導体装置を提供する。

【解決手段】ゲート絶縁層として熱酸化シリコン層を用いる。熱酸化シリコン層を用いることで、CVD法やスパッタリング法で形成された酸化シリコン層を用いる場合よりゲートリーク電流を抑制することができる。ゲート絶縁層に熱酸化シリコン層を用いるために、チャネル領域を含む半導体層を形成する基板とは別にシリコン基板を用意し、シリコン基板上に熱酸化シリコン層を形成する。そして熱酸化シリコン層を、チャネル領域を含む半導体層に貼り合わる。このようにして、半導体層の上に熱酸化シリコン層を形成し、熱酸化シリコン層をゲート絶縁層として用いたトランジスタを形成する。

(もっと読む)

半導体装置

【課題】液晶の配向不良を抑制するために画素電極を平坦化し、開口率を下げずに十分な

容量を得られる容量素子を有する半導体装置を実現することを課題とする。

【解決手段】薄膜トランジスタ上の遮光膜、前記遮光膜上の容量絶縁膜、前記容量絶縁膜

上に導電層、前記導電層と電気的に接続するように画素電極を有する半導体装置であり、

前記遮光膜、前記容量絶縁膜および前記導電層から保持容量素子を形成することにより、

容量素子として機能する領域の面積を増やすことができる。

(もっと読む)

半導体装置

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電気特性の安定した半導体装置を提供する。とくに、酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜と接して形成されたソース電極、及びドレイン電極と、を有し、ゲート絶縁膜は、少なくとも酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された酸素放出型の酸化膜と、により構成され、酸素放出型の酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、より安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたソース電極およびドレイン電極と、保護膜と、を有し、該保護膜は金属酸化膜を有し、該金属酸化膜は、膜密度が3.2g/cm3以上である。

(もっと読む)

薄膜デバイスおよびその製造方法

【課題】酸化物半導体をチャネルに用いた薄膜デバイスおよびその製造方法において、PETやPES等の樹脂基板上でも自己整合型トップゲート構造の作製を可能にする。

【解決手段】IGZO膜2によりチャネル膜を作製するTFTの製造方法であり、IGZO膜2とゲート電極膜4との間に、ゲート絶縁膜3として機能する有機膜をスピンコート等の塗布法を用いて作製し(図1(b))、その後、IGZO膜2と、外部に導出されたソース・ドレイン電極膜7との間に、絶縁膜として機能する層間膜5をスパッタリング法を用いて作製する(図1(c)、(d))。

(もっと読む)

表示装置

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】表示部に複数の画素を有し、複数のフレーム期間で表示を行う液晶表示装置であって、フレーム期間は、書き込み期間及び保持期間を有し、書き込み期間において、複数の画素のそれぞれに、画像信号を入力した後、保持期間において、複数の画素が有するトランジスタをオフ状態にして、少なくとも30秒間、画像信号を保持させる。画素は、酸化物半導体層でなる半導体層を具備し、酸化物半導体層は、キャリア濃度が1×1014/cm3未満である。

(もっと読む)

81 - 100 / 3,760

[ Back to top ]