Fターム[5F110GG23]の内容

Fターム[5F110GG23]に分類される特許

41 - 60 / 486

発光装置

【課題】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、トランジスタのばらつきを低減する。

【解決手段】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、駆動用トランジスタのチャネル幅をチャネル長よりも小さくする。その際、ゲート配線と平行にアノード側電源線を設けて、フルカラー表示を行う。

(もっと読む)

半導体回路および論理回路

【課題】論理回路をできるだけ小さな回路面積で形成可能な半導体回路を提供する。

【解決手段】半導体回路は、第1および第2のトランジスタで共有されるゲート領域と、ゲート領域に接するように配置されるゲート絶縁膜と、ゲート絶縁膜に接するように配置される半導体層と、を備える。半導体層は、ゲート領域に対向するように配置され、第1のトランジスタのチャネルとして用いられる反転層形成領域と、反転層形成領域に沿って、あるいは反転層形成領域と交差するように形成され、第2のトランジスタのチャネルとして用いられる導通路形成領域と、を有する。導通路形成領域は、ゲート領域が所定の電圧範囲のときには、反転層形成領域から伸びる空乏層により遮断される。

(もっと読む)

液晶表示装置、電子機器

【課題】IPSにおける従来の技術は、工程数が多く、開口率が低いので、実用化できな

い。また、液晶層に最も近接している層に存在する配線及び電極が多く、画素表示部にお

ける個々の液晶にかかる電界が不均一であった。

【解決手段】本発明は、ゲイト線102、105とコモン線103、104を最初に同時

に形成し、層間膜形成後、画素電極108とコモン電極110、111とソ─ス線106

、107を同時に形成する。こうすることによって、電極パタ─ンを単純化でき、工程を

簡略化した。また、液晶層に最も近接している層に存在する配線及び電極を画素電極とコ

モン電極とソ─ス線とし、その形状を単純なものにした。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

EL表示装置

【課題】開口率の高い表示装置又は素子の面積の大きい半導体装置を提供することを課題

とする。

【解決手段】隣接する画素電極(又は素子の電極)の間に設けられた配線との下方にマル

チゲート構造のTFTのチャネル形成領域を設ける。そして、複数のチャネル形成領域の

チャネル幅の方向を前記画素電極の形状における長尺方向と平行な方向とする。また、チ

ャネル幅の長さをチャネル長の長さよりも長くすることでチャネル形成領域の面積を大き

くする。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

電子装置およびその製造方法

【課題】グラフェンシートを使い、大電流をオンオフできる電子装置を提供する。

【解決手段】電子装置は基板と、前記基板上にゲート絶縁膜を介して形成されたグラフェンシートと、前記グラフェンシートの一端に形成されたソース電極と、前記グラフェンシートの他端に形成されたドレイン電極と、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極の間において、前記ソース電極からドレイン電極へのキャリアの流れを横切って形成された、複数の開口部よりなる開口部列と、を備え、前記各々の開口部では前記グラフェンシートから4個以上の炭素原子が除去されており、前記各々の開口部は、他の炭素原子に結合していない結合手を有する炭素原子を二個以上含む少なくとも5個の炭素原子からなるジグザグ形状の端部により画成されている。

(もっと読む)

縦型電界効果トランジスタとその製造方法及び電子機器

【課題】縦型電界効果トランジスタとその製造方法及び電子機器において、基材の材料の選択の幅を広げること。

【解決手段】基材1と、基材1の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極2と、基材1の上に形成され、第1の電極2に重なる開口12を備えた第1の絶縁膜3と、開口12の横の第1の絶縁膜3の上に形成されたゲート電極6と、第1の絶縁膜3の上に形成され、開口12を備えた第2の絶縁膜8と、開口12の横の第2の絶縁膜8の上に形成され、ソース電極とドレイン電極のうちの他方となる第2の電極10と、開口12の側面に形成されたゲート絶縁膜16と、第1の電極2、第2の電極10、及びゲート絶縁膜16上に形成され、酸化物半導体を材料とするチャネル17とを有する縦型電界効果トランジスタによる。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】オフ電流の極めて小さい半導体装置を提供する。また、該半導体装置を適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上にゲート電極を有し、ゲート電極上にゲート絶縁層を有し、ゲート絶縁層上に酸化物半導体層を有し、酸化物半導体層上にソース電極及びドレイン電極を有し、酸化物半導体層の外縁のうちソース電極の外縁からドレイン電極の外縁に達する部分の長さを、チャネル長の3倍以上、好ましくは5倍以上とする。また、熱処理により、ゲート絶縁層から酸化物半導体層へ酸素を供給する。また、酸化物半導体層を選択的にエッチングした後、絶縁層を成膜する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】基板上に第1の酸化絶縁膜を形成し、該第1の酸化絶縁膜上に第1の酸化物半導体膜を形成した後、加熱処理を行い、第1の酸化物半導体膜に含まれる水素を脱離させつつ、第1の酸化絶縁膜に含まれる酸素の一部を第1の酸化物半導体膜に拡散させ、水素濃度及び酸素欠陥を低減させた第2の酸化物半導体膜を形成する。次に、第2の酸化物半導体膜を選択的にエッチングして、第3の酸化物半導体膜を形成した後、第2の酸化絶縁膜を形成して、当該第2の酸化絶縁膜を選択的にエッチングして、第3の酸化物半導体膜の端部を覆う保護膜を形成する。この後、第3の酸化物半導体膜及び保護膜上に一対の電極、ゲート絶縁膜、及びゲート電極を形成する。

(もっと読む)

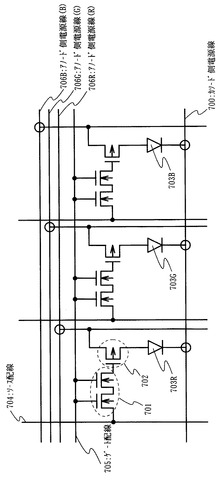

発光装置およびモジュール

【課題】開口部をシンプルにしてシュリンクの問題を解決する。

【解決手段】駆動トランジスタと、スイッチングトランジスタと、消去用トランジスタと、を画素内に有する3トランジスタ型の発光装置の場合において、スイッチング用TFT5505と消去用TFT5506の2つのTFTを、第1のゲート信号線5502と第2のゲート信号線5503の間に配置する。このように配置することで開口率を上げ、開口部もシンプルな形状にすることが出来る。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製

方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を

有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけら

れた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとし

て機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向

に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向

と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面

を有するディスプレイを実現するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体装置

【課題】従来に比してオン電圧性能に優れた横型IGBT、および順方向電圧特性に優れた横型FWDを同一基板上に構成可能とする半導体装置を提供する。

【解決手段】半導体基板上において、横型IGBTと、横型FWDとが、絶縁体であるトレンチ絶縁仕切り部を挟むように横方向に隣接配置されて成る半導体装置であって、横型IGBTは、平面視した場合に、エミッタ領域と当該横型IGBTのドリフト領域との境界面の幅がコレクタ領域と当該横型IGBTのドリフト領域との境界面の幅より狭くなるよう形成されており、横型FWDは、平面視した場合に、カソード領域と当該横型FWDのドリフト領域との境界面の幅がアノード領域と当該横型FWDのドリフト領域との境界面の幅より狭くなるよう形成されていることを特徴とする、半導体装置。

(もっと読む)

グラフェン電子素子

【課題】グラフェン電子素子を提供する。

【解決手段】ゲート電極、ゲート電極上に配置されたゲート酸化物、ゲート酸化物上のグラフェンチャネル層、グラフェンチャネル層の両端にそれぞれ配置されたソース電極及びドレイン電極を備えるグラフェン電子素子。グラフェンチャネル層には、複数のナノホールがグラフェンチャネル層の幅方向に一つの列で形成される。更にグラフェンチャネル層には、複数のナノホールがグラフェンチャネル層の長手方向に実質的に直交して配置される。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するためのフォトリソグラフィ工程及びエッチング工程を省略し、ゲート電極(同一層で形成される配線等を含む)を形成する工程、ソース電極及びドレイン電極(同一層で形成される配線等含む)を形成する工程、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線等を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。コンタクトホールを形成する工程において、半導体層が除去された溝部を形成することで、寄生チャネルの形成を防ぐ。

(もっと読む)

発光装置

【課題】開口部をシンプルにしてシュリンクの問題を解決する。

【解決手段】駆動トランジスタと、スイッチングトランジスタと、消去用トランジスタと

、を画素内に有する3トランジスタ型の発光装置の場合において、スイッチング用TFT

5505と消去用TFT5506の2つのTFTを、第1のゲート信号線5502と第2

のゲート信号線5503の間に配置する。このように配置することで開口率を上げ、開口

部もシンプルな形状にすることが出来る。

(もっと読む)

薄膜トランジスタおよび画像表示装置

【課題】ホールの多数発生を抑制し、かつリーク電流の増大を抑制することができる薄膜トランジスタを提供する。

【解決手段】本発明に係る薄膜トランジスタでは、半導体層12は、平面視において、ゲート電極2の端辺部2A,2Bからソース電極7およびドレイン電極8が引き出された部分において、ゲート電極2から外側に延在する延在部P1,P2,P3を有している。また、平面視において、ソース電極7とゲート電極2の端辺部2A,2Bとが交差する部分L1,L2は、チャネル形成領域13に接するソース電極7の部分LSと、チャネル長方向Yにおいて重ならない。さらに、平面視において、ドレイン電極8とゲート電極2の端辺部2Bとが交差する部分L3は、チャネル形成領域13に接するドレイン電極8の部分LDと、チャネル長方向Yにおいて重ならない。

(もっと読む)

41 - 60 / 486

[ Back to top ]