Fターム[5F110GG23]の内容

Fターム[5F110GG23]に分類される特許

161 - 180 / 486

半導体装置及びその製造方法

【課題】SOI基板に形成されたMOSトランジスタを備えた半導体装置において、ソース領域及びドレイン領域におけるPN接合領域を低減する。

【解決手段】PMOSトランジスタにおいて、LOCOS酸化膜7のバーズビーク下のシリコン層であってゲート電極17から所定範囲内に位置する第1バーズビーク下シリコン層21はチャネル領域と同じ導電型で形成されている。LOCOS酸化膜7のバーズビーク下のシリコン層であってソース領域9及びドレイン領域11と接し、かつ第1バーズビーク下シリコン層21を除く位置の第2バーズビーク下シリコン層5はソース領域9及びドレイン領域11と同じ導電型でソース領域9及びドレイン領域11よりも薄い不純物濃度で形成されている。

(もっと読む)

SOI基板の作製方法

【課題】レーザー光を照射することにより単結晶半導体層の結晶性を回復させる場合であっても、レーザー光の照射時に酸素が取り込まれるのを抑制し、レーザー光の照射前後において、単結晶半導体層に含まれる酸素濃度を同等又は低減することを目的の一とする。

【解決手段】貼り合わせによりベース基板上に設けられた単結晶半導体層にレーザー光を照射して当該単結晶半導体層の結晶性を回復(再単結晶化)させる工程を有し、レーザー光の照射を還元性雰囲気下または不活性雰囲気下で行う。

(もっと読む)

MIS積層構造体の作製方法およびMIS積層構造体

【課題】コスト低減の図れるスイッチング素子の基本構造であるMIS積層構造体およびそれらの作製方法を提供する。

【解決手段】支持基板上に、少なくとも半導体材料層〔S〕、絶縁材料層〔I〕、および導電性酸化物材料層〔M〕(照射するレーザ光を吸収し、薄膜の少なくとも一部がアモルファス相である導電性酸化物材料層)を順次成膜してMIS積層構成体を形成する成膜工程(a)と、集光した状態のレーザ光を前記導電性酸化物材料層側から照射して該導電性酸化物材料層の一部を熱変化させると共に、MIS積層構成体内部に伝播した熱により前記半導体材料層の一部を熱変化させる熱処理工程(b)と、前記MIS積層構成体の熱変化していない部分をエッチング処理で除去するエッチング処理工程(c)とによりMIS積層構造体を作製し、これに電極を設けてスイッチング素子とする。

(もっと読む)

有機ELディスプレイ

【課題】駆動TFTの線形領域における動作を広範囲で行うことが可能な有機ELパネルを提供する。

【解決手段】薄膜トランジスタのチャネル領域が、チャネル幅を一定として、薄膜トランジスタを結晶化する結晶粒形の長手方向及びそれに交差する方向のいずれにも形成されている。発光色の異なる副画素13R、13G、13Bにおける結晶粒形の長手方向のチャネル長Lhと、それに交差する方向のチャネル長LVの和L(L=Lh+Lv)は等しく、Lh/LVが異なっている。

(もっと読む)

再構成可能な半導体デバイス

【課題】 再構成可能な半導体デバイスを提供する。

【解決手段】 再構成可能な半導体デバイスが開示されている。半導体デバイスは、基板と、基板上に形成された第1の絶縁材料と、異なる極性を有する2つのチャネルと、絶縁材料上に形成され、かつ対向する端部で、これらのチャネルに、共通に結合された複数のターミナル電極と、ターミナル電極に形成された第2の絶縁材料と、第2の絶縁材料上に形成された少なくとも1つのコントロールゲートとを含む。チャネルは、異なる極性を有し、電荷蓄積層は、第2の絶縁材料内側に形成されている。コントロールゲートに、フォワードバイアスまたはリバースバイアスが印加され、次にバイアスが切断される。半導体デバイスの電圧−電流特性は、電荷蓄積層に生成された電荷に従って変化する。

(もっと読む)

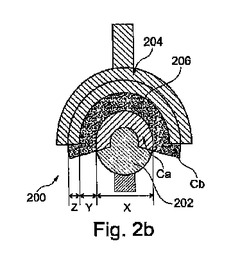

ボディ・タイの領域に効果的に直接コンタクトを設けるプロセスフロー

【課題】直接ボディ・タイ・コンタクトを備えた浅いトレンチ絶縁(STI)デバイスを製造するプロセスフローを提供する。

【解決手段】プロセスフローは、ボディ・タイ・コンタクト222が、ボディ・タイ204まで直接、ナイトライド層210およびSTI酸化物層206を通してエッチングされるエッチングステップの一つを除いて、標準的なSTI製造方法と同様である。このプロセスフローは、浮遊ボディ効果を緩和するように直接ボディ・タイ・コンタクト222を提供するが、臨界的なアライメント要求ならびにレイアウトの臨界的な寸法制御なしで、非直接ボディ・タイ・コンタクトに共通のヒステリシスおよび過渡アップセット効果をも除去する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】 真性酸化亜鉛からなる半導体薄膜を有する薄膜トランジスタの製造に際し、加工精度を良くする。

【解決手段】 まず、真性酸化亜鉛からなる半導体薄膜8の上面全体に保護膜9を形成し、その上に上層絶縁膜12を成膜する。次に、上層絶縁膜12および保護膜9にコンタクトホール10、11を形成する。この場合、チャネル長Lは2つのコンタクトホール10、11間の間隔により決定され、チャネル幅Wはコンタクトホール10、11の所定方向の寸法により決定される。これにより、半導体薄膜8にサイドエッチングがやや生じても、チャネル長Lおよびチャネル幅Wに寸法変化が生じることはない。

(もっと読む)

ゲイン変化補償を伴うトランジスタ

半導体装置(10)およびこれを製造方法は、活性素子領域(12)および隔離領域(14)を提供する工程を含み、隔離領域は、活性素子領域との境界(32)を形成する。パターン化ゲート材料(16)は、境界の第1部分(34)と第2(36)部分との間において、活性素子領域と重なる。パターン化ゲート材料は、活性素子領域内において、チャネルを画定し、ゲート材料は、境界領域の第1部分および第2部分の付近において、境界の第1部分と第2部分との間よりも大きい(24+26,28+30)、ゲート材料の主要寸法に沿って中心線(18)と直交するゲート長さ寸法を有する。チャネルは、境界の第1部分に隣接する第1端と、境界の第2部分に隣接する第2端とを含み、更に、チャネルの両端においてテーパが付けられたゲート長さ寸法によって特徴付けられる。  (もっと読む)

(もっと読む)

アクティブマトリクスOLEDディスプレイおよびその駆動回路

ディスプレイが、それぞれが関連画素駆動回路をもつ複数の有機発光ダイオード(OLED)画素と、複数の選択線と、複数のデータ線とを有する。画素駆動回路のそれぞれは、選択線およびデータ線に結合される。画素駆動回路は、OLEDを駆動するように構成された駆動トランジスタを含むとともに、選択線に結合された第1の端子と、データ線に結合された第2の端子とを有する選択トランジスタを含み、選択トランジスタの端子の一方は、選択トランジスタのゲート接続を備え、端子の他方は、選択トランジスタのドレイン接続およびソース接続の一方を備え、選択トランジスタは、ソース領域と、ドレイン領域と、ゲート領域とを備え、ゲート領域は、ソース領域およびドレイン領域に少なくとも部分的に重なり、ゲート接続と、ドレイン接続およびソース接続の一方との間の静電容量が、ゲート接続と、接続の他方との間の静電容量よりも小さくなるように、ゲート領域の、ソース領域およびドレイン領域の一方との重なりの面積が、領域の他方との重なりの面積よりも大きくなっている。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 特性のばらつきを抑制した半導体素子を備える半導体装置を製造するための製造方法を提供する。

【解決手段】本発明による半導体装置の製造方法は、半導体層(Se)の第1領域(Sa)と第2領域(Sb)との間の少なくとも一部にスリット(SL)を形成する工程と、第1開口部(Oa)および第2開口部(Ob)の設けられたマスク層(M)を形成する工程と、半導体層(Se)の第1領域(Sa)および第2領域(Sb)に触媒元素(Ct)を導入し、半導体層(Se)の第1領域(Sa)および第2領域(Sb)のそれぞれの結晶化を行う工程と、半導体層(Se)の第1領域(Sa)および第2領域(Sb)をパターニングした第1島状半導体層(122)および第2島状半導体層(142)を用いて半導体素子(120)および半導体素子(140)を作製する工程と包含する。

(もっと読む)

薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置

【課題】薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置を提供する。

【解決手段】基板と、前記基板上に位置し、結晶化誘起金属を用いて結晶化された多結晶シリコン層からなり、ソース/ドレイン領域及びチャネル領域を含む半導体層と、前記半導体層上に位置するゲート絶縁膜と、前記ゲート絶縁膜上に位置するゲート電極と、前記ゲート電極上に位置する層間絶縁膜と、前記層間絶縁膜上に位置し、前記半導体層のソース/ドレイン領域と電気的に接続されるソース/ドレイン電極を含み、前記半導体層は前記半導体層の両端部に位置する第1ゲッタリングサイト及び前記第1ゲッタリングサイトと離隔されて位置する第2ゲッタリングサイトを含むことを特徴とする薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置を提供する。

(もっと読む)

バルク基板上に形成されたダブルゲート及びトライゲートトランジスタ及びそのトランジスタを形成するための方法

【解決手段】

FinFETS及びトライゲートトランジスタのような三次元トランジスタ構造が、強化されたマスキング形態によって形成することができ、それによりバルク半導体材質内での自己整合手法によるドレイン及びソース区域(211D,211S)、フィン(210)並びに分離構造(208A)の形成が可能になる。基本フィン構造(210)を画定した後、プレーナトランジスタ構造の高度に効率的な製造技術を用いることができ、それにより三次元トランジスタ構造の総合的な性能を更に高めることができる。

(もっと読む)

表示装置及びその製造方法

【課題】表示品位、製造効率及び製造コストが良好な表示装置及びその製造方法を提供する。

【解決手段】表示装置は、薄膜トランジスタ24のチャネル保護膜34において、半導体膜及びチャネル保護膜34上に形成されたn+半導体膜と、n+半導体膜を介しチャネル保護膜34に跨って互いに離間して形成されたソース電極27及びドレイン電極28のそれぞれの下方領域との間に位置する端部に、平面視で鋭角の突起部35が形成されている。

(もっと読む)

有機トランジスタアレイ及び表示装置

【課題】 プロセスステップを増加させず、かつ現状の印刷プロセスで製造可能な集積度の高い有機トランジスタアレイ、及び、前記有機トランジスタアレイを有する表示装置を提供することを目的とする。

【解決手段】 基板上に設けられた複数のゲート電極と、前記複数のゲート電極の上層又は下層にゲート絶縁膜を介して設けられた複数のソース電極及び複数のドレイン電極と、前記ゲート絶縁膜を介して前記ゲート電極に対向して配置され、前記ソース電極と前記ドレイン電極との間にチャネル領域を形成する有機半導体層と、を有する有機トランジスタアレイであって、前記有機トランジスタアレイは、平面視において、単一画素を構成する複数の区画に区分され、前記区画は、最密充填構造を有することを特徴とする。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】薄型軽量画像表示装置や、フレキシブル電子装置を構成するTFT回路の、TFTの配置をより稠密に行う。更には、小さい製造工程数により製造コストを低減する。

【解決手段】塗布法、滴下法、印刷法で、TFTの第1層目の電極のパターニングを行った後、基板の裏面からの露光を利用した自己整合技術により、第2層目の電極の位置合わせを、第1層目の電極に整合させて、塗布法、滴下法、印刷法で第2層目の電極を形成する。この際、第2層目の電極の配置を、前記の露光工程において、第1層目の電極の形状の投影像を遮光マスク用いて分離状態を実現する。例えば、TFTが並置される場合は、各電極の透光性基板の主面への投影像の関係が、第2層目の電極の配置が第1層目の電極に囲まれる形態か、第2層目の電極の配置より、分離するための第1層目の電極の一部が突き出す形態をとる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート長が膜厚で規定された縦型の半導体装置であって、良好な信頼性のゲート絶縁膜を備え、微細化が容易な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置10の基板11上の、チャネル領域32に対応する領域を

除いた領域を種結晶領域として用い、チャネル領域32を迂回する形で、

基板11上に選択エピタキシャル成長又は固相エピタキシャル成長によってゲートとなる単結晶膜を結晶成長させる。この単結晶膜をCMPで窒化膜19の膜厚に規定し、この単結晶膜と絶縁膜からなる積層膜に、チャネルとなる任意の大きさの開口を形成する。この開口形成時にできた、単結晶膜の端面を酸化させることによりゲート酸化膜を形成する。

(もっと読む)

表示装置およびその製造方法

【課題】製造工程の増大をもたらすことなく、所望のチャネル幅を得る製造方法を提供する。

【解決手段】ボトムゲート型の薄膜トランジスタを備える表示装置の製造方法であって、半導体層および金属層を順次形成する工程と、前記金属層上に形成されたフォトレジスト膜を、ハーフ露光を用いて、ドレイン電極DTおよびソース電極STの形成領域において膜厚を大きく、外側にはみ出る領域において膜厚を小さくして残存させる工程と、前記フォトレジスト膜をマスクとして前記金属層および半導体層を順次エッチングする工程と、アッシングを用いて、前記フォトレジスト膜のうち膜厚の小さいフォトレジスト膜を除去し、前記ドレイン電極およびソース電極の形成領域上のフォトレジスト膜を残存させる工程と、前記ドレイン電極およびソース電極の形成領域上のフォトレジスト膜をマスクとして前記金属層をエッチングする工程と、を備える。

(もっと読む)

薄膜トランジスタ

【課題】本発明は、薄膜トランジスタに関する。

【解決手段】本発明の薄膜トランジスタは、ソース電極と、前記ソース電極と分離して設置されるドレイン電極と、前記ソース電極及び前記ドレイン電極に電気的に接続される半導体層と、絶縁層と、前記絶縁層により、前記半導体層と、前記ソース電極及び前記ドレイン電極と絶縁状態で設置されるゲート電極と、を含む。前記半導体層が積層された少なくとも二枚のカーボンナノチューブフィルムを含み、前記隣接するカーボンナノチューブフィルムにおけるカーボンナノチューブが、端と端で接続され、同じ方向に沿って配列されていることを特徴とする薄膜トランジスタ。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】 簡便に形成可能であり、リーク電流の発生を抑制できる薄膜トランジスタ及び薄膜トランジスタの製造方法を提供する。

【解決手段】 薄膜トランジスタ22は、ソース領域及びドレイン領域の一方である第1領域と、他方である第2領域と、を有した半導体層25と、ゲート絶縁層27と、ゲート絶縁層上に形成され、第1領域から外れて位置し、第2領域に重ねられた開口部30aを有した環状のゲート電極30と、層間絶縁膜31と、半導体層の第1領域に接続された第1電極と、半導体層の第2領域に接続された第2電極と、を備えている。

(もっと読む)

薄膜トランジスタ

【課題】本発明は、薄膜トランジスタに関する。

【解決手段】本発明の薄膜トランジスタは、ソース電極と、前記ソース電極と分離して設置されるドレイン電極と、前記ソース電極及び前記ドレイン電極に電気的に接続される半導体層と、絶縁層と、前記絶縁層により、前記半導体層と、前記ソース電極及び前記ドレイン電極と絶縁状態で設置されるゲート電極と、を含む。前記半導体層が一枚のカーボンナノチューブフィルムを含み、該カーボンナノチューブフィルムにおけるカーボンナノチューブが端と端で接続され、同じ方向に沿って配列される。

(もっと読む)

161 - 180 / 486

[ Back to top ]