Fターム[5F110GG23]の内容

Fターム[5F110GG23]に分類される特許

81 - 100 / 486

スイッチング素子、高周波信号スイッチ及び高周波信号増幅モジュール

【課題】高周波信号経路を切り替えるために半導体基板上に形成された、小型でかつ低歪特性を実現するスイッチング素子を提供する。

【解決手段】スイッチング素子の一例であるFET100は半導体基板109上に形成された櫛型の2つのソース・ドレイン電極101と、2つのソース・ドレイン電極101の間を這うように配置された少なくとも2本のゲート電極102と、隣り合うゲート電極102の間に挟まれ、かつ、隣り合うゲート電極102に沿って配置された導電層103とを備え、ゲート電極102の2つのソース・ドレイン電極101の指状部と平行な部分である直線部108の直下に位置する層が、ゲート電極102の隣り合う一対の直線部108をつなぐ部分である屈曲部107の直下に位置する層から、電気的に分離されている。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて製造することが可能な電界効果トランジスタを提供する。

【解決手段】ソース領域144及びドレイン領域146並びにチャネル領域142を含む酸化物導電体層140と、チャネル領域142の導通状態を制御するゲート電極120と、ゲート電極120とチャネル領域142との間に形成され強誘電体材料からなるゲート絶縁層130とを備え、チャネル領域142の層厚は、ソース領域144の層厚及びドレイン領域146の層厚よりも薄い電界効果トランジスタ。酸化物導電体層140は、型押し成形技術を用いて形成されている。

(もっと読む)

半導体素子

【課題】垂直に形成されたナノワイヤを構成要素として備える半導体素子の寄生容量増加を抑制し、動作速度時定数が改善される半導体素子を提供する。

【解決手段】導電性基板101の主平面と電極109間の層間絶縁膜を膜厚調整層102と保護絶縁層103の2層化することにより、膜密着性の乏しい低誘電率膜102と電極109を保護絶縁層103で隔てることによってはがれを抑制しながら、主平面101と電極109間を電気的に接続するナノワイヤ107と、導電性基板101と電極109の間の寄生容量を低減する。

(もっと読む)

SOI基板の作製方法

【課題】半導体層が効率良く平坦化されたSOI基板を提供することを課題の一とする。また、当該SOI基板を用いた半導体装置を提供することを課題の一とする。

【解決手段】ボンド基板に加速されたイオンを照射して該ボンド基板に脆化領域を形成し、ボンド基板またはベース基板の表面に絶縁層を形成し、絶縁層を介してボンド基板とベース基板を貼り合わせ、熱処理により、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成し、半導体層の表面と、該半導体層と同じ半導体材料でなる半導体ターゲットとが対向するように配置し、半導体層の表面と半導体ターゲットとに、交互に希ガスイオンを照射することで、半導体層の表面の平坦化を図るSOI基板の作製方法である。

(もっと読む)

トランジスタ

【課題】高い電流駆動力と高いカットオフ特性を備えたトランジスタを提供する。

【解決手段】本発明の一態様に係るトランジスタは、ゲート電極12下にゲート絶縁膜を介して形成され、ソース側端部10Sを含む半導体領域10aとドレイン側端部10Dを含む導体領域10bとを有し、ソース側端部10Sにおけるチャネル幅方向の幅Laがドレイン側端部10Dにおけるチャネル幅方向の幅Lbよりも小さいグラフェン膜10と、グラフェン膜10のソース側端部10Sに接続され、ショットキーバリア接合を形成するソース電極と、グラフェン膜10のドレイン側端部10Dに接続され、オーミック接合を形成するドレイン電極と、を有する。

(もっと読む)

MEMS及びMEMSの製造方法

【課題】回路構成の設計自由度の高いMEMS及びMEMSの製造方法を提供する。

【解決手段】基板10と、基板10の一方の面側に設けられる第1半導体部21と、基板10の一方の面側に設けられる振動子31と、を備えるMEMSにおいて、第1半導体部21の側面側に設けられ、かつ基板表面に対して略垂直な第1面21aと、振動子31の側面側に設けられ、かつ基板表面に平行な方向において第1面21aと対向する第2面31aが設けられると共に、第2面31a側の表層部分は第1面21a側をゲート電極として電圧が印加された際にチャネルとなることで、第1半導体部21における第1面21aを含む部分と振動子31における第2面31aを含む部分とで電界効果トランジスタが構成されることを特徴とする。

(もっと読む)

電界効果トランジスタおよび半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。

(もっと読む)

記憶装置、半導体装置、及び電子機器

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。位相反転素子への電源電圧の印加を停止する場合、データを容量素子に記憶させることで、位相反転素子への電源電圧の供給を停止しても、容量素子においてデータを保持させる。

(もっと読む)

表示装置、スイッチング回路および電界効果トランジスタ

【課題】画素駆動用のスイッチング回路に用いる電界効果トランジスタのOFF電流特性の抑制およびON電流特性の向上を同時に図ることができ、スイッチング回路の高性能化により画質の向上を図ることができる表示装置を提供する。

【解決手段】一つまたは電気的に直列接続された複数の電界効果トランジスタを有するスイッチング回路において、少なくとも一つの電界効果トランジスタのチャネルとなる半導体層15の少なくとも一部の幅をチャネル長方向に連続的に変化させる。例えば、チャネル部における半導体層15のソース側の部分の幅をW50からW51に直線的に減少させ、他の部分は一定の幅W51とする。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

窒化物半導体素子

【課題】ゲート絶縁膜の絶縁破壊を抑制または防止できる構造を有する窒化物半導体素子を提供する。

【解決手段】電界効果トランジスタ1(窒化物半導体素子)は、窒化物半導体の積層構造部3と、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、ガードリング層11とを含む。積層構造部3は、n型GaN層4,5、p型GaN層6およびn型GaN層7を積層して構成されている。ゲート絶縁膜15は、n型GaN層5、p型GaN層6およびn型GaN層7に跨るように、積層構造部3の壁面9に形成されている。ゲート電極16は、ゲート絶縁膜15を挟んでp型GaN層6に対向している。ガードリング層11は、p型GaN層6における壁面9に間隔を開けて対向するようにn型GaN層5上に形成されたp型GaN層からなる。

(もっと読む)

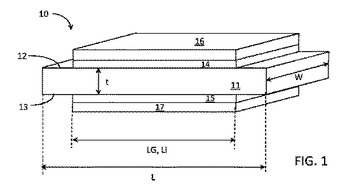

ダブルゲートナノ構造FET

少なくとも1つのナノ構造を備えた電界効果トランジスタ(FET)半導体デバイスであって、少なくとも、2つの主面を有する、均一にドープされたビーム形状のナノ構造と、ナノ構造の各主面に設けられたゲート電極と、ダブルゲートナノ構造ピンチオフFETを形成するための、ナノ構造の各主面とゲート電極との間の絶縁層とを備えたデバイス。FETのピンチオフ電圧及び電流を独立して調整できることが、かかるFETの利点である。  (もっと読む)

(もっと読む)

スパッタリングターゲットおよびその製造方法、並びにトランジスタ

【課題】酸化物半導体膜を成膜する成膜技術を提供することを課題の一とする。

【解決手段】金属酸化物の焼結体を含み、その金属酸化物の焼結体の含有水素濃度が、たとえば、1×1016atoms/cm3未満と低いスパッタリングターゲットを用いて酸化物半導体膜を形成することで、H2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物の含有量が少ない酸化物半導体膜を成膜する。また、この酸化物半導体膜をトランジスタの活性層として適用する。

(もっと読む)

液晶表示装置

【課題】薄膜トランジスタへの外部光の入射を遮光できるとともに、画素の開口率の向上を図った液晶表示装置を提供する。

【解決手段】表示装置の画素領域における薄膜トランジスタTFTはゲート電極GTと前記ゲート電極GTの上方に配置した半導体層ASと、前記半導体層ASの上層に配置したドレイン電極DTおよびソース電極を有し、前記半導体層ASは、ドレイン信号線DLの延在方向においてゲート電極GTの形成領域からはみ出して形成される延在部を有し、前記ゲート電極GTは、ゲート信号線の延在方向において前記半導体形成領域からはみ出して形成されている。

(もっと読む)

単電子ターンスタイルデバイスおよびその製造方法

【課題】より小さな単電子島が作製でき、また、高い精度を必要とせずにトップゲートが配置できるようにする。

【解決手段】形成しようとする細線の延在方向に対して直交して開口部104を挟む2つの箇所に、対向して配置される2つの溝部105を形成する。溝部105は、絶縁層101に到達するまで形成する。次に、酸化シリコン層103を介してシリコン層102の上層部を熱酸化し、シリコン層102をより薄くする。この酸化工程により、開口部104の対向する2つの曲線状の縁部に対応する曲線状の境界部の内側近傍において、層厚方向にくびれるくびれ部107が形成され、くびれ部107においては、シリコン層102の層厚がより薄くなり、層厚方向の量子サイズ効果によりトンネルバリアが形成されるようになる。

(もっと読む)

不均一な半導体装置のアクティブ領域パターン形成方法

【課題】不均一な半導体装置のアクティブ領域パターン形成方法を提供する。

【解決手段】具体例によると、少なくとも3つのアクティブ領域を含む半導体装置が提供される。少なくとも3つのアクティブ領域は隣接する。少なくとも3つのアクティブ領域の縦軸は平行で、少なくとも3つのアクティブ領域は、それぞれ、対応するアクティブ領域の縦軸と交差する辺縁を有する。少なくとも3つのアクティブ領域の辺縁は弧形を形成する。

(もっと読む)

半導体装置

【課題】三次元半導体であるsurrounding gate transistor(SGT)のオン電流を増加させることにより、SGTの高速動作を実現する半導体装置を提供することを課題とする。

【解決手段】ソース、ドレイン及びゲートが、基板上に階層的に配置される半導体素子であって、シリコン柱と、前記シリコン柱の側面を取り囲む絶縁体と、前記絶縁体を囲むゲートと、前記シリコン柱の上部又は下部に配置されるソース領域と、前記シリコン柱の上部又は下部に配置されるドレイン領域であって、前記シリコン柱に対して前記ソース領域と反対側に配置されるドレイン領域とを備え、前記シリコン柱と前記ソース領域との接触面は、前記シリコン柱と前記ドレイン領域との接触面より小さい半導体素子を提供することにより上記課題を解決する。

(もっと読む)

液晶表示装置及び当該液晶表示装置を具備する電子機器

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上を図ることのできる液晶表示装置を提供する。

【解決手段】薄膜トランジスタ106、及び画素電極105を有する複数の画素を有し、画素は、走査線として機能する第1の配線101に電気的に接続されており、薄膜トランジスタは、第1の配線101上にゲート絶縁膜113を介して設けられた酸化物半導体層103を有し、酸化物半導体層103は、第1の配線が設けられた領域をはみ出て設けられており、画素電極105と、酸化物半導体層103とが重畳して設けられる。

(もっと読む)

81 - 100 / 486

[ Back to top ]