Fターム[5F110GG32]の内容

薄膜トランジスタ (412,022) | チャネル半導体層 (67,982) | チャネル領域の不純物 (5,796) | 不純物材料 (2,984)

Fターム[5F110GG32]の下位に属するFターム

キャリアにならない不純物 (905)

Fターム[5F110GG32]に分類される特許

2,061 - 2,079 / 2,079

表示装置および光電変換素子

【課題】 製造コストをかけることなく、十分な光電流を得ることができる表示装置を提供する。

【解決手段】 表示装置は、各画素TFTごとに2個ずつ設けられる画像取込み用のセンサとを有する。センサ内のフォトダイオードD1,D2を構成するp+領域46とn+領域48の間に、低濃度のp-領域47またはn-領域を形成し、このp-領域47またはn-領域の基板水平方向長さをp+領域46やn+領域48よりも長くするため、p+領域46とn+領域48の間に形成される空乏層53がn-領域に長く伸び、その結果、光電流が増えて光電変換効率がよくなるとともに、S/N比が向上する。

(もっと読む)

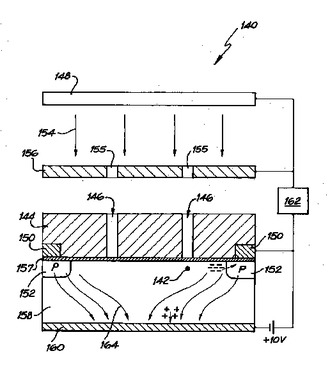

注入され計数されたドーパントイオン

本発明は、実質的に真性な半導体の基板(158)の領域に注入された、計数された数のドーパントイオン(142)を有する汎用タイプの半導体装置に関する。基板(158)の一つ以上のドープされた表面領域は、金属化され、電極(150)が形成される。計数された数のドーパントイオン(142)が、実質的に真性な半導体の領域に注入される。

【その他】

原文には、請求項11及び請求項11Aが存在する。請求項11Aは、オンライン手続上、請求項11内に記載した。

(もっと読む)

(もっと読む)

使い捨てスペーサを隆起ソース/ドレイン処理に取り入れた半導体デバイスの製造方法

半導体形成プロセスでは、ゲート電極(10)を基板(108)の上に形成する。第1シリコン窒化膜スペーサ(122)をゲート電極の側壁に隣接するように形成し、そして次に、使い捨てシリコン窒化膜スペーサ(130)をオフセットスペーサに隣接するように形成する。次に、使い捨てスペーサ(130)の境界によって画定される隆起ソース/ドレイン構造(132)をエピタキシャル成長により形成する。次に、使い捨てスペーサ(130)を除去して、ゲート電極(110)の近位に位置する基板を露出させ、そしてハロイオン注入(140)及びエクステンションイオン注入(142)のようなシャロージャンクションイオン注入を、ゲート電極の近位に位置する露出基板に行なう。取り替えスペーサ(136)を、使い捨てスペーサ(130)が形成されていた領域とほぼ同じ領域に形成し、そしてソース/ドレインイオン注入(140)を行なって、ソース/ドレイン不純物分布を隆起ソース/ドレイン(132)に形成する。ゲート電極(110)は被覆窒化シリコンキャップ層(144)を含むことができ、そして第1シリコン窒化膜スペーサ(122)はキャップ層(144)とコンタクトしてポリシリコンゲート電極(110)を窒化シリコンで取り囲むことができる。  (もっと読む)

(もっと読む)

複合スペーサ絶縁領域幅を備えた集積回路

異なるスペーサ絶縁領域幅を有するPチャネルトランジスタ(823)とNチャネルトランジスタ(821)とを備えた集積回路が開示されている。一実施形態において、Nチャネルトランジスタのスペーサ絶縁領域幅がPチャネルトランジスタのスペーサ絶縁領域幅よりも小さくなるようにPチャネル領域(115)をマスクしている間に、Nチャネルトランジスタの外側壁スペーサ(321)は除去される。また、Pチャネルソース/ドレインシリサイド領域(809)がPチャネルトランジスタのゲート(119)に対して配置されるよりも、Nチャネルトランジスタのドレイン/ソースシリサイド領域(805)はNチャネルトランジスタのゲート(117)に対してより近い位置に配置される。Pチャネルトランジスタのスペーサ絶縁幅をより大きくし、ソース/ドレインシリサイド領域とゲートとの間の距離をより大きくすることにより、Nチャネルトランジスタのチャネル領域の応力に対しPチャネルトランジスタのチャネル領域の相対圧縮応力を増大させた結果、Pチャネルトランジスタの性能が向上する。  (もっと読む)

(もっと読む)

ドープされた部分を有する堆積チャネル領域を含むトランジスタ

ゲート電極(12、60)と、ソース電極(20、62)と、ドレイン電極(22、64)と、誘電体材料(16、70)と、ソース電極(20、62)とドレイン電極(22、64)との間に配置されるチャネル領域(18、80)とを有するトランジスタ(10、40、42、44、46)。チャネル領域(18、80)が、不純物がドープされている部分(82)を含み、これにより、チャネル領域(18、80)の残りの部分に対して、その部分(82)内の固定電荷密度が変えられる。  (もっと読む)

(もっと読む)

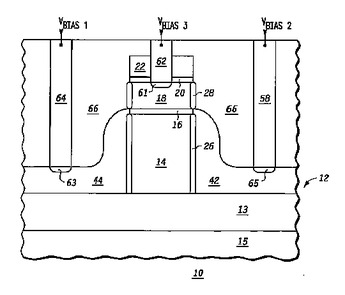

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

フィン型FETを製造する方法

【課題】 結晶学的に完璧に近く、薄いフィンの固有の構造的な弱さを克服した側壁表面を有する極めて薄いフィンを有するフィン型FETを製造する方法を提供する。

【解決手段】 フィン型FET構造体およびフィン型FETデバイスを形成する方法。この方法は、(a)半導体基板(100)を設けるステップと、(b)基板(100)の上面(105)上に誘電体層(110)を形成するステップと、(c)誘電体層(110)の上面(115)上にシリコン・フィン(135)を形成するステップと、(d)フィン(135)の少なくとも1つの側壁(150A)上に保護層(160)を形成するステップと、(e)フィン(135)のチャネル領域(175)において、少なくとも1つの側壁(150A)から保護層(160)を除去するステップと、を含む。第2の実施形態では、保護層(160)は、保護スペーサ(210A)に変換される。

(もっと読む)

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

シリコン薄膜の焼鈍方法およびそれから調製される多結晶シリコン薄膜

後に絶縁層およびシリコン薄膜が形成される基板中のシリコン薄膜の焼鈍方法が開示される。本方法は、基板が処理中に変態しない温度範囲内でシリコン薄膜を加熱または予備加熱して、そこに内因性キャリヤを生成させることにより、抵抗をジュール加熱が可能な値に低下する工程;および予備加熱されたシリコン薄膜に電界を印加して、ジュール加熱をキャリヤの移動によって引き起こすことにより、結晶化を行い、結晶欠陥を排除し、結晶成長を確実にする工程を含む。本方法を用いると、予備加熱条件に従って、a−Si薄膜、a−Si/ポリ−Si薄膜またはポリ−Si薄膜にジュール加熱が選択的に引き起こされ、それによって良好な品質のポリ−Si薄膜が、非常に短時間に、基板を損傷することなく作製される。 (もっと読む)

有機薄膜トランジスタ

【課題】特殊な技術を要せず、簡単な製造方法でキャリア移動度が高い有機薄膜トランジスタを提供すること。

【解決手段】有機半導体層に重量平均分子量2000以上のπ共役系ポリマー及び分子量2000以下のπ共役系オリゴマーを含有することを特徴とする有機薄膜トランジスタ。

(もっと読む)

半導体装置の製造方法

【課題】閾値電圧の絶対値を低く抑えながら、オフリーク電流を低下させることができる半導体装置の製造方法を提供する。

【解決手段】Nチャネル型TFT形成予定領域内のpoly−Si層4にリンを注入することにより、n+領域8を形成した後、Pチャネル型TFT形成予定領域にのみ開口部が存在するレジストマスク9を用いて、ボロンのイオン注入を行うことにより、Pチャネル型TFTのソース・ドレイン領域となるp+領域10を形成する。次に、レジストマスク9を残存させたまま、水素注入を行うことにより、Pチャネル型TFT形成予定領域内において、チャネル領域(poly−Si層4)及びソース・ドレイン領域(p+領域10)の水素化処理を行う。このような方法によれば、Nチャネル型TFTに対する水素化処理が行われないため、Nチャネル型TFTにおける不要な閾値電圧の遷移が防止され、オフリーク電流の上昇を回避することができる。

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

表示装置及びその製造方法

【課題】表示品質と画像取込み性能に優れた表示装置及びその製造方法を提供する。

【解決手段】表示装置の製造工程にてTFT11のチャネル部とフォトダイオードD1,D2のI層をともに水素化する際、TFT11とフォトダイオードD1,D2とで水素化の進行に違いが出るようにして、TFT11のチャネル部の欠陥密度を少なくし、かつフォトダイオードD1,D2のI層の欠陥密度を多くする。これにより、TFT11のリーク電流が抑制され、フォトダイオードD1,D2の光に対する感度を向上できる。

(もっと読む)

D/A変換回路及び半導体装置

【課題】 高いビット数のデジタル信号に対応し、線形性が良く、占有面積の小さいD/A変換回路を提供する。

【解決手段】 複数の容量を有するD/A変換回路であって、複数の容量は、第1電極と、第1電極に接している第1誘電体と、第1誘電体に接している第2電極と、第2電極に接している第2誘電体と、第2誘電体に接している第3電極とをそれぞれ有しており、第2電極は、第1電極及び第3電極と重なっており、第2電極は、第1電極及び第3電極と重なっている部分において開口部を有しており、第2電極が有する開口部において、第1誘電体及び第2誘電体にコンタクトホールが形成されており、コンタクトホールを介して第1電極と第3電極が接続されていることを特徴とするD/A変換回路。

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】 電気特性の優れた多結晶TFTを提供する。

【解決手段】多結晶膜3を堆積させる工程、堆積した多結晶膜のうち所望の位置4のみを残すようにエッチングする工程、残された部分的な多結晶膜の中で所望の結晶方位の結晶粒5だけを、しかも所望の結晶面(ファセット)6を出した状態になるように異方性エッチングする工程、さらに、こうして得られた結晶核の上に膜を堆積し結晶化させる工程を用いる。

(もっと読む)

半導体膜形成方法及び薄膜半導体装置の製造方法

【課題】 本発明の目的は、基板上に高品質な半導体膜を形成するための半導体膜形成方法を提供することにある。

【解決手段】 本発明は、バイアス触媒CVD,高密度バイアス触媒CVD,バイアス減圧CVD,バイアス常圧CVDを利用して、基板に半導体膜を形成する半導体膜形成方法である。真空容器1に原料ガスを供給し、真空容器1中に配置された基板10と電極3aとの間にグロー放電開始電圧以下の電界を印加して、基板10上に、少なくとも錫、ゲルマニウム、鉛のいずれか一つ以上を含有する半導体膜と、絶縁膜と、を形成することを含む工程と、この半導体膜および絶縁膜にレーザーを照射してアニールする工程と、このアニールする工程の後工程であって、水蒸気でアニールを行う工程と、を備える。

(もっと読む)

半導体装置、画像表示装置、半導体装置の製造方法、及び画像表示装置の製造方法

【課題】 CMOS−TFTを構成するp型及びn型TFTの各しきい値電圧を独立に効率良く(最小限のフォトリソグラフィーで)高精度に制御する。

【解決手段】 CMOS−TFTを製造するに際して、しきい値電圧(Vthp ,Vthn )制御として極低濃度にp型不純物(B:ボロン)の非選択的添加(p型及びn型TFTの双方に添加)及び選択的添加(n型TFTのみに添加)を連続的に行なう。具体的には、当初図4(a)のようにId −Vg 特性がp型及びn型TFT共に負シフトした状態から、非選択的添加により図4(b)のようにp型及びn型TFT共に正シフトさせてVthp を先ず仕様値とし、続いて選択的添加によりn型TFTのみ正シフトさせてVthn を仕様値に調整する。

(もっと読む)

電気光学装置及びその製造方法並びに電子機器

【課題】 電気光学装置において、比較的簡単な構成を用いて、画素部のTFTのチャネル領域やチャネル隣接領域における入射光や戻り光に対する遮光性能を高める。

【解決手段】 電気光学装置は、一対の基板間に挟持された電気光学物質層(50)と、TFTアレイ基板(10)にマトリクス状に設けられた画素電極(9a)とを備える。TFT(30)の下側には、第1遮光膜(11a)が設けられている。データ線(6a)は、遮光性の材料からなり、TFTのチャネル領域(1a’)及びチャネル隣接領域(1a”)を対向基板(20)の側から見て夫々覆う主配線部と、この主配線部の縁から層間絶縁膜に形成された溝に向けて伸びておりチャネル隣接領域を側方から囲む側方遮光部(6b)とを有する。

(もっと読む)

2,061 - 2,079 / 2,079

[ Back to top ]