Fターム[5F110HK37]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | 堆積 (8,750) | CVD (2,011) | 減圧CVD (39)

Fターム[5F110HK37]に分類される特許

1 - 20 / 39

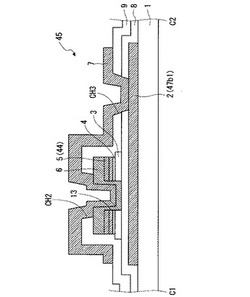

配線構造及びそれを備える薄膜トランジスタアレイ基板並びに表示装置

【課題】透明導電膜上における絶縁膜の膜浮きの発生を抑え、且つ、透明導電膜と金属膜との良好な電気的接続性を得ることができる配線構造を提供する。

【解決手段】それぞれ配線として機能する第1の導電膜2と第2の導電膜5と接続する配線変換部45において、第2の導電膜5の内側には刳り抜き部13が形成される。第2の導電膜5の上に設けられる第2の導電膜5は、第2の導電膜5の上面および刳り抜き部13に露出した端面を覆い、且つ、第2の導電膜5の外周の端面を覆わないように形成される。第1の透明導電膜6の上層の第2の透明導電膜7が、第2の導電膜5と第1の導電膜2とに接続することにより、第1の導電膜2と第2の導電膜5とが電気的に接続される。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】電界効果トランジスタであって、半導体基板10上に垂直に形成され、且つ第1の領域が第2の領域よりも高く形成された半導体フィン31と、第1の領域の両側面にゲート絶縁膜40を介して設けられたゲート電極50と、第2の領域に第1の領域の上端よりも低い位置まで設けられた、合金半導体からなるソース・ドレイン下地層63,73と、下地層63,73上に第1の領域の上部を挟むように設けられた、下地層63,73とは格子定数の異なるソース・ドレイン領域60,70とを備えている。チャネル領域には応力が付与され、下地層63,73は、空乏層が収まる厚さよりも厚く、熱平衡状態で結晶にミスフィット転位が導入される熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に歪みを加える領域内の格子位置に存在する炭素量を多くすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板のうちゲート電極5両側にエクステンション領域7s、7d、ポケット領域8s、8dを形成し、ゲート電極5側面にサイドウォール9を形成し、半導体基板1のうちサイドウォール9、ゲート電極5から露出した領域をエッチングして凹部1s、1dを形成し、凹部1s、1d内に第3不純物を含む半導体層11s,11dを形成し、第1熱処理により第3不純物を活性化してゲート電極5の両側方にソース/ドレイン領域11s,11dを形成し、半導体層11s,11d内に炭素を有する第4不純物をイオン注入して半導体層11s,11dをアモルファス領域13s,13dとなし、第2熱処理によりアモルファス領域13s,13d内結晶の格子位置での炭素の結合性を高めてゲート電極5の両側方に歪発生領域14s,14dを形成する工程を有する。

(もっと読む)

薄膜トランジスタアレイ基板、及び液晶表示装置

【課題】透明導電膜上層に形成される絶縁膜の膜浮きの発生を防止或いは抑制し、歩留り或いは信頼性を向上することの可能な薄膜トランジスタアレイ基板、及び液晶表示装置を得る。

【解決手段】この発明のTFTアレイ基板100においては、TFT51と、ソース電極53及びドレイン電極54、並びにソース電極53及びドレイン電極54と同一材料により同層に形成される金属パターン5の何れかに直接重なり形成される透明導電膜パターン6と、透明導電膜パターン6上を含むゲート絶縁膜8上を覆う上層絶縁膜9を備え、少なくとも額縁領域42に形成される透明導電膜パターン6は、ソース電極53、ドレイン電極54或いは金属パターン5のパターン端面を覆うことなく形成される。

(もっと読む)

半導体装置及びその作製方法

【課題】電極の表面へのエッチングによるダメージを低減する。

【解決手段】第1の導電層を覆って設けられた第1の絶縁層と、第1の絶縁層上に設けられた第1の半導体層と、第1の半導体層上に、第1の半導体層を露出させて離間して設けられた第2の半導体層と、第2の半導体層上に設けられた不純物半導体層と、不純物半導体層上に、少なくとも一部が接するように設けられた第2の導電層と、第2の導電層上に設けられた第2の絶縁層と、第1の半導体層、第2の半導体層、不純物半導体層、第2の導電層、及び第2の絶縁層を覆って設けられた第3の絶縁層と、少なくとも、第3の絶縁層上に設けられた第3の導電層と、を有し、第1の絶縁層乃至第3の絶縁層に開口部が設けられたデュアルゲート型トランジスタの第1の絶縁層の厚さと第2の絶縁層の厚さを概ね等しいものとする。

(もっと読む)

薄膜トランジスタアレイ基板、その製造方法、及び液晶表示装置

【課題】 FFSモードの液晶表示装置において、半透過マスクを用いることなくフォトリソグラフィー工程数を削減することができ、さらに断線を防止することができる薄膜トランジスタアレイ基板、その製造方法、及び液晶表示装置を提供すること

【解決手段】本発明にかかる薄膜トランジスタアレイ基板は、ゲート配線43を覆うゲート絶縁膜11上に形成されたソース配線44と、ゲート絶縁膜11上に形成され、ドレイン電極5の下のほぼ全面と、ソース電極4の下のほぼ全面と、ソース配線44の下のほぼ全面と、ゲート電極の対面とに配設された半導体層2と、一部がドレイン電極5の上に直接重なり形成された画素電極6と、ソース電極4及びソース配線44の上に、画素電極6と同じ層によって直接重なり形成された透明導電パターン6aと、画素電極6及び透明導電パターン6aを覆う層間絶縁膜12上に形成され、画素電極6との間でフリンジ電界を発生させる対向電極8と、を備えるものである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

FINFETSおよびその形成方法

【課題】フィン電界効果トランジスタのソース/ドレイン構造を提供する。

【解決手段】基板上のフィンチャネル本体110a、110b、フィンチャネル本体110a、110b、上に配置されたゲート電極115、およびフィンチャネル本体110a、110b、に隣接して配置され、どのフィン構造も実質的に含まない、少なくとも1つのソース/ドレイン(S/D)領域120a,120b及び125a,125bを含むフィン電界効果トランジスタ(FinFET)。

(もっと読む)

半導体装置およびその製造方法

【課題】薄膜BOX−SOI基板に形成される電界効果型トランジスタの信頼性および動作特性の劣化を防ぐことのできる技術を提供する。

【解決手段】薄膜BOX−SOI基板の主面上に所定の間隔で配置されたnウェルnwおよびpウェルpwが形成されており、pウェルpwに形成されたnMIS1nは、SOI層1iの主面上に所定の距離を隔てて積み上げられた半導体層に形成された一対のn型ソース・ドレイン領域2nと、一対のn型ソース・ドレイン領域2nに挟まれたゲート絶縁膜3、ゲート電極4、およびサイドウォール5とを有しており、nウェルnwとpウェルpwとの間に素子分離10を形成し、素子分離10の側端部が、n型ソース・ドレイン領域2nの側端部(BOX層1bの側壁部)よりもゲート電極4側に広がっている。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

フラットパネルディスプレイ半導体の製造方法

【課題】a−Siプロセスと、ポリ−Siプロセスとを組み合わせることが可能なプロセスを提供することである。

【解決手段】プロセス800は、アモルファスシリコン又はアモルファスシリコンに適合可能なプロセスを用いて、ディスプレイパネル用のポリ−最終構造を形成する(ブロック810)。ポリ−最終構造は、チャネルシリコン前駆体を有する。次に、プロセス800は、ポリシリコン固有のプロセスを用いて、ポリ−最終構造からディスプレイパネルを形成する(ブロック820)。

(もっと読む)

半導体装置の製造方法

【課題】半導体層に形成したリセスにモフォロジの良好な別の半導体層をエピタキシャル成長させる。

【解決手段】Si基板上にゲート絶縁膜、ゲート電極及びサイドウォールスペーサを形成した後(ステップS1,S2)、そのSi基板のソース・ドレイン領域を形成する部分に、ドライエッチングで第1リセスを形成する(ステップS3)。そして、ドライエッチングによってエッチングダメージが生じた第1リセスの表層部をウェットエッチングで除去することによって第2リセスを形成した後(ステップS4)、第2リセスにSiGe層をエピタキシャル成長させる(ステップS5,S6)。これにより、Si基板に形成したリセスに、モフォロジの良好なSiGe層を形成することが可能になる。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】微細化TFTに適用が可能な低抵抗のソース・ドレイン構造を低温プロセスで形成可能な薄膜半導体及びその製造方法を提供すること。

【解決手段】透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成され、側壁に絶縁膜からなるサイドウオールスペーサを有するゲート電極、及び前記ソース領域並びにドレイン領域上にそれぞれ600℃以下の温度で固相成長された、第1導電型の不純物を含む積上げソース多結晶半導体層並びに第1導電型の不純物を含む積上げドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

液晶表示装置、及びその製造方法

【課題】開口率を向上することができるFFSモードの液晶表示装置、及びその製造方法を提供すること

【解決手段】本発明にかかる液晶表示装置は、TFT50を有するTFTアレイ基板と、TFTアレイ基板と対向配置された対向基板との間に液晶が挟持された液晶表示装置であって、TFTアレイ基板上において、少なくとも一部がTFT50のドレイン電極5に直接重なるよう、ドレイン電極5の上又は下に直接形成された画素電極6と、画素電極6を覆う層間絶縁膜12と、層間絶縁膜12上に形成され、画素電極6との間でフリンジ電界を発生させるスリットを有する対向電極8と、を備えるものである。

(もっと読む)

半導体装置および半導体装置を製造する方法

【課題】ソース・ドレイン領域の占有面積が小さい半導体装置およびそれを製造する方法を提供する。

【解決手段】本発明の半導体装置は、素子分離領域と活性領域を有する半導体装置であって、活性領域とゲート酸化膜が接する第1の面より上に、ソース領域およびドレイン領域の一部が存在し、該ソース領域および/または該ドレイン領域と、該ソース領域および/または該ドレイン領域に電気的に接続される電極とが接する第2の面が、該第1の面に対して傾いている。

(もっと読む)

半導体装置の製造方法、半導体装置および半導体層の形成方法

【課題】半導体上にモフォロジの良好な半導体層を選択的にエピタキシャル成長させる。

【解決手段】リセスド・ソース・ドレイン型pMOSFETを形成する際、STIを形成したSi基板上にゲート絶縁膜を介してゲート電極を形成し(ステップS1)、サイドウォールを形成した後(ステップS2)、その両側のSi基板に部分的にリセスを形成する(ステップS3)。そして、そのSi基板のリセス内に、下層部の方が上層部よりも、サイドウォールやSTIに対する成長選択性が低くなるような条件を用いて、下層部と上層部をエピタキシャル成長させ、SiGe層を形成する(ステップS4,S5)。これにより、Si基板のリセス内に、サイドウォール等に対する成長選択性を確保しつつ、モフォロジの劣化が抑えられたSiGe層を形成することが可能になる。

(もっと読む)

自己整合エピタキシャルソース及びドレイン張り出し部を有する半導体デバイス

ゲート誘電層に近接する自己整合ソース及びドレイン張り出し部を有するトランジスタの作製方法は、基板上にゲート積層体を作製する工程、前記ゲート積層体に隣接する前記基板の領域へドーパントを注入する工程であって、前記ドーパントは前記基板のエッチング速度を増大させ、かつ前記ソース及びドレイン張り出し部の位置を画定する工程、前記基板のドーパントが注入された領域上に設けられた前記ゲート積層体の横方向で対向する面に一対のスペーサを形成する工程、前記基板のドーパントが注入された領域及び該領域の下に位置する前記基板の一部をエッチングする工程であって、前記ドーパントが注入された領域のエッチング速度は該領域の下に位置する前記基板の一部のエッチング速度よりも速い工程、並びに、前記の基板のエッチングされた部分中にシリコンベースの材料を堆積する工程、を有する。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】フォトレジストを用いることなく薄膜を加工することができる加工方法及び半導体装置の作製方法を提供する。特に、容易に薄膜を加工できる方法及び加工後の薄膜の不良を防止する方法及び半導体装置の作製方法を提供することを課題とする。

【解決手段】基板上に光吸収層を形成し、光吸収層にレーザビームを選択的に照射して、レーザビームが照射された領域の光吸収層を除去する。残存する光吸収層に一導電型を付与する不純物元素又は不活性元素を添加して、光吸収層の引っ張り応力をレーザビームの照射前よりも小さくする。

(もっと読む)

半導体装置の作製方法およびレーザ加工装置

【課題】半導体装置の製造工程において、フォトレジストを用いたリソグラフィー工程を簡略化する半導体装置の製造技術を提供して、製造コストを低減し、スループットを向上させる。

【解決手段】基板上に第1材料層、第2材料層を順次積層して被照射体を形成する。当該被照射体に、第1材料層に吸収される第1のレーザビームと、第2材料層に吸収される第2のレーザビームを重畳するように照射し、該重畳するようにレーザビームが照射された領域の一部或いは全部をアブレーションさせ、開口を形成する。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】導電層上にマスクを設け、マスクを設けた導電層上に絶縁膜を成膜し、マスクを除去することで開口を有する絶縁層を形成する。露出した導電層と接するように開口に導電膜を形成することによって、導電層及び導電膜は絶縁層を介して電気的に接続することができる。開口の形状はマスク形状を反映し、柱状(角柱、円柱、三角柱など)、針状などを用いることができる。

(もっと読む)

1 - 20 / 39

[ Back to top ]