Fターム[5F110HM20]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | その他 (49)

Fターム[5F110HM20]に分類される特許

1 - 20 / 49

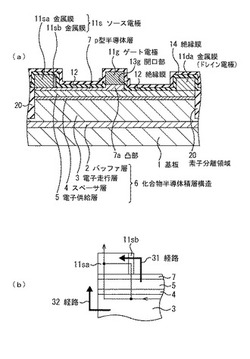

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11daと、電子供給層5とゲート電極11gとの間に形成された第1のp型半導体層7aと、ソース電極11sと電子供給層5との間に形成されたp型半導体層7と、が設けられている。第2のp型半導体層7上のソース電極11sには、第1の金属膜11saと、第1の金属膜11saにゲート電極11g側で接し、第1の金属膜11saよりも抵抗が大きい第2の金属膜11sbと、が設けられている。

(もっと読む)

半導体素子

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半

導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを

課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレ

イン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート

絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は

側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

横型素子を有する半導体装置

【課題】高速スイッチング動作を行う場合でも、アバランシェブレークダウンを抑制でき、スイッチング損失低減や素子破壊を抑制することが可能な構成とする。

【解決手段】横型FWD7などの横型素子において、SRFP21の全抵抗Rの抵抗値を90kΩ〜90MΩ、好ましくは270kΩ〜27MΩ、より好ましくは900kΩ〜9MΩとすることにより、2ndピーク時のアノード電流IAなどの電流が大きくなることを抑制できる。これにより、高速スイッチング動作を行う場合でもアバランシェブレークダウンを抑制でき、横型FWD7のスイッチング損失低減や素子破壊を抑制することが可能となる。

(もっと読む)

窒化物半導体装置

【課題】ゲート電極から染み出した金属がドレイン電極に到達することを抑制して、ドレイン−ゲート間の絶縁破壊を抑制する窒化物半導体装置を提供する。

【解決手段】ゲート電極5の直下に位置するAlGaN層22と、このAlGaN層22の直上に位置する絶縁膜30との間の界面Sに、ゲート電極5とドレイン電極1との間に位置するように、溝50を設けている。ゲート電極5から界面Sを伝ってドレイン電極1側へ染み出した金属を、溝50によって、堰き止めることができる。

(もっと読む)

表示装置、及び、その製造方法

【課題】薄膜トランジスタにおいて生じるリーク電流を抑えつつ、表示装置の生産性を向上させることを目的とする。

【解決手段】基板301と、基板301に形成されている複数の薄膜トランジスタTFTと、を有する表示装置であって、薄膜トランジスタTFTは、ゲート電極303と、ゲート電極303の上側に配置される微結晶半導体層305と、微結晶半導体層305上に配置される非晶質半導体層306と、を有し、非晶質半導体層306の水素濃度が、12atom%以下である、ことを特徴とする表示装置。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタ

【課題】オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTを提供する。

【解決手段】n型バリア層15を形成することでエミッタ側のキャリア濃度を高くしてオン電圧の低減を図りつつ、n型バリア層15を隣り合うエミッタ間に形成しないようにすることで、ターンオフ時間の改善を図る。また、このような構造により、スイッチング時の破壊耐量の向上も図ることも可能となる。したがって、オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTとすることが可能となる。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および電子装置

【課題】 ミリ波以上の周波数において、安定して、高い利得および動作周波数が得られる電界効果トランジスタを提供する。

【解決手段】 基板11上の動作層13の上に、ソース電極14、ドレイン電極15、ゲート電極18、絶縁膜17が形成され、

ゲート電極18は、ソース電極14とドレイン電極15の間に配置され、

絶縁膜17は、ゲート電極18とドレイン電極15の間に配置され、

フィールドプレート電極19は、絶縁膜17上に形成され、かつ、ソース電極14と電気的に接続され、

ゲート電極18上部は、ソース電極14側およびドレイン電極15側に突出し、

フィールドプレート電極19下端は、ゲート電極18下端よりも下方に配置され、

フィールドプレート電極19上端は、ゲート電極19上部においてドレイン電極15側に最も突出した部分よりも下方に配置されている電界効果トランジスタ。

(もっと読む)

トランジスタ

【課題】高い電流駆動力と高いカットオフ特性を備えたトランジスタを提供する。

【解決手段】本発明の一態様に係るトランジスタは、ゲート電極12下にゲート絶縁膜を介して形成され、ソース側端部10Sを含む半導体領域10aとドレイン側端部10Dを含む導体領域10bとを有し、ソース側端部10Sにおけるチャネル幅方向の幅Laがドレイン側端部10Dにおけるチャネル幅方向の幅Lbよりも小さいグラフェン膜10と、グラフェン膜10のソース側端部10Sに接続され、ショットキーバリア接合を形成するソース電極と、グラフェン膜10のドレイン側端部10Dに接続され、オーミック接合を形成するドレイン電極と、を有する。

(もっと読む)

トランジスタおよびその製造方法

【課題】高い電流駆動力と高いカットオフ特性を備えたトランジスタおよびその製造方法を提供する。

【解決手段】本発明の一態様に係るトランジスタ100は、導体領域10aと表面に原子が結合した半導体領域10bとを有し、チャネルとして機能するグラフェン膜10と、グラフェン膜10上にゲート絶縁膜11を介して形成されたゲート電極12と、を有し、導体領域10aと半導体領域10bが形成するショットキー接合のトンネル電流をスイッチング動作に用いる。

(もっと読む)

縦型バイポーラインジェクタを有するDRAMメモリセル

【課題】フローティングボディDRAMセルにおいて表面積が縮小された改良型メモリセルを提供する。

【解決手段】ソースSと、ドレインDと、ソースSとドレインD間のフローティングボディFBとを有するFETトランジスタと、FETトランジスタのフローティングボディへの電荷の注入を制御可能なインジェクタであって、エミッタ15と、ベースと、FETトランジスタのフローティングボディFBによって形成されたコレクタとを有するバイポーラトランジスタからなるインジェクタとを備え、バイポーラトランジスタのエミッタ15が、FETトランジスタのソース22がバイポーラトランジスタのベースとして働くように配置される。複数のメモリセルを備えるメモリアレイ、及びこのようなメモリセルを制御する方法にも適用される。

(もっと読む)

半導体素子、半導体装置及びそれらの作製方法

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

トランジスタ基板及びトランジスタ基板の製造方法

【課題】微結晶シリコンをチャネル領域として用い、良好にリーク電流を抑制することが可能なトランジスタを備えるトランジスタ基板及びトランジスタ基板の製造方法を提供する。

【解決手段】トランジスタ基板におけるトランジスタ100は、基板11と、ゲート電極112と、ゲート絶縁膜113と、半導体層(チャネル領域)114と、ドレイン領域116、ソース領域117と、ドレイン電極118と、ソース電極119と、を備える。ドレイン領域116と半導体層114が接触する箇所及びソース領域117と半導体層114が接触する箇所のうち少なくとも一方は、ゲート電極112と比較し、薄膜トランジスタ100のチャネル長方向に外側に位置するように形成されている。このようにストッパ膜115を形成することにより、電界の急激な変化を抑制することができ、良好にリーク電流を抑制することができる。

(もっと読む)

逆耐圧を有する縦型窒化ガリウム半導体装置

【課題】逆阻止能力を有し、低オン抵抗で高速スイッチング特性を有する素子を提供すること。

【解決手段】シリコン基板101と、シリコン基板101上に形成されたバッファ層102,103と、バッファ層102、103上に形成された窒化ガリウム半導体層104と、シリコン基板101の裏面からシリコン基板101ならびにバッファ層102、103を貫通して窒化ガリウム半導体層104に達する深さで形成されたトレンチ溝112と、このトレンチ溝112の中に形成された金属膜113と、を備え、金属膜113と窒化ガリウム半導体層104とがショットキー接合を形成する逆耐圧を有する窒化ガリウム半導体装置とする。

(もっと読む)

GaN系電界効果トランジスタおよびその製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】GaN系電界効果トランジスタ100は、基板101と、基板の上に形成されたp型GaN系半導体材料からなるチャネル層104と、チャネル層上に形成され、チャネル層よりもバンドギャップエネルギーが大きいGaN系半導体材料からなる電子供給層106と、電子供給層の一部が除去されて表出したチャネル層104の表面に形成されたゲート絶縁膜111と、ゲート絶縁膜上に形成されたゲート電極112と、ゲート電極を挟んで形成されたソース電極109及びドレイン電極110と、電子供給層106上に形成されたゲート絶縁膜111とは別の絶縁膜であって、電流コラプス低減効果のある第2の絶縁膜113と、を備える。

(もっと読む)

横型MOSトランジスタ

【課題】

オン抵抗の低減を図った横型MOSトランジスタを提供する。

【解決手段】

第1導電型の半導体層と、半導体層の第1領域に深さ方向に形成される第1酸化膜と、半導体層の第1領域とは離間した第2領域に深さ方向に形成される第2酸化膜と、半導体層内で第1酸化膜に隣接する領域に深さ方向に形成されるゲート電極と、半導体層内で第2酸化膜に隣接する領域に形成される制御電極と、半導体層の第1酸化膜と第2酸化膜で挟まれる領域の表面部のうちの第1酸化膜の近傍の領域に形成される第2導電型領域と、第2導電型領域の表面部のうちの第1酸化膜の近傍の領域に形成される第1導電型領域と、第1導電型領域及び第2導電型領域の上に形成されるソース電極と、半導体層の第1酸化膜と第2酸化膜で挟まれる領域の表面部のうちの第2酸化膜の近傍の領域に形成される第1導電型領域と、第1導電型領域の上に形成されるドレイン電極とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御でき、短チャネル効果を効果的に抑制できる半導体装置を提供する。

【解決手段】シリコン基板1と接してショットキー接合を形成するソース領域10,ドレイン領域11と、上記シリコン基板1とソース領域10との境界が露出する部分およびシリコン基板1とドレイン領域11との境界が露出する部分を被覆するように設けられた絶縁層を備える。上記絶縁層は、シリコン基板1とソース領域10との境界およびシリコン基板1とドレイン領域11との境界を跨ぐように、シリコン基板1とソース領域10に接すると共にシリコン基板1とドレイン領域11に接する固定電荷を含む領域8を有する。上記固定電荷は、熱平衡状態において荷電している。

(もっと読む)

横型半導体装置

【課題】 バイポーラで動作する横型半導体装置において、オン電圧を低くする技術を提供する。

【解決手段】 半導体装置10は、半導体層54の表面に設けられている第1主電極20と第2主電極2を備えている。半導体層54は、第1主電極20に接触しているn型の第1半導体領域24と、第2主電極2に接触しているp型の第2半導体領域58と、第1半導体領域24と第2半導体領域58の間に設けられているn型の第3半導体領域12を有している。第3半導体領域12は、第1半導体領域24と第2半導体領域58を結ぶ第1方向に沿って伸びている第1層8と第2層40を有している。第1層8と第2層40は、第1方向に直交する第2方向に並んでいる。第1層8は、不純物濃度が第1方向に均一である。第2層40は、第1層8よりも不純物濃度が濃く、不純物濃度が第1半導体領域24側から第2半導体領域58側に向けて増加している。

(もっと読む)

1 - 20 / 49

[ Back to top ]