Fターム[5F110NN03]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935) | 複数層 (3,316)

Fターム[5F110NN03]に分類される特許

1,301 - 1,320 / 3,316

半導体装置およびその作製方法

【課題】薄膜トランジスタの製造工程における不特定な要因によって、しきい値電圧がマイナス側、或いはプラス側にシフトすることがある。0Vからシフトする値が大きい場合には、駆動電圧の増大を招き、結果として半導体装置の消費電力を増加させてしまう。

【解決手段】酸化物半導体層を覆う第1の保護絶縁膜として平坦性のよい樹脂層を形成した後、樹脂層上に第2の保護絶縁膜としてスパッタ法またはプラズマCVD法を用いて低パワー条件で成膜される第2の保護絶縁膜を形成する。さらに、しきい値電圧を所望の値に制御するため、酸化物半導体層の上下にゲート電極を設ける。

(もっと読む)

薄膜トランジスタ

【課題】電界効果移動度が高く、オン電流が大きい薄膜トランジスタを提供する。

【解決手段】ゲート電極と、ゲート電極を覆って設けられたゲート絶縁層と、ゲート絶縁層上に、ゲート電極と重畳して設けられた半導体層と、半導体層上の一部に設けられてソース領域及びドレイン領域を形成する不純物半導体層と、不純物半導体層上に設けられた配線層と、を有し、ソース領域及びドレイン領域の幅は、半導体層の幅よりも小さく、半導体層の幅は、少なくともソース領域とドレイン領域の間において拡大された薄膜トランジスタとする。

(もっと読む)

半導体装置、表示装置、及び電子機器

【課題】実動作の阻害を低減し、ノイズによる影響を低減する。

【解決手段】電極と、電極に電気的に接続された配線と、平面視において前記電極と重なる酸化物半導体層と、断面視において前記電極と前記酸化物半導体層の間に設けられた絶縁層と、前記配線を介して前記電極から信号が入力され、入力された前記信号に応じて動作が制御される機能回路と、を有する構造であり、酸化物半導体層及び絶縁層と、配線又は電極と、を用いて容量素子を構成する。

(もっと読む)

液晶表示装置、及び電子機器

【課題】 TFTの工程を複雑化させることなくシステムオンパネル化を実現し、なおか

つコストを抑えることができる液晶表示装置の提案を課題とする。

【解決手段】 画素部に液晶素子と、液晶素子に印加される電圧を制御するTFTとを有

する画素が設けられており、駆動回路が有するTFTと、液晶素子に印加される電圧を制

御するTFTとは、ゲート電極とゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁

膜を間に挟んでゲート電極と重なっている第1の半導体膜と、第1の半導体膜上に形成さ

れた一対の第2の半導体膜とを有し、一対の第2の半導体膜には一導電型を付与する不純

物が添加されており、第1の半導体膜はセミアモルファス半導体で形成されていることを

特徴とする液晶表示装置。

(もっと読む)

高耐圧半導体装置および高電圧集積回路装置

【目的】ワイヤ接続における高耐圧半導体装置において、複雑なプロセス製造工程も、複雑な裏面加工工程も一切伴わず、低コストで高耐圧化、高信頼性化を実現できる高耐圧半導体装置およびそれを用いた高電圧集積回路装置を提供することにある。

【構成】半導体基板100上に誘電体層101を介して半導体層102が形成され、半導体層102上にドレイン層113と、ドレイン層113を内包するように形成されたバッファ層112と、ドレイン層113と離間し、その周りを囲むように形成されたソース層114と、ソース層114を内包するように形成されたウエル層111と、半導体層102上にゲート絶縁膜を介して形成されたゲート電極110と、を備えた高耐圧半導体装置において、ドレイン層113及び、バッファ層112の平面形状が非連続または連続の環状とする。

(もっと読む)

薄膜トランジスタアレイ基板、及びその製造方法、並びに液晶表示装置

【課題】液晶分子を駆動するための画素電極と共通電極が、平面視上、重畳領域を有するTFTアレイ基板において、製造工程の短縮化を実現する。

【解決手段】本発明に係るTFTアレイ基板は、ドレイン領域10Dから延在される画素電極11を備える島状の結晶性半導体層3と、結晶性半導体層3の上層に形成されたゲート絶縁膜21と、ゲート絶縁膜上21であって、チャネル領域10Cと対向配置されるゲート電極12と、ゲート電極12より上層に配置され、絶縁層25に形成されたコンタクトホールCHを介してソース領域10Sと電気的に接続されたソース電極13と、絶縁層25より上層に形成され、画素電極11と重畳する領域を有する共通電極14とを備える。

(もっと読む)

表示装置

【課題】極めて簡単な構成にも拘わらず、半導体層への光照射を低減し、オフ電流の発生の抑制を図った薄膜トランジスタを具備する表示装置の提供。

【解決手段】画像表示部が形成された基板に薄膜トランジスタが形成された表示装置であって、

前記薄膜トランジスタは、

ゲート電極と、

前記ゲート電極を被って形成されたゲート絶縁膜と、

前記ゲート絶縁膜上であって前記ゲート電極に重畳して形成される半導体層と、

前記半導体層上に形成され互いに対向して配置された一対の電極と、

を備え、

前記半導体層は、平面的に観た場合、前記ゲート電極の形成領域内に配置され、前記ゲート電極側から、結晶性半導体層および非晶質半導体層の順次積層体から構成され、

前記ゲート電極は、少なくとも前記半導体層と対向する領域において、光透過率が0.3%以下となる膜厚で形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】連続発振のレーザー光の照射により形成された結晶質半導体層において、結晶欠陥の発生を抑制する。

【解決手段】絶縁基板10に非晶質半導体膜12を成膜する半導体膜成膜工程と、非晶質半導体膜12を覆うようにキャップ膜13を成膜するキャップ膜成膜工程と、キャップ膜13を介して非晶質半導体膜12に連続発振のレーザー光Bを幅方向にオーバーラップするように走査しながら照射して、結晶質半導体膜12aを形成する結晶質半導体膜形成工程と、結晶質半導体膜12a及びキャップ膜13の積層膜をパターニングして、結晶質半導体層12ba及びキャップ層13baを形成する結晶質半導体層形成工程とを備える半導体装置の製造方法であって、キャップ膜13の膜厚は、10nm〜30nmである。

(もっと読む)

液晶パネル

【課題】複数個のアレイ基板を同時に形成するためのアレイ基板用マザー基板にスピンコ

ーターを用いてレジスト塗布する際、表示領域内に放射状の塗布ムラが生じないような配

線パターンとされたアレイ基板を備えた液晶パネルを提供すること。

【解決手段】本発明の液晶パネルは、液晶層を挟持して対向配置された一対の基板を有し

、前記一対の基板の一方の表示領域には複数のサブ画素がマトリクス状に形成されている

と共に、表示領域の周縁部には表示領域からゲート配線39G及びソース配線39Sが端

子領域まで延在されている液晶パネルにおいて、前記互いに隣接するゲート配線39G及

びソース配線39S等の引き回し配線の直近の屈曲点P1同士を順次結んでなるラインが

、端子領域が形成されている辺と実質的に平行な直線ラインL1とされている。

(もっと読む)

半導体構造体およびその製造方法(移動度が最適化された方位を有する半導体ナノワイヤ)

【課題】高いオン電流、低いオフ電流を与えるp型半導体ナノワイヤ・デバイス、n型半導体ナノワイヤ・デバイスを提供する。

【解決手段】各々が半導体リンク部30C,50Cと2つの隣接するパット部30A,30B,50A,50Bを含む半導体構造体で、半導体リンク部の側壁は、第1の半導体構造体の場合には正孔の移動度を最大化するように、第2の半導体構造体の場合には電子の移動度を最大化するように方位を定める。半導体構造体の酸化による薄化で、半導体リンク部の幅は、異なる結晶方位ごとに異なる速度で小さくされる。異なる量の薄化の結果、薄化後に得られる半導体ナノワイヤが目標とするサブリソグラフィ寸法となるように、予め決定される。異なる結晶面に対する異なる薄化速度を補償することによって、過剰な薄化又は不十分な薄化がなされることなく、最適なサブリソグラフィ幅を有する半導体ナノワイヤを形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を無機絶縁膜で覆うことなく加熱処理を行って酸化物半導体層が結晶化されると、結晶化による表面凹凸などが形成され、電気特性のバラツキが発生する恐れがある。

【解決手段】酸化物半導体層成膜直後から酸化物半導体層上に接して酸化シリコンを含む無機絶縁膜を形成する直前までの間に1回も加熱処理を行わず、基板上の酸化物半導体層上に接して第2の絶縁膜を形成した後に加熱処理を行うプロセス順序とする。また、酸化シリコンを含む無機絶縁膜において、膜中に含まれる水素密度は、5×1020/cm3以上、または窒素密度は、1×1019/cm3以上とする。

(もっと読む)

電気光学装置およびプロジェクタ

【課題】電気光学装置において、画素開口率を高めると同時に蓄積容量の増大を図り且つ斜めの入射光や戻り光に対する遮光性能を高めることにより、クロストークやゴーストを低減しコントラスト比を向上して、高品位の画像表示を行う。

【解決手段】電気光学装置は、TFTアレイ基板(10)上に、画素電極(9a)と、画素電極をスイッチング制御するTFT(30)と、このTFTに接続された走査線(3a)及びデータ線(6a)とを備える。平面的に見てデータ線に重なる領域に、蓄積容量(70)が構築される。蓄積容量は、走査線と同一膜からなる第1容量電極(13)と、画素電極及びTFT間を中継接続するバリア層(34)と同一膜からなる第2容量電極(33)とが、誘電体膜(42)を介して対向配置されてなる。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層とで積層されたゲート電極を含むゲート配線と、半導体層と前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、半導体層と電気的に接続され、第3の導電層と第4の導電層とで積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

半導体装置およびその作製方法

【課題】開口率の高い半導体装置を提供することを課題とする。または、開示する発明の一態様は、消費電力の低い半導体装置を提供することを課題とする。または、開示する発明の一態様は、配線抵抗の低い半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた透光性を有する第1の電極と、基板上に設けられた透光性を有する第2の電極と、第1の電極および第2の電極と電気的に接続するように設けられた透光性を有する半導体層と、第1の電極と電気的に接続された第1の配線と、少なくとも半導体層を覆うように設けられた絶縁層と、半導体層と重なる領域の絶縁層上に設けられた透光性を有する第3の電極と、第3の電極と電気的に接続された第2の配線と、を有する。

(もっと読む)

電気光学装置および電子機器

【課題】第1中間導電層や第2中間導電層に起因したデッドスペースを削減する。

【解決手段】第1スイッチング素子Q1と第2スイッチング素子Q2とは走査線22をゲートとして動作する。第1スイッチング素子Q1は、第1データ線24Aと第1中間導電層541との間に電気的に介在し、第2スイッチング素子Q2は、第2データ線24Bと第2中間導電層542との間に電気的に介在する。第1中間導電層541は第1電極31に導通し、第2中間導電層542は第2電極32に導通する。第1中間導電層541の少なくとも一部と第2中間導電層542の少なくとも一部とは、平面視で走査線22に重なる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】低抵抗なAl配線材料を用いて、生産コストの低下および生産性の向上を図ることができる薄膜トランジスタの製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、Arガスを用いたスパッタリングによって純AlまたはAl合金を第1層として成膜する工程と、前記第1層の上層に、Ar+N2混合ガスまたはAr+NH3混合ガスを用いたスパッタリングによって、前記第1層の材料に加えて窒化アルミニウムも部分的に含む第2層を成膜する工程と、別途形成するコンタクトホールを介して透明膜電極と第1電極の前記第2層とを電気的に接続する工程を含むものである。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。

【解決手段】半導体層を酸化物半導体層とする逆スタガ型薄膜トランジスタを含む半導体装置において、酸化物半導体層上にバッファ層を有する。バッファ層は、半導体層のチャネル形成領域と、ソース電極層及びドレイン電極層とに接する。バッファ層は膜内に抵抗分布を有し、半導体層のチャネル形成領域上に設けられる領域の電気伝導度は半導体層のチャネル形成領域の電気伝導度より低く、ソース電極層及びドレイン電極層と接する領域の電気伝導度は半導体層のチャネル形成領域の電気伝導度より高い。

(もっと読む)

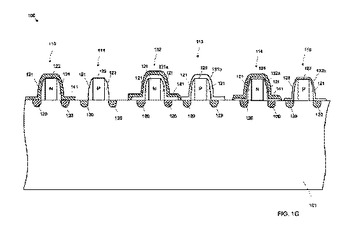

ストレス低減層を有する集積回路装置

集積回路装置が開示され、集積回路装置はNMOSゲート薄膜スタック(122)を覆う張力ストレス層(141)を有するデュアルストレスライナーNMOSデバイス(110)と、PMOSゲート薄膜スタック(123)を覆う圧縮ストレス層(142)を有するデュアルストレスライナーPMOSデバイス(111)と、張力ストレス層(141)とNMOSゲート薄膜スタック(124)との間に延在するストレス低減層(131a)を有する低減ストレスのデュアルストレスライナーNMOSデバイス(112)と、圧縮ストレス層(142)とPMOSゲート薄膜スタック(125)との間に延在するストレス低減層(131b)を有する低減ストレスのデュアルストレスライナーPMOSデバイス(113)とを含む。発明の実施形態において、追加の低減ストレスのデュアルストレスライナーNMOSデバイス(114)と低減ストレスのPMOSデバイス(115)とは、ストレス低減層(132a,132b)の厚みおよび/または材料特性を変更することによって形成される。  (もっと読む)

(もっと読む)

薄膜トランジスタ及びその製造方法、並びにそれを含む有機電界発光表示装置

【課題】薄膜トランジスタ及びその製造方法、並びにそれを含む有機電界発光表示装置を提供する。

【解決手段】基板と、前記基板上に位置し、チャンネル領域、イオンを含むソース/ドレイン領域及びオフセット領域を含む半導体層と、前記半導体層上に位置するゲート絶縁膜と、前記ゲート絶縁膜上に位置するゲート電極と、前記ゲート電極上に位置する第1絶縁膜と、前記第1絶縁膜上に位置する第2絶縁膜と、前記第2絶縁膜上に位置し、前記半導体層のソース/ドレイン領域とそれぞれ電気的に接続されるソース/ドレイン電極とを含み、前記ソース/ドレイン領域上の前記ゲート絶縁膜及び前記第1絶縁膜の厚さの合計は、0を超え前記ソース/ドレイン領域に含まれたイオンの垂直浸透深さより小さいことを特徴とする。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置および電子機器

【課題】ボトムゲート構造およびトップゲート構造の双方の特長を兼ね備えた半導体装置の製造方法、半導体装置、電気光学装置、および電子機器を提供すること。

【解決手段】素子基板10上の薄膜トランジスター30は、ボトムゲート構造を備え、かつ、ポリシリコン膜からなる島状半導体膜1aにチャネル領域1g、低濃度ソース領域1b、低濃度ドレイン領域1c、高濃度ソース領域1d、高濃度ドレイン領域1eを備えたGOLD構造を備えている。素子基板10を製造する際、諧調露光により形成したレジストマスクと、かかるレジストマスクに対するエッチバックを利用して、高濃度不純物の導入、半導体膜のパターニングと、ゲート絶縁膜2aと同層の層間絶縁膜のコンタクトホールを形成すべき領域からの半導体膜の除去、および低濃度不純物の導入とを行なう。

(もっと読む)

1,301 - 1,320 / 3,316

[ Back to top ]