Fターム[5F110QQ09]の内容

Fターム[5F110QQ09]に分類される特許

21 - 40 / 1,360

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、インジウムを含む酸化物半導体膜、ゲート電極層と重畳する酸化物半導体膜上に接する絶縁層が順に積層され、酸化物半導体膜及び絶縁層に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、絶縁層表面における塩素濃度を1×1019/cm3以下とし、かつインジウム濃度を2×1019/cm3以下とする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いたボトムゲート型のトランジスタにおいて、高いゲート電圧がゲート電極層に印加される場合、ドレイン電極層の端部近傍(及びソース電極層の端部近傍)に生じる恐れのある電界集中を緩和し、スイッチング特性の劣化を抑え、信頼性が向上された構造を提供する。

【解決手段】チャネル形成領域上に重なる絶縁層の断面形状を、テーパ形状とし、チャネル形成領域上に重なる絶縁層の膜厚は、0.3μm以下、好ましくは5nm以上0.1μm以下とする。チャネル形成領域上に重なる絶縁層の断面形状の下端部のテーパ角θを60°以下、好ましくは45°以下、さらに好ましくは30°以下とする。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物の濃度を低減する。また、酸化物半導体膜の結晶性を向上させる。該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記ゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜における、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域において、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さく、少なくとも第1の領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

(もっと読む)

半導体装置

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

表示装置

【課題】高開口率を有し、容量の大きな保持容量を有する表示装置を提供する。

【解決手段】第1導電膜によるゲート電極と、第1導電膜上の第1絶縁層によるゲート絶縁膜と、第1絶縁層上にゲート電極と重なる第1半導体層と、第1半導体層上かつゲート電極に重なる第2絶縁層によるチャネル保護膜と、第1半導体層と重なりソース領域及びドレイン領域に分離された導電性の第2半導体層と、第2半導体層上の第2導電膜によるソース電極及びドレイン電極とを含む薄膜トランジスタと、第2導電膜上に形成された第3絶縁層と、第3絶縁層上の第3導電膜により形成され、ソース電極またはドレイン電極の一方と接続する画素電極と、第1絶縁層上の容量配線と、容量配線上の第3絶縁層を挟んで、画素電極の重畳領域に形成される保持容量とを有する表示装置及びその作製方法。

(もっと読む)

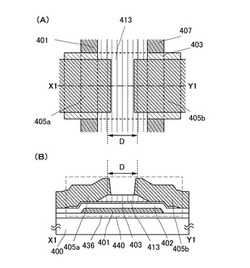

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】ソース電極層405a及びドレイン電極層405bの端部と、ゲート電極層401の端部とを重畳させ、更に酸化物半導体層403のチャネル形成領域となる領域に対して、ゲート電極層401を確実に重畳させることで、トランジスタのオン特性を向上させる。また、絶縁層491中に埋め込み導電層を形成し、埋め込み導電層481a,481bと、ソース電極層405a及びドレイン電極層405bとの接触面積を大きくとることで、トランジスタのコンタクト抵抗を低減する。ゲート絶縁層402のカバレッジ不良を抑制することで、酸化物半導体層403を薄膜化し、トランジスタの微細化を実現する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電気特性の安定した半導体装置を提供する。とくに、酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜と接して形成されたソース電極、及びドレイン電極と、を有し、ゲート絶縁膜は、少なくとも酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された酸素放出型の酸化膜と、により構成され、酸素放出型の酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

半導体装置

【課題】電流駆動能力がより小さなクロック信号生成回路を適用することが可能な半導体装置を提供する。

【解決手段】nチャネル型トランジスタで構成されるスイッチ及び論理回路を有し、スイッチは導通状態又は非導通状態がクロック信号によって選択され、論理回路は、ブートストラップ回路と、入力信号が入力される入力端子と、反転入力端子と、出力端子とを有し、高電源線と出力端子との接続を反転入力端子に入力される信号によって制御し、低電源線と出力端子との接続を入力端子に入力される信号によって制御することによって、入力信号がローレベル電位の場合には、ブートストラップ回路を用いて出力端子の電位を上昇させることにより出力端子から高電源電位を出力し、トランジスタは、チャネルが形成される半導体層と、半導体層を挟んで上下に設けられた一対のゲート電極とを有し、一対のゲート電極の他方はソースと接続される。

(もっと読む)

半導体装置

【課題】液晶等の電気光学素子若しくは発光素子等を表示媒体として用いる表示装置及びその駆動方法を提供する。

【解決手段】劣化しやすいトランジスタのゲート電極に、オンしたトランジスタを介して信号を入力することで、劣化しやすいトランジスタのしきい値電圧のシフト及びオンしたトランジスタのしきい値電圧のシフトを抑制する。すなわち、高電位(VDD)がゲート電極に印加されているトランジスタを介して(若しくは抵抗成分を持つ素子を介して)、交流パルスを劣化しやすいトランジスタのゲート電極に加える構成を含んでいる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、現在実用化されている量産技術からの膜構成、プロセス条件、または生産装置等の変更が少なく、半導体装置に安定した電気特性を付与し、信頼性の高い半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、を有し、ゲート絶縁膜は、窒化酸化シリコン膜と、窒化酸化シリコン膜上に形成された酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された金属酸化膜と、を含み、金属酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

表示装置

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】表示部に複数の画素を有し、複数のフレーム期間で表示を行う液晶表示装置であって、フレーム期間は、書き込み期間及び保持期間を有し、書き込み期間において、複数の画素のそれぞれに、画像信号を入力した後、保持期間において、複数の画素が有するトランジスタをオフ状態にして、少なくとも30秒間、画像信号を保持させる。画素は、酸化物半導体層でなる半導体層を具備し、酸化物半導体層は、キャリア濃度が1×1014/cm3未満である。

(もっと読む)

半導体装置

【課題】新規な構成を有する半導体装置である。

【解決手段】第1の素子を有し、第2の素子を有し、トランジスタを有し、容量を有し、第1の素子の出力は、第2の素子の入力と電気的に接続され、第2の素子の出力は、第1の素子の入力と電気的に接続され、第1の素子の入力は、入力端子と電気的に接続され、第1の素子の出力は、出力端子と電気的に接続され、トランジスタのソース及びドレインの一方は、容量の一方の電極と電気的に接続され、トランジスタのソース及びドレインの他方は、入力端子と電気的に接続され、トランジスタのチャネル形成領域は、結晶を有する酸化物半導体を有する。結晶を有する酸化物半導体を有するトランジスタはリーク電流が非常に小さいため、データを保持することができる。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いた表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供する。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させること

ができる。

(もっと読む)

半導体装置、及びダイオード

【課題】酸化亜鉛を含む半導体膜を用いたダイオードを提供する。

【解決手段】基板上の、酸化亜鉛を含み、チャネル形成領域を有する半導体膜と、前記半

導体膜とゲート電極との間のゲート絶縁膜と、前記半導体膜と電気的に接続されるソース

電極及びドレイン電極と、を有し、前記ゲート電極は、前記ソース電極及び前記ドレイン

電極の一方と電気的に接続される。前記ゲート電極は前記チャネル形成領域の上又は下に

あり、前記ゲート電極は前記ソース電極及び前記ドレイン電極の上にあってもよい。

(もっと読む)

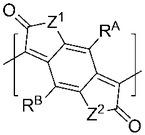

高分子化合物、該高分子化合物を含む薄膜及び組成物

【課題】両極性の有機トランジスタを簡便に製造しうる、p型とn型の両極性を示す高分子化合物を提供すること。

【解決手段】式

【化0】

(1)

〔式中、Z1は、−O−、−S−、−N(R1)−、−N(COR2)−又は−N(CO2R3)−を表す。Z2は、−S−、−N(R1)−、−N(COR2)−又は−N(CO2R3)−を表す。R1、R2及びR3は、それぞれ独立に、水素原子アルキル基、アリール基又はヘテロアリール基を表す。RA及びRBは、それぞれ独立に、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、ヘテロアリール基、ハロゲン原子又はシアノ基を表す。〕

で表される構成単位を含む高分子化合物。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置

を提供することを課題の一とする。

【解決手段】半導体層を酸化物半導体層とする逆スタガ型薄膜トランジスタを含む半導体

装置において、酸化物半導体層上にバッファ層を有する。バッファ層は、半導体層のチャ

ネル形成領域と、ソース電極層及びドレイン電極層とに接する。バッファ層は膜内に抵抗

分布を有し、半導体層のチャネル形成領域上に設けられる領域の電気伝導度は半導体層の

チャネル形成領域の電気伝導度より低く、ソース電極層及びドレイン電極層と接する領域

の電気伝導度は半導体層のチャネル形成領域の電気伝導度より高い。

(もっと読む)

表示装置

【課題】消費電力が抑制された表示装置を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、及び一対の電極を有する発光素

子を含む画素が複数設けられた画素部を有し、前記第1のトランジスタは、ゲートが走査

線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソー

スまたはドレインの他方が前記第2のトランジスタのゲートに電気的に接続され、前記第

2のトランジスタは、ソースまたはドレインの一方が電源線に電気的に接続され、ソース

またはドレインの他方が前記一対の電極の一方に電気的に接続され、前記第1のトランジ

スタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。そして、

前記表示装置が静止画像を表示する期間の間に、前記画素部に含まれる全ての走査線に供

給される信号の出力が停止される期間を有する。

(もっと読む)

半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出

力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有

するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を

用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極

又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持

することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

21 - 40 / 1,360

[ Back to top ]