Fターム[5F140AA06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | しきい値電圧の安定化 (713)

Fターム[5F140AA06]に分類される特許

201 - 220 / 713

半導体装置の製造方法

【課題】 閾値電圧の低い金属ゲート電極においてPMISFETの製造方法を提供する。

【解決手段】 半導体基板10上にPMISFETを作製する方法であって、半導体基板10上に絶縁膜20を形成する工程と、半導体基板10及び絶縁膜20をハロゲン化合物を含むガスにさらして、絶縁膜20上に吸着層110を形成する工程と、吸着層110上に金属を含むゲート電極40を形成して、吸着層110とゲート電極40を反応させて、吸着層110をハロゲン含有金属層にする工程とを有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜とゲート電極との間の界面層にカーボン層を導入して、低い閾値電圧を実現している例では、カーボン層中のカーボンはSi半導体基板中に入り、欠陥準位を形成するため、EWFが不安定であった。本発明は上記問題点を解決するためになされたもので、p−metalを用いたMIS型半導体装置において、EWFを安定して増加させることが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基10上に形成された絶縁膜20と、絶縁膜20上に形成され、且つ、CN基又はCO基を含む界面層30と、界面層30上に形成された金属層40とを備えて半導体装置を構成する。

(もっと読む)

半導体装置

【課題】メタル電極/high−kゲート絶縁膜からなるゲート構造において、半導体特性や信頼性の劣化をおこさせることなく、サイドウォールを形成したゲート構造を有する半導体装置の提供。

【解決手段】半導体基板1上に設けられた、high−k誘電体材料からなるゲート絶縁膜2と、ゲート絶縁膜2の上に設けられたメタル電極3と、メタル電極3の側壁を覆い、ゲート絶縁膜2を挟んで半導体基板1と対向配置された酸化防止膜4と、ゲート絶縁膜2と酸化防止膜4とを覆うように、半導体基板上に設けられたサイドウォール5とを含むゲート構造。

(もっと読む)

半導体装置

【課題】チャネル幅が狭い場合においても、eWFが十分に低減された閾値電圧が低い半導体装置を実現できようにする。

【解決手段】半導体装置は、素子分離領域102により分離された活性領域103を有する半導体基板101と、活性領域103の上に形成されたゲート絶縁膜111と、ゲート絶縁膜111の上に形成されたゲート電極121とを備えている。ゲート絶縁膜111は、シリコン及び酸素を除く第1の元素が拡散している。素子分離領域102は、第1の素子分離膜102Aと、第1の素子分離膜102Aよりもゲート絶縁膜111側に形成され且つ第1の素子分離膜102Aと比べて第1の元素が拡散しにくい第2の素子分離膜102Bとを有している。

(もっと読む)

半導体装置の製造方法

【課題】素子特性を劣化させることなく、しきい値電圧の低い、金属のゲート電極を有するPチャネルMOSトランジスタを備えた半導体装置を製造することを可能にする。

【解決手段】半導体領域2上にゲート絶縁膜5を形成するステップと、第1金属元素と、OH基、NOx(x=1,2)基のうち少なくとも一つを含有する酸素含有金属層6をゲート絶縁膜上に形成するステップと、酸素含有金属層上に第2金属元素を含むゲート電極膜7を形成するステップと、ゲート電極膜を形成した後、酸素含有金属層の熱分解反応或いは脱水反応が生じる温度以上に加熱するステップと、を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチの側壁部の上部における寄生トランジスタのしきい値電圧の低下を抑制する。

【解決手段】半導体装置は、半導体基板100におけるFET形成領域に形成されたMISトランジスタを備えている。半導体基板100に設けられたトレンチ104内に形成され、FET形成領域を区画するシリコン酸化膜107と、FET形成領域及びシリコン酸化膜107の上に形成されたゲート絶縁膜110と、ゲート絶縁膜110の上に形成されたゲート電極111とを備えている。ゲート絶縁膜110のうち、トレンチ104内に位置するゲート電極111と半導体基板100の側面との間に形成されている部分は、アルミニウムを含有している一方、ゲート絶縁膜110のうち、ゲート電極111と半導体基板100の上面との間に形成されている部分は、アルミニウムを含有していない。

(もっと読む)

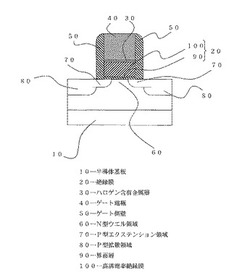

高誘電率ゲート絶縁膜を備えた電界効果トランジスタを有する半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜を用いるFET及びその製造方法において、閾値電圧の制御性を向上する。

【解決手段】基板101上に高誘電率ゲート絶縁膜110、その上にゲート電極111aを形成する。少なくともゲート電極111aをマスクとして基板101にN型不純物を導入し、N型イクステンション領域113を形成する。少なくともゲート電極111aをマスクとして、基板101におけるN型イクステンション領域113の下にP型不純物を導入し、P型ポケット領域114を形成する。N型イクステンション領域113に対するN型不純物のうちのAsの導入量を、当該Asと高誘電率ゲート絶縁膜110中の元素との結合によって生じる異常な短チャネル効果が実質的に抑制される臨界点以下である範囲に設定する。臨界点は、高誘電率ゲート絶縁膜110の膜厚に基づいて算出される。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率でありかつリーク電流を低減することが可能なゲート絶縁膜を備えた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板11上に設けられ、かつランタンアルミシリコン酸化物若しくは酸窒化物を含む第1の誘電体膜23と、第1の誘電体膜23上に設けられ、かつハフニウム(Hf)、ジルコニウム(Zr)、チタン(Ti)、及び希土類金属のうち少なくとも1つを含む酸化物若しくは酸窒化物を含む第2の誘電体膜24と、第2の誘電体膜24上に設けられた電極14とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】偏析不純物による仕事関数の制御の可能な半導体装置または半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10上に設けられた絶縁膜(HfSiON膜30)と、絶縁膜30上にフルシリサイド電極(NiSi51)と、フルシリサイド電極51に接するように、絶縁膜30とフルシリサイド電極51の間に設けられたバリア膜(SiOC膜40)と、を備え、SiOC膜40と接するフルシリサイド電極51の部分に、N型またはP型いずれかの不純物60が偏析し、SiOC膜40は、シリコン酸窒化膜の誘電率以下の誘電率を有し、以下の(a)、(b)および(c)を主成分として含み、((a)シリコン(Si)、(b)炭素(C)、(c)酸素(O)または窒素(N))、HfSiON膜30またはNiSiフルシリサイド電極51を構成する金属元素を主成分としてバリア膜の少なくとも内部に含まないもの。

(もっと読む)

半導体装置

【課題】半導体装置の実装時の特性値変動を従来よりも低減した、より高精度の特性を有する半導体装置を提供する。

【解決手段】特性値に影響の大きい対を形成したトランジスタ間の特性値変動、ここではK値の変動を等しくし、シフトを相殺する事でシフトを低減することが可能となる。希ガスのイオン注入などにより、MOSトランジスタ形成領域の結晶性を崩す。このことにより、対となったトランジスタ間でのシフトが同じになるため、結果的にパッケージング時の特性変化を低減することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜内に金属原子を拡散させるための膜の除去を容易にする。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に金属膜を形成する工程と、窒素ガス及び不活性ガスの少なくとも一方の雰囲気中で半導体基板、下地膜、ゲート絶縁膜及び金属膜を熱処理する工程と、ゲート絶縁膜上に残存する金属膜を除去する工程と、ゲート絶縁膜上に、ゲート電極膜を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】第1の加熱温度の第1の加熱処理により、ソース・ドレイン拡散層3のシリコンとソース・ドレイン拡散層上の第1の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜を形成し、素子分離絶縁膜の上の第1の金属膜の表面上に第1の金属よりも融点が高い高融点金属である第2の金属を堆積して、少なくとも第1の金属膜の表面を被覆するように第2の金属膜を形成し、第2の加熱温度の第2の加熱処理により、少なくとも第1の金属膜の表面を第2の金属膜と反応させて、合金膜106aを形成し、第1の加熱温度および第2の加熱温度よりも高い第3の加熱温度の第3の加熱処理により、シリサイド膜のシリコンの濃度を増加させ、合金膜、第1の金属膜の未反応部分、および、第2の金属膜の未反応部分を選択的に除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】N型トランジスタ、P型トランジスタともに低い閾値電圧が得られる半導体装置及びその製造方法を提供する。

【解決手段】基板上の第1領域201にN型トランジスタが形成され、前記基板上の第2領域202にP型トランジスタが形成された半導体装置101であって、前記基板111と、シリコンを含有する第1のゲート絶縁膜121と、第1の金属と酸素とを含有する第2のゲート絶縁膜122と、前記第1の金属と異なる第2の金属と酸素とを含有する第3のゲート絶縁膜123と、ハフニウムを含有する第4のゲート絶縁膜124と、金属と窒素とを含有するゲート電極層131とを備え、前記第2領域に形成された前記ゲート電極層の厚さは、前記第1領域に形成された前記ゲート電極層の厚さよりも厚くなっている。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成しつつ、半導体装置の生産性を向上することが可能な半導体装置の製造方法を提供する。

【解決手段】第1の圧力の不活性雰囲気中において、第1の加熱温度の第1の加熱処理により、ソース・ドレイン拡散層のシリコンとソース・ドレイン拡散層上の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜を形成し、第2の圧力の酸化性雰囲気において、第2の加熱温度の第2の加熱処理により、素子分離絶縁膜の上の金属膜の少なくとも表面を選択的に酸化して、金属酸化膜を形成し、第1の加熱温度および第2の加熱温度よりも高い第3の加熱温度の第3の加熱処理により、シリサイド膜のシリコンの濃度を増加し、素子分離絶縁膜上の金属酸化膜および金属膜の未反応部分を選択的に除去する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】n型MOSトランジスタ、p型MOSトランジスタにおいて共通のゲート絶縁膜構造及びゲート電極材料を用いながら、各々のトランジスタのしきい値電圧を適正な値へ設定し、且つゲート絶縁膜における酸素欠損に伴う移動度の低下を抑制する。

【解決手段】メタルゲート電極及び高誘電率ゲート絶縁膜を用いた半導体装置の製造方法であって、n型半導体領域200及びp型半導体領域300上にそれぞれ、シリコン酸化物からなる第1のゲート絶縁膜、La,Al,Oを含む第2のゲート絶縁膜、Hfを含む第3のゲート絶縁膜を積層し、その上に金属膜からなるゲート電極を形成し、次いでp型半導体領域300上の、第1のゲート絶縁膜,第2のゲート絶縁膜,第3のゲート絶縁膜,及びゲート電極の積層構造を、水素拡散防止膜350で被覆した後、水素雰囲気で熱処理を施す。

(もっと読む)

半導体装置とその製造方法

【課題】

メタルゲートを有するpチャネルMISトランジスタとメタルゲートを有するnチャネルMISトランジスタとを、少ない工程数で形成する。

【解決手段】

半導体装置は、シリコン層を有する半導体基板と、半導体基板に画定されたn型活性領域とp型活性領域と、n型活性領域の上方に形成され、酸化シリコンより高い誘電率を有し、表面にAlを含有する第1高誘電率ゲート絶縁膜と、p型活性領域の上方に形成され、酸化シリコンより高い誘電率を有する第2高誘電率ゲート絶縁膜と、第1高誘電率ゲート絶縁膜および第2高誘電率ゲート絶縁膜の各々の上に形成され、nチャネルトランジスタに適した仕事関数を有する金属又は金属化合物を含む材料で形成された、第1ゲート電極および第2ゲート電極と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 ハフニウムシリケートからなるゲート絶縁膜に、アルミナ膜を重ねると、等価酸化膜厚を薄くすることが困難になる。また、ハフニウムシリケートからなるゲート絶縁膜内にAlが拡散すると、正孔の移動度が低下してしまう。

【解決手段】 半導体基板(10)の上に、HfとOとを含む絶縁膜(16)を形成する。この絶縁膜の上に、構成元素として酸素とチタンとを含むキャップ膜(17)を形成する。絶縁膜及びキャップ膜を、窒素ガスまたは希ガス雰囲気中で熱処理し、キャップ膜中のチタンを絶縁膜内に拡散させることにより、ゲート絶縁膜(18)を形成する。ゲート絶縁膜の上に、ゲート電極膜(19)を形成する。

(もっと読む)

半導体装置

【課題】ゲートパルスストレスによる耐圧劣化およびしきい値電圧の変動を抑制できる半導体装置を提供する。

【解決手段】ゲート電極GEは、ソース領域およびドリフト領域DRに挟まれる領域上に絶縁層FOを介在して形成されている。フィールドプレートFPは、ゲート電極GEおよびドリフト領域DR上を延在し、かつゲート電極GEに電気的に接続されている。ダミー導電層DCは、フィールドプレートFPとドリフト領域DRとの間において絶縁層FO上に形成され、かつソース領域に電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の空乏化と、ゲート電極内の不純物量の減少ないしはバラつきと、イオンがゲート絶縁膜を突き抜けてしまうことに起因したゲート絶縁膜の信頼性低下及び閾値変動を抑制する。

【解決手段】第1注入工程(図1(b)、図1(c))と第2注入工程(図1(d)、図1(e))を備える。第1注入工程ではゲート絶縁膜5と、ゲート電極9、10となる膜6と、が形成された半導体基板1のゲート電極9、10となる部分に、n型又はp型の導電型のイオンを注入する。第2注入工程では、ゲート電極9、10に同じ導電型のイオンを注入する。第1注入工程で注入するイオンの質量は、第2注入工程で注入するイオンよりも大きくする。これにより第1注入工程による不純物の濃度分布の縦方向におけるピーク位置を、第2注入工程による不純物のピーク位置よりもゲート絶縁膜5寄りにする。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】化合物半導体と絶縁性材料との界面に形成される界面準位が低減した半導体装置を提供する。

【解決手段】閃亜鉛鉱型の結晶構造を有する3−5族化合物半導体と、3−5族化合物半導体の(111)面、(111)面と等価な面、または、(111)面もしくは(111)面と等価な面から傾いたオフ角を有する面に接する絶縁性材料と、絶縁性材料に接し、金属伝導性材料を含むMIS型電極とを備える半導体装置を提供する。

(もっと読む)

201 - 220 / 713

[ Back to top ]