Fターム[5F140AA06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | しきい値電圧の安定化 (713)

Fターム[5F140AA06]に分類される特許

161 - 180 / 713

半導体装置及びその製造方法

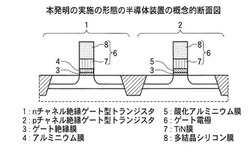

【課題】 半導体装置及びその製造方法に関し、高誘電率膜を用いた相補型トランジスタの実効仕事関数を調整して適切なしきい値電圧を実現する際に、エッチング工程数を低減するとともに、エッチングダメージの発生を回避する。

【解決手段】 nチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第1のゲート絶縁膜と第1金属ゲート電極との間にアルミニウム膜を設けるとともに、pチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第2ゲート絶縁膜と第2金属ゲート電極との間に酸化アルミニウム膜を設ける。

(もっと読む)

半導体装置の製造方法

【課題】金属ゲート電極/高誘電体ゲート絶縁膜構造のMISトランジスタを有する半導体装置を高性能化する。

【解決手段】シリコン基板1上に、順に、ハフニウムおよび酸素を主体とする高誘電体膜hk1と、第1金属および酸素を主体とし、化学量論的組成よりも多くの第1金属を含むpMIS用キャップ膜Cp1を形成する。その後、シリコン基板1に、第1熱処理と第2熱処理とを順に施す。続いて、pMIS用キャップ膜Cp1上にゲート電極用金属膜EM1を形成し、これらを加工することでpMIS用金属ゲート電極pG1とpMIS用高誘電率ゲート絶縁膜pI1とを形成する。特に、第1熱処理では高誘電体膜hk1中の余剰酸素を除去し、第2熱処理では高誘電体膜hk1中にpMIS用キャップ膜Cp1中の第1金属を拡散させる。第1熱処理は、第2熱処理よりも低い温度で施す。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高品質な特性を有する電界効果トランジスタ及びその方法を提供する。

【解決手段】素子分離領域106間のソース/ドレイン領域114、及びポケット領域116を含んでいる半導体基板102と、素子分離領域間の半導体基板の上面のトレンチ110内にあって、(100)面を有する底面及び上面と、2つ以上の平面を有する側面とを有するシリコンゲルマニウム層112と、ゲート絶縁層120、ゲート電極122、及びサイドスペーサ128を含むシリコンゲルマニウム層上のゲート構造と、ゲート構造によって覆われていないシリコンゲルマニウム層及び半導体基板の上部分上のメタルシリサイド124とを備え、シリコンゲルマニウム層は、チャネル長方向において、ゲート構造の下で側面を有していない。

(もっと読む)

MIS型半導体装置及びその製造方法

【課題】半導体集積回路のトランジスタのゲート絶縁膜を、安定な高誘電率絶縁膜で構成した、リーク電流が小さくしかも駆動力の大きい、MIS型半導体装置を提供する。また、閾値電圧のバラツキの小さい、量産可能で安価な高誘電率ゲート絶縁膜の製造方法を提供する。

【解決手段】アルミニウム酸化物層と、ジルコニウムまたはハフニウムのシリコン酸化物層とを積層した積層ゲート絶縁膜を用いたMIS型半導体装置。ジルコニウムまたはハフニウムのシリコン酸化物層を、導電チャネル側に設置する。

(もっと読む)

半導体装置およびその製造方法

【課題】NMISトランジスタとPMISトランジスタの閾値電圧を同時に低減できる半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板10に形成された第1の活性領域10a上に高誘電体を含む第1のゲート絶縁膜17aと、金属材料を含む第1のゲート電極18aとを形成し、基板10に形成された第2の活性領域10b上に高誘電体を含む第2のゲート絶縁膜17bと、金属材料を含む第2のゲート電極18bとを形成する工程と、第1のゲート絶縁膜17aの端部と第2のゲート絶縁膜17bの端部とに負の固定電荷を導入する工程と、第1のゲート絶縁膜17aの端部を除去する工程とを備えている。

(もっと読む)

窒化物系半導体電界効果トランジスタ

【課題】ノーマリオフ動作を達成し、十分なチャネル電流が得られ、かつ、しきい値電圧制御が容易な窒化物系半導体ヘテロ接合電界効果トランジスタを提供する。

【解決手段】GaN層10とAlGaN層11のヘテロ接合界面をチャネルとする電界効果トランジスタにおいて、負の電荷を有する第三の層40をゲート電極34下のゲート絶縁膜31中に設けるとともに、ヘテロ接合を形成する窒化物半導体内にフッ素イオンF−等の負のイオン41を注入する。第三の層40はCl−等の負のイオンが注入される。ゲート絶縁膜31中およびAlGaN層11中に適量の負のイオンを注入することにより、しきい値電圧が上がりノーマリオフ動作を確実に達成するとともに、十分なチャネル電流が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体絶縁膜及びメタルゲート電極を有する半導体装置において、高仕事関数を得ると共にNBTI信頼性劣化を低減する。

【解決手段】半導体装置100において、基板101上に、高誘電体ゲート絶縁膜109を介してメタルゲート電極110が形成されている。高誘電体ゲート絶縁膜109とメタルゲート電極110との界面におけるメタルゲート電極110の側に、ハロゲン元素が偏析している。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】高誘電率ゲート絶縁膜として機能するHf含有絶縁膜4a,4b上にメタルゲート電極であるゲート電極GE1,GE2が形成され、ゲート電極GE1,GE2は、金属膜7a,7b,7cの積層膜からなる金属膜7とその上のシリコン膜8との積層構造を有している。金属膜7の最下層の金属膜7aは、窒化チタン膜、窒化タンタル膜、窒化タングステン膜、炭化チタン膜、炭化タンタル膜または窒化タングステン膜からなり、金属膜7bは、ハフニウム膜、ジルコニウム膜またはアルミニウム膜からなり、金属膜7cは、金属膜7aと同種の材料からなる膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチゲート構造を有するトランジスタにおいて、サブスレッショルド特性を良好にする。

【解決手段】半導体装置100は、第1導電型のソース領域112およびドレイン領域113、これらの間に第2導電型のチャネル領域108が形成された基板102と、チャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162を埋め込むように形成されたゲート電極122とを有するトランジスタを含む。チャネル領域108において、基板102表面およびトレンチ162の底部には、それぞれ第2の高濃度領域132および第1の高濃度領域130が形成されており、第2導電型の不純物濃度がトレンチ162側方における第2導電型の不純物濃度よりも高くなっている。また、第1の高濃度領域130の第2導電型の不純物濃度が第2の高濃度領域132の第2導電型の不純物濃度以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】pMOSトランジスタにcSiGeとeSiGeを適用し、且つゲート絶縁膜におけるダメージ発生を防止でき、素子特性の向上及びしきい値制御性の向上をはかる。

【解決手段】pMOSトランジスタのチャネル部及びソース・ドレイン領域にSiGeを用いた半導体装置において、Si基板202上の一部に形成され、pMOSトランジスタのチャネルとなる第1のSiGe層205と、第1のSiGe層205上にゲート絶縁膜206を介して形成されたゲート電極208と、pMOSトランジスタのソース・ドレイン領域に埋め込み形成され、且つチャネル側の端部が基板表面よりも深い位置でチャネル側に突出するように形成された第2のSiGe層214と、第1のSiGe層205と第2のSiGe層214とを分離するように、基板の表面部でSiGe層205,214間に挿入されたSi層222とを備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、最適な仕事関数を有するメタルゲート電極を持つ半導体装置及びその製造方法に関する。

【解決手段】n チャネルMIS トランジスタを含む半導体装置であり、n チャネルMIS トランジスタは、基板上に形成されたp 型半導体領域、p 型半導体領域に形成されたソース領域102及びドレイン領域104、ソース領域102及びドレイン領域104間のp 型半導体領域上に形成されたゲート絶縁膜106、ゲート絶縁膜106上に形成された金属層108及び化合物層110からなる積層構造を持つゲート電極を有する。金属層108は2 nm未満の厚さ及び4.3 eV以下の仕事関数を有し、化合物層110は4.4 eVを越える仕事関数を有しかつAl及び金属層108とは異なる金属を含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易な手順で、高誘電率ゲート絶縁膜とメタルゲート電極とのゲートスタック構造を有する相補型トランジスタの閾値を調整する。

【解決手段】相補型トランジスタの第1導電型のトランジスタ(162)の閾値電圧を変化させる第1の調整用金属を第1導電型のトランジスタ(162)および第2導電型のトランジスタ(160)に同時に添加し、第2導電型のトランジスタ(160)のメタルゲート電極(110a)上から第1の調整用金属の拡散を抑制する拡散抑制元素を添加する。

(もっと読む)

半導体装置及びその製造方法

【課題】High-k/metalゲート電極構造において各極性のFETに要求される仕事関数値を実現する。

【解決手段】第1の領域と第2の領域とを有する半導体基板101の上にゲート絶縁膜103を形成する。次に、ゲート絶縁膜103の上に第1の金属窒化膜105を堆積する。次に、第1の金属窒化膜105における第2の領域に位置する部分を除去することにより、ゲート絶縁膜103における第2の領域に位置する部分を露出させる。次に、ゲート絶縁膜103における第2の領域に位置する部分の上に、第1の金属窒化膜105と同じ金属窒化物からなる第2の金属窒化膜107を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】閾値電圧が相対的に高い半導体装置のチャネル領域における不純物濃度を閾値電圧が相対的に低い半導体装置のチャネル領域における不純物濃度よりも高くすると、閾値電圧が相対的に高い半導体装置の駆動力の低下を招来する虞があった。

【解決手段】半導体装置は、第1のトランジスタと第2のトランジスタとを備えている。第1のトランジスタは、第1のチャネル領域3aと、第1のゲート絶縁膜4aと、第1のゲート電極5aと、第1のエクステンション領域8aとを有している。第2のトランジスタは、第1のトランジスタよりも高い閾値電圧を有しており、第2のチャネル領域3bと、第2のゲート絶縁膜4bと、第2のゲート電極5bと、第2のエクステンション領域8bとを有している。第2のエクステンション領域8bは浅接合化不純物を含んでおり、第2のエクステンション領域8bの接合深さは第1のエクステンション領域8aの接合深さよりも浅い。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】nチャネル型MISFETQnは、半導体基板1のp型ウエルPWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3aを介して形成されたゲート電極GE1を有し、pチャネル型MISFETQpは、n型ウエルNWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3bを介して形成されたゲート電極GE2を有している。ゲート電極GE1,GE2は、金属膜7とその上のシリコン膜8との積層構造を有している。Hf含有絶縁膜3aは、Hfと希土類元素とSiとOとNとからなる絶縁材料膜またはHfと希土類元素とSiとOとからなる絶縁材料膜であり、Hf含有絶縁膜3bは、HfとAlとOとNとからなる絶縁材料膜またはHfとAlとOとからなる絶縁材料膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】導電型に応じて容易に構成を変えることが可能なFinトランジスタ及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に設けられた凸状の半導体からなるトランジスタ活性領域104と、トランジスタ活性領域104の一部の側面上及び上面上に設けられたゲート絶縁膜105aと、ゲート絶縁膜105aを間に挟んでトランジスタ活性領域104の側面及び上面の一部上に設けられたゲート電極350とを備えている。ゲート電極350のうち、トランジスタ活性領域104の側面上に設けられた部分の構成とトランジスタ活性領域104の上面上に設けられた部分の構成とは互いに異なっている。

(もっと読む)

161 - 180 / 713

[ Back to top ]