Fターム[5F140AA06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | しきい値電圧の安定化 (713)

Fターム[5F140AA06]に分類される特許

121 - 140 / 713

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

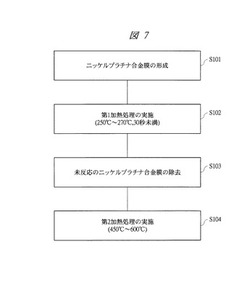

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

窒化物半導体装置

【課題】エンハンメント型GaN系HFETの閾値電圧のバラツキを低減する。

【解決手段】窒化物半導体装置80では、第2のリセスエッチングによりアンドープGaN層3の上部に突起部51が設けられる。突起部51上には、上部が第1のリセスエッチングにより形成されたアンドープAlGaN層4aが設けられる。積層部7は、アンドープGaN層3の突起部51、アンドープAlGaN層4a、及び絶縁膜5から構成される。トレンチ部8は、絶縁膜5、アンドープAlGaN層4a、及びアンドープGaN層3表面がリセスエッチングされたものである。積層部7及びトレンチ部8上にはゲート絶縁膜6が設けられる。ゲート絶縁膜6上には、トレンチ部8を覆うようにゲート電極33が設けられる。絶縁膜5はゲート絶縁膜6よりも膜厚が厚く設定されている。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、トランジスタ特性のばらつきが抑えられた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001と、半導体基板1001内に形成された第1導電型の第1の活性領域1003と、第1の活性領域1003上に形成された第1のゲート絶縁膜1030aと第1のゲート電極1032aとを有し、第1の活性領域1003上に形成された第1チャネル型の第1のMISFET1050とを備える。第1のゲート電極1032aは、第1のゲート絶縁膜1030a上に形成され、金属原子を含む第1の下部ゲート電極1011aと、炭素の単体を含む材料、または分子中に炭素を含む材料からなる第1の酸化防止膜1012aと、第1の上部ゲート電極1013aとを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】バリアメタルの膜厚を抑制しながらメタルゲートの拡散性材料が高誘電率誘電体に拡散することを防ぐ。

【解決手段】半導体装置がゲート積層体構造を含む。ゲート積層体構造は、半導体基板5の上に形成された界面層4と、界面層4の上に形成された高誘電率誘電体3と、拡散性材料と不純物金属を含み、高誘電率誘電体の上方に形成されたシリサイドゲート1と、拡散性材料に対するバリア効果を持ち、高誘電率誘電体3とシリサイドゲート1の間に形成されたバリアメタル2とを備えている。不純物金属は、シリサイドゲート1の拡散性材料が高誘電率誘電体に導入されることを防ぐことができるような、拡散性材料に対するバリア効果を有している。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタに適当なしきい値電圧が与えられる一方、抵抗素子はシリコン膜からなる抵抗体層の異常成長を抑制して、シリコン膜の膜厚を安定化する。

【解決手段】半導体装置は、半導体基板10の上部に形成された素子分離領域12によって囲まれた第1の活性領域10a、第1の活性領域の上に形成された第1の高誘電体膜14aを有する第1のゲート絶縁膜27a、及び第1のゲート絶縁膜の上に形成された第1のゲート電極28aとを有する第1導電型の第1のMISトランジスタ1aと、素子分離領域の上に形成された第2の高誘電体膜14x、及び該第2の高誘電体膜の上に形成されたシリコンからなる抵抗体層20xを有する抵抗素子1xとを備えている。第1の高誘電体膜と第2の高誘電体膜とは、互いに同一の高誘電体材料からなり、第1の高誘電体膜は第1の調整用金属を含み、第2の高誘電体膜は第1の調整用金属を含まない。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

半導体装置の製造方法

【目的】ゲート酸化膜の信頼性を確保しながらB(ボロン)の吸い出し現象やP(リン)のパイルアップ現象を補償して正常に動作するMOSFET素子を形成できる半導体装置の製造方法を提供する。

【解決手段】n型拡散層9の表面層にp型拡散層10を形成し、その後のゲート酸化膜11の形成により生じたB(ボロン)の吸い出し現象やP(リン)のパイルアップ現象を900℃以上の熱処理をすることで補償し、n型化したp型拡散層10の表面をp型に戻して、ゲート酸化膜11の信頼性を確保しながら、正常に動作するMOSFET素子を有する半導体装置の製造方法を提供することができる。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタにおけるシリコン混晶層からなるソースドレイン領域を、不純物の拡散による不具合を防止しながらチャネル領域に近づけることができるようにする。

【解決手段】半導体装置は、半導体基板10からなるn型の活性領域の上に、ゲート絶縁膜12を介在させて形成されたゲート電極13と、活性領域におけるゲート電極13の両側方の領域に形成されたp型ソースドレイン領域20と、活性領域における各p型ソースドレイン領域20の側面からそれぞれゲート電極13の下側に向かって形成されたn型ポケット領域18とを有している。p型ソースドレイン領域20は、シリコンとIV族元素との混晶層からなり、混晶層は、ゲート長方向におけるゲート電極側の側面がゲート電極側に突き出す凸部20aを有している。凸部20aの先端は、ポケット領域18によって覆われている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域の寄生抵抗の上昇を抑えつつ短チャネル効果の発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2中のゲート電極12の両側に形成され、ゲート電極12側にエクステンション領域161を有し、導電型不純物を含むソース・ドレイン領域16と、ソース・ドレイン領域16のエクステンション領域161のゲート電極12側の側面のみに接し、導電型不純物の半導体基板2中での拡散を抑制する性質を有する拡散抑制不純物を含む拡散抑制層15と、を有する。

(もっと読む)

二種類の仕事関数メタルを備える半導体装置

【課題】高誘電率ゲート絶縁膜を備える半導体装置の閾値電圧を適切に制御すること。

【解決手段】半導体装置の形成方法は、仕事関数メタルを含むダミーメタルゲート層をベース絶縁膜の直上に形成することと、アニーリングによって仕事関数メタルをベース絶縁膜中に拡散させることと、ウェットエッチングによってダミーメタルゲート層を除去することと、ベース絶縁膜211、212上に高誘電率ゲート絶縁膜213、213を形成することと、高誘電率ゲート絶縁膜213上にメタルゲート214、215を形成することと、を含む。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】ゲート電極構造の垂直方向の抵抗を低減する。

【解決手段】半導体基板1と、半導体基板1の上に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成された仕事関数制御層3と、仕事関数制御層3の上に形成された第1のシリサイド層4と、第1のシリサイド層4の上に形成されたポリシリコンゲート電極5と、ポリシリコンゲート電極5の下の半導体基板1中の領域を挟んで半導体基板1中に形成されるソース領域6およびドレイン領域7と、を有する半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法、pチャネルMOSトランジスタ

【課題】nチャネルMOSトランジスタにおいてhigh−Kゲート絶縁膜をhigh−K誘電体膜と酸化ランタン膜の積層により構成した半導体装置において、酸化ランタン膜のパターニングプロセスを不要とする半導体装置の製造方法を提供する。

【解決手段】界面酸化膜22上に形成されたhigh−K誘電体膜23上に酸化膜24を形成する工程と、前記high−K誘電体膜に窒化物層25を形成する工程と、前記窒化物層および前記酸化膜を第1の素子領域21Aから選択的に除去し、第1および第2の素子領域21Bにわたり酸化ランタン膜26を形成し、前記第1の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化ランタン膜を積層した第1の積層構造を、また前記第2の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化膜と前記窒化物層と前記酸化ランタン膜を積層した第2の積層構造を形成する工程と、を含む。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート閾値電圧を低下させることなく、チャネル移動度を向上できる炭化珪素MOSFETを提供する。

【解決手段】炭化珪素半導体装置200は、炭化珪素基板10と、炭化珪素基板10上に形成された炭化珪素層20と、炭化珪素層20上に形成されたゲート絶縁膜30と、ゲート絶縁膜30を介して炭化珪素層20上の所定位置に形成され、III族軽元素であるB、AlまたはGaをp型ドーパントとして含む多結晶シリコンからなるゲート電極40とを有する。そして、ゲート電極40中の上記p型ドーパントを、ゲート電極40直下の炭化珪素層20とゲート絶縁膜30との界面近傍に拡散させ、上記p型ドーパントによって界面近傍の不純物準位をパッシベーションする。

(もっと読む)

最適化されたチャンネル領域を有するMOSトランジスタを具備する半導体素子

【課題】 MOSトランジスタを備える半導体素子を提供する。

【解決手段】 半導体素子は、半導体基板の所定領域に形成されて活性領域を区画する素子分離膜を有する。第1活性領域9a及び第2活性領域9bは(100)面の中心上面9t及び中心上面9tから素子分離膜14に向けて延びる傾斜エッジ面9eを有する。第1活性領域9a及び第2活性領域9bの中心上面9t及び傾斜エッジ面9eは第1半導体パターン15a及び第2半導体パターン15bで覆われる。第1半導体パターン15a及び第2半導体パターン15bは中心上面9tに平行な(100)面の平坦な上面15t及び平坦な上面に実質的に垂直な側壁15sを有する。第1半導体パターン15a及び第2半導体パターン15bの上部を通って側壁に交差する方向に第1ゲートパターン26a及び第2ゲートパターン26bが配置される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ピラー型MOSトランジスタに関し、チャネルがフローティング状態になることを防止できる半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置200は、基板11に立設された、トランジスタ用の第一のピラー1と、前記第一のピラー1に隣接された、前記第一のピラー1のチャネル16と同じ導電型の連結部14と、前記第一のピラー1に連結部14を介して隣接された、前記チャネル16と同じ導電型の、前記第一のピラー1のチャネル16電位制御用の第二のピラー2と、を有し、前記第二のピラー2上面に、電位を与える構造を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】Geを含む半導体で構成されるチャネル領域を有するP型FETにおいて、逆短チャネル特性の発生を抑制しつつ、短チャネル特性を改善する。

【解決手段】半導体装置は、半導体基板100上に形成されたP型FETを備えている。P型FETは、半導体基板100上に形成され、Geを含有する第1の半導体層103と、第1の半導体層103上に形成され、第1の半導体層103よりも低濃度のGeを含有する第2の半導体層104と、第2の半導体層104上にゲート絶縁膜107aを間に挟んで形成されたゲート電極110aと、第2の半導体層104のうちゲート電極110aの両側方に位置する部分に形成されたp型エクステンション領域111aと、第1の半導体層103内に設けられ、且つp型エクステンション領域111aの下に形成されたn型不純物領域152とを有している。

(もっと読む)

121 - 140 / 713

[ Back to top ]