Fターム[5F140AA06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | しきい値電圧の安定化 (713)

Fターム[5F140AA06]に分類される特許

101 - 120 / 713

半導体装置及びその製造方法

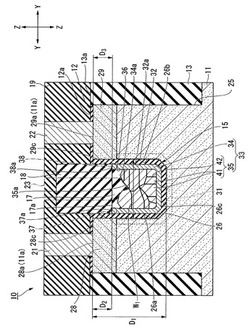

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】工数を大幅に増加せず且つ高誘電体からなるゲート絶縁膜にダメージを与えることがない、仕事関数変更用金属不純物膜の効果を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたp型活性領域110と、p型活性領域110の上に形成されたゲート絶縁膜150と、ゲート絶縁膜150の上に形成されたゲート電極106とを有している。ゲート絶縁膜150は、二酸化シリコンよりも大きい誘電率を有する高誘電体膜103と、高誘電体膜103の上に形成され、炭素を含む炭素含有膜104とを有している。高誘電体膜103及び炭素含有膜104は、第1の金属としてランタン又はマグネシウムを含み、ゲート電極106は、第2の金属を含む。

(もっと読む)

半導体装置の製造方法

【課題】キャップ材料を使用した半導体装置のウェハ面内における閾値電圧Vtのバラツキを抑制することを目的とする。

【解決手段】まず、半導体基板1001の上に、高誘電率ゲート絶縁膜1006及び第1のキャップ膜1008を順に形成する。次に、熱処理を行って、第1のキャップ膜1008中の第1の金属を高誘電体膜1006に拡散させる。その後、高誘電体膜1006に拡散せずに高誘電体膜1006の上に残存した第1のキャップ膜1008を除去して、第1の金属が拡散した高誘電率ゲート絶縁膜1006Aの上に金属電極1010を形成する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】低閾値動作が可能な電界効果トランジスタを提供する。

【解決手段】n型半導体領域2と、半導体領域に離間して形成されたソース領域およびドレイン領域12a、12bと、ソース領域12aとドレイン領域12bとの間の半導体領域上に形成され、シリコンと酸素を含む第1絶縁膜4と、第1絶縁膜上に形成され、Hf、Zr、Tiから選ばれた少なくとも1つの物質と酸素を含む第2絶縁膜8と、第2絶縁膜上に形成されたゲート電極10と、を備え、第1絶縁膜と第2絶縁膜との界面7aを含む界面領域7に、Geが導入されており、Geの面密度が、界面領域7内の第1絶縁膜4側においてピークを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な電気的特性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜20と、ゲート絶縁膜上に形成されたキャップ膜22と、キャップ膜上に形成されたシリコン酸化膜23と、シリコン酸化膜上に形成された金属ゲート電極24と、金属ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層48とを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】電界効果型トランジスタの閾値電圧を精度よく制御することができ、かつその範囲を広くする。

【解決手段】この半導体装置は、ゲート絶縁膜120及びゲート電極130を有する電界効果型トランジスタ101を備える。ゲート絶縁膜120は、界面層110と高誘電率膜112とを積層した構成を有している。高誘電率膜112は、酸化シリコンより誘電率が高い金属酸化物からなる。そしてゲート絶縁膜120は、高誘電率膜112と界面層110の界面近傍に、窒素を含有する窒素含有層を有している。窒素含有層は高誘電率膜112から界面層110に渡って形成されている。窒素含有層において、窒素の濃度は高誘電率膜112と界面層110の界面が最も高い。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ構造を有するMOSトランジスタにおいて、チャネル領域のしきい値の適切な調整が可能となる半導体装置を提供する。

【解決手段】第1導電型半導体基板に作られたゲート幅方向に深さが変化する凹部領域と凸部領域の前記凹部領域はトレンチ構造で形成されているトレンチ構造を有するMOSトランジスタにおいて、前記第1導電型半導体基板表面に沿って成膜した犠牲酸化膜を介して形成された第1導電型ドープドポリシリコン膜を前記凹部領域のトレンチ構造に埋め込ませて熱処理をおこなうことで、前記トレンチ構造間の凸部領域上面およびトレンチ構造の凹部領域側面と底面に不純物拡散する。これにより、トレンチピッチが縮小されてもチャネルへの均一な不純物添加が可能になる。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および電子装置

【課題】 高い閾値電圧と、低いオン抵抗とを両立可能であり、かつ、パラレル伝導を抑制できる電界効果トランジスタを提供する。

【解決手段】

基板601上に、III族窒化物のバッファ層602、チャネル層603、障壁層605、およびキャップ層606が、前記順序で積層され、

各半導体層の上面は、(0001)結晶軸に垂直なIII族原子面であり、

バッファ層602は、格子緩和され、

障壁層605は、引っ張り歪みを有し、

チャネル層603およびキャップ層606が圧縮歪みを有するか、または、チャネル層603が格子緩和され、キャップ層606が引っ張り歪みを有し、

障壁層605上の一部の領域に、キャップ層606、ゲート絶縁膜607、およびゲート電極608が、前記順序で積層され、他の領域に、ソース電極609とドレイン電極610が形成されていることを特徴とする電界効果トランジスタ。

(もっと読む)

電荷トラップを有するゲート誘電体を含む揮発性メモリ及びその製造方法

【課題】チャネルイオン注入領域のドーピング濃度を相対的に低下しながらも所望のしきい電圧値を得ることができる揮発性メモリを提供する。

【解決手段】ゲート誘電体として順次積層された下部ゲート誘電体、電荷トラップのための中間ゲート誘電体、及び上部ゲート誘電体を備えたセルトランジスタと、ゲート誘電体として単一層の酸化膜を備えたロジック用トランジスタとで、揮発性メモリを構成する。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】ゲート電極が金属窒化膜により構成されるMOSFETにおいて、電流駆動能力の向上を図る。

【解決手段】基板10に、素子形成領域20を分離する素子分離領域50を設ける。次に素子形成領域20上にゲート絶縁膜100を形成する。その後ゲート絶縁膜100上に金属窒化膜により構成される下部ゲート電極膜200を形成する。さらに下部ゲート電極膜200を熱処理する。そして下部ゲート電極膜200上に上部ゲート電極膜220を形成する。

(もっと読む)

デプレッション型MOSトランジスタ

【課題】閾値電圧ばらつきが少ないデプレッション型NチャネルMOSトランジスタを提供する。

【解決手段】デプレッション型NチャネルMOSトランジスタの、チャネル領域となる低濃度N型不純物領域の下に、同程度の濃度の低濃度P型不純物領域を形成し、低濃度N型不純物領域の深さばらつきを抑制する。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

金属窒化膜、該金属窒化膜を用いた半導体装置、および半導体装置の製造方法

【課題】所望の実効仕事関数(例えば、高い実効仕事関数)を実現し、かつ、EOTが変化しない、またはEOTの変化を低減した金属窒化膜、金属窒化膜を用いた半導体装置、および半導体装置の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る金属窒化膜は、TiとAlとNを含有し、該金属窒化膜のTiとAlとNのモル比率(N/(Ti+Al+N))が0.53以上であり、かつ、上記金属窒化物層のTiとAlとNのモル比率(Ti/(Ti+Al+N))が0.32以下であり、かつ上記金属窒化物層のTiとAlとNのモル比率(Al/(Ti+Al+N))が0.15以下である。

(もっと読む)

アルミニウムドープゲートを備えるプログラマブルIII−窒化物トランジスタ

【課題】アルミニウムドープゲートを有するプログラマブルIII−窒化物トランジスタを提供する。

【解決手段】第1のIII−窒化物材料104と第2のIII−窒化物材料106との界面に形成される2次元電子ガスを有する導電チャネルを含むIII−窒化物ヘテロ接合デバイスにおいて、ゲート接点140の下に形成されるゲート絶縁層112が導電チャネルの上方に配置され、接点絶縁層112は界面における2次元電子ガスの形成を変更する。接点絶縁層112はAlSiN又はアルミニウムがドープされたSiNとすることができる。接点絶縁層112はIII−窒化物ヘテロ接合デバイス160の閾値電圧をプログラミングしてデバイスをエンハンストモードデバイスにする。

(もっと読む)

半導体装置の製造方法

【課題】FIN状の半導体部により構成されるFIN型トランジスタを有する半導体装置において、FIN状の半導体部の上面の不純物濃度と側面の不純物濃度との差を小さくすることにより、FIN型トランジスタの特性ばらつきを抑えて、信頼性を向上させる。

【解決手段】

FIN状の半導体部10の上面に2〜5nm程度の厚さのパッド絶縁膜3を形成し、FIN状の半導体部10の一方の側面に、第1注入角度θ1を有する斜め方向からクラスタイオンを注入した後、FIN状の半導体部10の他方の側面に、第1注入角度θ1と対称の第2注入角度θ2を有する斜め方向からクラスタイオンを注入する。その後、FIN状の半導体部10に注入されたクラスタイオンを活性化して、ソース領域およびドレイン領域の一部を構成する拡散領域を形成する。

(もっと読む)

膜厚測定用標準試料、その製造方法、膜厚測定方法および半導体装置の製造方法

【課題】膜厚測定に用いる標準試料中のLaを含む膜の保管時の安定性を向上させる。

【解決手段】膜厚測定用標準試料100は、シリコン基板101上に設けられたLa含有膜103およびLa含有膜103の上部に設けられてLa含有膜103を覆うとともに金属窒化物を含む保護膜105を含む。これにより、Laを含む膜103の保管時の変質による膜厚変動を効果的に抑制する。このような膜厚測定用標準試料100を用いて、Laを含む膜の膜厚の測定値を補正するステップを含む、膜厚測定方法。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコンゲート電極の意図しないフルシリサイド化を防止する。

【解決手段】基板17上に、ゲート絶縁膜12およびシリコン層10をこの順に積層した積層体(10、12)を形成する工程と、積層体(10、12)の側壁沿いにSiN膜を有するオフセットスペーサ13を形成する工程と、その後、シリコン層10の上面を、薬液を用いて洗浄する工程と、その後、少なくともシリコン層10の上面を覆う金属膜19を形成する工程と、その後、加熱する工程と、を有し、オフセットスペーサ13が有するSiN膜は、ALD法を用いて450℃以上で成膜されたSiN膜、または、1Gpa以上の引張/圧縮応力を有するSiN膜であり、前記薬液は、重量比率で、HF/H2O=1/100以上であるDHF、または、バッファードフッ酸である半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの閾値電圧のバックゲート電圧依存性を低減することができる。

【解決手段】半導体装置100は、基板(例えば、P型半導体基板3)と、基板に形成され素子形成領域1を他の領域と分離する素子分離領域2と、を有している。更に、素子形成領域1上に形成されたゲート電極4を有し、ゲート電極4は、素子分離領域2において素子形成領域1を介して互いに対向する第1及び第2領域2a、2bの上にそれぞれ延伸している。更に、ゲート電極4を基準としてチャネル長方向Dに相互に離間するように素子形成領域1に形成された一対の拡散領域(例えば、N型拡散領域5)を有する。第1領域2a及び第2領域2bの上面の少なくとも一部分ずつは、素子形成領域1の上面よりも下に、チャネル幅Wの5%以上の深さに凹んでおり、それら凹み7内にもゲート電極4の一部分ずつが存在している。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

101 - 120 / 713

[ Back to top ]