Fターム[5F140AA06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | しきい値電圧の安定化 (713)

Fターム[5F140AA06]に分類される特許

61 - 80 / 713

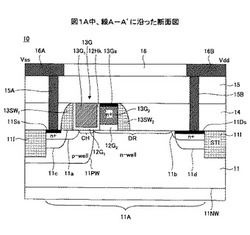

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】nチャネル型MISFET用のメタルゲート電極であるゲート電極GE1とpチャネル型MISFET用のダミーゲート電極GE2とを形成してから、nチャネル型MISFET用のソース・ドレイン領域とpチャネル型MISFET用のソース・ドレイン領域をそれぞれ形成する。その後、ダミーゲート電極GE2を除去し、ダミーゲート電極GE2が除去されたことで形成された凹部にpチャネル型MISFET用のメタルゲート電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数やコストを増加させることなく、信頼性の高い高耐圧pチャネル型トランジスタが形成された半導体装置を提供する。

【解決手段】主表面を有し、かつ内部にp型領域を有する半導体基板SUBと、p型領域PSR上であって主表面に配置された、ドレイン電極DRを取り出すための第1のp型不純物領域PRを有するp型ウェル領域PLDと、主表面に沿う方向に関してp型ウェル領域PLDと接するように配置された、ソース電極SOを取り出すための第2のp型不純物領域PRを有するn型ウェル領域NWRと、主表面に沿う方向に関して、第1のp型不純物領域PRと第2のp型不純物領域PRとの間に配置されたゲート電極GEと、n型ウェル領域NWRの上に配置された、主表面に沿って延びるp型埋め込みチャネルPPRとを含んでいる。上記n型ウェル領域NWRとp型ウェル領域PLDとの境界部は、ゲート電極GEの、第1のp型不純物領域PRに近い側の端部よりも、第1のp型不純物領域PRに近い位置に配置される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置及びその製造方法

【課題】閾値電圧調整用金属を含む高誘電率絶縁膜を有するゲート絶縁膜を備えたn型MISトランジスタを有する半導体装置において、ゲート幅が狭くなっても、n型MISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】n型MISトランジスタnTrは、半導体基板1における素子分離領域32に囲まれた活性領域1aと、活性領域1a上及び素子分離領域32上に形成され且つ高誘電率絶縁膜12aを有するゲート絶縁膜13aと、ゲート絶縁膜13a上に形成されたゲート電極16aとを備えている。活性領域1aにおける素子分離領域32に接する部分のうち少なくともゲート絶縁膜13aの下側に位置する部分に、n型不純物領域28が形成されている。

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

【課題】半導体デバイスを提供する。

【解決手段】理論的な金属:酸素化学量論比を有する高kゲート誘電体、前記高kゲート誘電体の上部に設置された、Mを遷移金属として、組成がMxAlyで表されるアルミナイドを含むNMOS金属ゲート電極、および前記高kゲート誘電体の上部に設置された、アルミナイドを含まないPMOS金属ゲート電極、を有するCMOS半導体デバイス。

(もっと読む)

半導体装置及びその製造方法

【課題】NBTIを改善することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたn型ウェル領域102と、n型ウェル領域102上に形成され、ゲート絶縁膜104と、下部ゲート電極105、及び下部ゲート電極105上に形成された上部ゲート電極106を含むゲート電極120とを有するpチャネル型MISトランジスタとを備える。下部ゲート電極105は、結晶粒界を有する多結晶の金属窒化物で構成されており、当該結晶粒界には金属窒化物を構成する元素とは異なる元素が偏析されている。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電圧の閾値電圧がばらつくことを抑制することができると共に、チャネル抵抗を低減させることができる半導体装置を提供する。

【解決手段】ベース領域4、ソース領域6、ドレイン領域7の不純物濃度を均一とし、第1、第2トレンチ8a、8bをベース領域4よりも浅く形成する。このような半導体装置では、ベース領域4、ソース領域6、ドレイン領域7の不純物濃度が均一とされているため、ゲート電圧の閾値電圧がばらつくことを抑制することができ、また、ソース領域6およびドレイン領域7を深くすることによりチャネル領域を有効に活用でき、チャネル抵抗を低減することができる。さらに、第1、第2トレンチ8a、8bをベース領域4より浅く形成しているため、ベース領域4のうち第1、第2トレンチ8a、8bより深く形成されている部分にはチャネル領域が形成されず、ソース領域6から深さ方向に電流が流れることを抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】CMOSトランジスタにおいて、ボロンの染み出しを抑制して閾値電圧を安定させると共に、ノイズを低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】CMOSトランジスタをシリコン基板1上に備える半導体装置であって、

シリコン基板1上に設けられ、窒素とフッ素とを含有するシリコン酸化膜からなるゲート酸化膜5と、ゲート酸化膜5上に設けられ、ポリシリコンからなるゲート電極7、8と、を有し、ゲート酸化膜5中のゲート電極7、8近傍の位置に窒素濃度のピークがあり、ゲート酸化膜5とシリコン基板1との界面付近の窒素濃度は0.5atom%以下であり、ゲート酸化膜5中におけるフッ素濃度は1atom%以上であり、当該フッ素によりゲート酸化膜5とシリコン基板1との界面のダングリングボンドが終端化されている。

(もっと読む)

半導体装置、及びその製造方法

【課題】高品質な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成される半導体領域、半導体領域内に形成され、互いに分離されているソース領域及びドレイン領域、半導体領域内に形成され、ソース領域及びドレイン領域を分離するチャネル領域、チャネル領域上に形成され、1×1019atoms/cm2よりも大きいピーク濃度で、Si、O、またはNとは異なる少なくとも一つの要素を有する界面酸化層、及び界面酸化層上に形成され、実質的に界面酸化層に隣接する深さでhigh―k/界面酸化層接合面を有するhigh―k絶縁層を有するMOS(metal-oxide-semiconductor)トランジスタを備え、少なくとも一つの要素のピーク濃度の少なくとも一つの深さは、実質的にhigh―k/界面酸化層接合面よりも下に位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】金属電極と該金属電極の上に形成されたシリコン電極とを有するゲート電極を備えた電界効果型トランジスタを実現する際に、金属電極とシリコン電極との界面に生じる界面抵抗を低減できるようにする。

【解決手段】半導体装置は、半導体基板100における第1の活性領域103aに形成されたP型の電界効果型トランジスタを備えている。第1の電界効果型トランジスタは、第1の活性領域103aの上に形成された第1のゲート絶縁膜106aと、第1のゲート絶縁膜106aの上に形成された第1のゲート電極115aとを有している。第1のゲート電極115aは、第1のゲート絶縁膜106aの上に形成された第1の金属電極107aと、該第1の金属電極107aの上に形成された第1の界面層110aと、該第1の界面層110aの上に形成された第1のシリコン電極111aとを有している。

(もっと読む)

ゲート電極及びその製造方法

【課題】フラットバンド電圧を制御できるとともに、半導体デバイス製造プロセスで使用される高温に曝されても特性の劣化が少ない、nMOSFETのゲート電極を与える。

【解決手段】炭化タンタルにイットリウムを添加した材料でゲート電極を作成する。このゲート電極はイットリウムの添加量に従ってフラットバンド電圧を調節できるとともに、600℃程度の熱処理を受けても特性の劣化が少ない。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、ゲート絶縁膜の一方の側のみに、容易に、かつ精度良く、バーズビークを形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】斜めイオン注入により、マスク膜にイオンを注入することで、シリコン酸化膜及びシリコン窒化膜を介して、ゲート絶縁膜の第1の側面と第1の不純物拡散領域の上面とで構成される角部に形成されたマスク膜のエッチング速度を、他の部分に形成されたマスク膜よりも速くし、次いで、ウエットエッチングにより、角部に形成されたマスク膜を選択的に除去して、シリコン窒化膜の表面の一部を露出させ、次いで、ウエットエッチングにより、マスク膜から露出されたシリコン窒化膜を選択的に除去して、シリコン酸化膜の表面の一部を露出させ、その後、熱酸化法により、ゲート絶縁膜の第1の側面側にバーズビークを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】生産性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、シリコン基板101と、同一のシリコン基板101上に設けられたN型トランジスタ200およびP型トランジスタ202と、を備え、N型トランジスタ200およびP型トランジスタ202は、Hfを含む高誘電率ゲート絶縁膜108と、高誘電率ゲート絶縁膜108上に設けられたTiN膜110と、を有しており、N型トランジスタ200は、シリコン基板101と高誘電率ゲート絶縁膜108との間に、La添加SiO2膜109aを有しており、P型トランジスタ202は、高誘電率ゲート絶縁膜108とTiN膜110の間に、N型トランジスタ200と同じ仕事関数調整用元素を含有するLa添加SiO2膜109bを有する。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−SiO2の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】チャネル移動度と閾値電圧とのトレードオフの関係を打破し、チャネル移動度を向上させ、かつ、閾値電圧の低下を抑えた炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】この発明に係る炭化珪素半導体装置1aの製造方法は、炭化珪素エピタキシャル層6を有する炭化珪素基板2の炭化珪素エピタキシャル層6上に、リンをドープした多結晶珪素膜18を形成する工程と、多結晶珪素膜18を熱酸化してゲート絶縁膜12を形成する工程と、を備えた。

(もっと読む)

拡散防止膜の形成方法及び半導体装置の製造方法

【課題】 拡散防止膜の形成方法及び半導体装置の製造方法に関し、閾値調整元素の拡散等による閾値電圧の変動の防止と製造工程の簡素化を両立する。

【解決手段】 Siを含有しない高誘電率酸化膜に窒素を導入したのち第1加熱処理を行う工程と、前記窒素を導入したSiを含有しない高誘電率酸化膜の上にSi含有半導体層を堆積させる工程と、第2加熱処理によって前記Si含有半導体層中のSiを前記窒素を導入したSiを含有しない高誘電率酸化膜中に拡散する工程とを設ける。

(もっと読む)

61 - 80 / 713

[ Back to top ]