Fターム[5F140AA06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | しきい値電圧の安定化 (713)

Fターム[5F140AA06]に分類される特許

21 - 40 / 713

半導体装置および半導体装置の製造方法

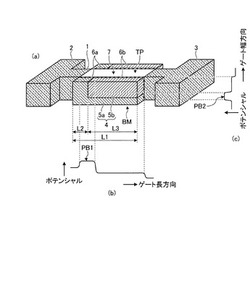

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】閾値電圧のバラつきを抑制する溝トランジスタを提供する。

【解決手段】図1に示すように、表面に少なくとも一つ以上の溝部250を有している半導体基板40と、溝部250の側壁を覆うように形成されたゲート絶縁膜20と、溝部250に埋めこまれているゲート電極10と、半導体基板40の表面に形成され、ゲート電極10を介して互いに対向しているソースおよびドレイン150と、を含み、溝部250の側壁には、複数の凸凹100が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】歩留まりを向上可能な半導体装置の製造方法および半導体装置を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、半導体基板上に形成される検査用トランジスタおよび製品用トランジスタのソースおよびドレインを活性化させるアニール処理を行うアニール工程と、アニール工程後における検査用トランジスタのゲート、ソースおよびドレインをシリサイド化させる検査用サリサイド工程と、検査用サリサイド工程後における検査用トランジスタの特性を測定する測定工程と、測定工程によって測定された特性と所望の特性との差分とに基づいて製品用トランジスタの特性を所望の特性へ近付ける特性調整アニール処理を行う特性調整アニール工程と、特性調整アニール工程後における製品用トランジスタのゲート、ソースおよびドレインをシリサイド化させる本サリサイド工程とを含む。

(もっと読む)

半導体装置

【課題】微細CMOSと中高耐圧MOSFETとの混載を前提とする集積回路(半導体装置)において、中高耐圧MOSFETのチャネル長やしきい値電圧のばらつきを抑制して、設計仕様どおりの安定した回路動作の実現や出力電流密度の向上を図ることができる技術を提供する。

【解決手段】本発明における特徴は、チャネル領域CHの幅(チャネル長)を小さくしたことにある。具体的には、ゲート電極Gと平面的に重なるチャネル領域CHの幅をLとし、ゲート電極Gの厚さをtとした場合、チャネル領域CHの幅Lが、ゲート電極Gの厚さtの1/5倍以上1倍以下になるようにチャネル領域CHを形成する。これにより、チャネル領域CHの幅Lを小さくすることができ、しきい値電圧のばらつきを小さくすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ダミーゲート電極の除去により形成されたゲート溝へのゲート電極材料の埋め込み性を改善することにより、適切な閾値電圧を持つ電界効果型トランジスタを備えた半導体装置を容易に実現できるようにする。

【解決手段】ゲート電極111bは、それぞれ金属又は導電性金属化合物からなる第1導電膜108b、第2導電膜109b及び第3導電膜110bが下から順に形成された積層構造を有し、ゲート電極111aは、第2導電膜109a及び第3導電膜110aが下から順に形成された積層構造を有する。第1導電膜108bの仕事関数と第2導電膜109a、109bの仕事関数とは異なっている。第1導電膜108bは板状に形成されており、第2導電膜109a、109bは凹形状に形成されている。

(もっと読む)

半導体装置及びその駆動方法

【課題】閾値電圧(Vth)の経時的に変動する現象を抑制することで、高信頼性を保つことが可能なMIS型半導体装置を提供する。

【解決手段】本発明は、半導体ボディ領域とゲート絶縁膜の間に半導体ボディ領域とは逆の半導体極性のチャネル層を有するMIS型半導体装置であり、当該半導体装置のフラットバンド電圧Vfbを−10ボルト以下とすることにより、半導体ボディ領域表面近傍に誘起されるキャリア電荷密度を当該半導体装置の動作保証範囲内において所定量以下に抑制する。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETのしきい値を調整する目的でLaなどが導入された高誘電率膜を含むゲート絶縁膜と、その上部のメタルゲート電極との積層構造を有する半導体装置において、ゲート電極のゲート幅を縮小した際、基板側からメタルゲート電極の底面に酸化種が拡散してnチャネル型MISFETの仕事関数が上昇することを防ぐ。

【解決手段】HfおよびLn含有絶縁膜5bとその上部のメタルゲート電極である金属膜9との間に、酸化種の拡散を防ぐためにAl含有膜8cを形成する。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板(1a,1b)の活性領域(1c,1d)が素子分離絶縁膜(2,6a)で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極(8a,8b)、ソース・ドレイン領域及び被覆応力膜を有するNTrとPTrを有し、活性領域におけるゲート長方向が<100>方向であり、素子分離絶縁膜としてNTrにおけるソース・ドレイン領域の両端部に第1の引張応力膜6aが形成され、ソース・ドレイン領域の両端部以外に第1の圧縮応力膜2が形成され、PTrの素子分離絶縁膜は第1の圧縮応力膜2が形成され、被覆応力膜としてNTrに第2の引張応力膜が形成され、PTrに第2の圧縮応力膜が形成されている構成とする。

(もっと読む)

エンハンスメント型III−V族高電子移動度トランジスタ(HEMT)および製造方法

【課題】ノーマリオフ型、すなわちエンハンスメント型トランジスタであるIII族窒化物HEMTを提供する。

【解決手段】エンハンスメント型高電子移動度トランジスタ(HEMT)400はIII−V族半導体412上に位置するIII−V族バリア層414を含むヘテロ接合416、およびIII−V族バリア層414上に形成され、P型III−V族ゲート層452を含むゲート構造462を具える。P型III−V族ゲート層452によりゲート構造462下での2次元電子ガス(2DEG)の発生を防ぐ。エンハンスメント型HEMT400を製造する方法は、基板402を設け、基板402にIII−V族半導体412を形成し、III−V族半導体412上にIII−V族バリア層414を形成し、III−V族バリア層414上にP型III−V族ゲート層452を含むゲート構造462を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】チャネル移動度の低下を抑制しつつ閾値電圧を制御する炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の炭化珪素半導体装置の製造方法は、(b)二酸化珪素膜が形成された炭化珪素基板を窒化処理する工程と、(c)窒化処理された炭化珪素基板を水蒸気を含んだ酸素雰囲気で熱処理する工程とを備える。工程(c)は、(c1)窒化処理された炭化珪素基板を投入した熱処理炉の温度を不活性ガス雰囲気中で昇温又は降温する工程を含む。工程(c1)は、窒化処理直後のチャネル移動度をμch、昇温又は降温開始時刻をt=0、熱処理開始時刻をt=t1、熱処理終了時刻をt=t2、熱処理炉からの基板取出時刻をt=t3、ボルツマン定数をk、時刻tにおける熱処理炉の温度をT(K)とした場合に、式(1)により求められる炭化珪素基板中のチャネル移動度の低下率が10%以下となるように昇温速度及び/又は降温速度を決定する。

(もっと読む)

仮想ボディ・コンタクト型トライゲート

【課題】FETデバイスにおける閾値電圧をより良く制御できるデバイスの提供。

【解決手段】基板101と、基板101の上のSiGe層103と、SiGe層上の半導体層105と、基板、SiGe層及び半導体層に隣接した絶縁層109aと、絶縁層に隣接した一対の第1のゲート構造体111と、絶縁層上の第2のゲート構造体113とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び導体層の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体が、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】安定に動作する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置は、基板11内に形成された第1導電型のウェル13と、ウェル13上にゲート絶縁膜17を介して配置されるゲート電極18と、ゲート電極18を挟んで基板11内に対向して配置される第2導電型のソース領域15及びドレイン領域16と、基板11内にソース領域15と隣接して配置され、ウェル1に電気的に接続される第1導電型のウェルタップ19と、ウェル13とウェルタップ19とに接し、ウェル13よりも不純物濃度が高く、第1導電型を有するポケット領域20と、を備える。

(もっと読む)

高有効仕事関数で電極を堆積する方法

【課題】半導体処理の方法が提供される。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】二重金属ゲートを有する構造体において金属膜の仕事関数を調整する為の改善した方法および半導体素子を提供する。

【解決手段】半導体素子は単一金属膜に対し、NMOSにおいてはフッ素、PMOSにおいては炭素をそれぞれ選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極108’、109’を有する。

(もっと読む)

半導体装置、半導体装置の製造方法、基板処理システムおよびプログラム

【課題】閾値電圧が上昇するのを防止または抑制でき、フラットバンド電圧が低下するのを防止または抑制できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜30と、ゲート絶縁膜上に形成されたTiN膜41と、TiN膜41上に形成されたTiAlN膜43と、TiAlN膜43上に形成されたシリコン膜45と、を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】リーク電流および閾値を低減させるゲート絶縁膜を提供する。

【解決手段】図1に示すように、半導体基板1上に、ゲート絶縁膜3を形成するゲート絶縁膜形成工程と、ゲート絶縁膜3上に、ゲート電極4を形成するゲート電極形成工程と、を備え、ゲート絶縁膜形成工程は、第1金属の酸化膜あるいは酸窒化膜を、成膜する第1の成膜工程と、第1金属の酸化膜あるいは酸窒化膜上に第2金属または、その酸化物を成膜する第2の成膜工程と、第2金属を第1金属の酸化膜中に拡散させるために熱処理する熱処理工程の3工程を含む。

(もっと読む)

プラズマ窒化処理方法、プラズマ窒化処理装置および半導体装置の製造方法

【課題】選択的に窒化物膜を形成する。

【解決手段】処理容器2内に窒素含有ガスを供給し、処理容器2内の圧力を133Pa以上1333Pa以下の範囲内に設定して、処理容器2内に窒素含有プラズマを生成し、該窒素含有プラズマによって、シリコンを含有する第2の部分100Bの表面100Baを窒化させずに、タングステンを含有する第1の部分100Aの表面100Aaを選択的に窒化して、第1の部分100Aの表面100Aaに窒化タングステン膜107を形成する。

(もっと読む)

半導体素子の製造方法

【課題】基板内のトランジスタ特性のばらつきを改善することができる半導体素子の製造方法を提供する。

【解決手段】半導体基板11,21の所定領域に、トランジスタのソース/ドレイン接合を形成するためのイオン注入S/D IMPを行うステップと、半導体基板11,21上の位置に依存するトランジスタ特性の偏差を補償するように、ソース/ドレイン接合の一部に追加の補償イオン注入CO IMPを行うステップとを含む。局部的にイオン注入が行われるように、基板11,21の平面に平行なX方向にイオンビームをスキャンする領域11Aと、基板11,21に平行であり、X方向にほぼ直交するY方向にイオンビームをスキャンする領域11Aとを設定した後、X方向のスキャン速度、Y方向のスキャン速度、又はX方向のスキャン速度及びY方向のスキャン速度を調整して、補償イオン注入CO IMPを行ってもよい。

(もっと読む)

21 - 40 / 713

[ Back to top ]