Fターム[5F140AA40]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 工程の簡略化 (489)

Fターム[5F140AA40]に分類される特許

141 - 160 / 489

フレームフリー湿式酸化

【課題】フレームフリー湿式酸化を提供すること。

【解決手段】半導体表面の湿式酸化で用いるための水は、超純粋水素および超純粋酸素を火炎を生じることなく反応させることによって生成することができる。火炎を用いないので、“トーチ”の石英成分に影響を与える火炎による混入は問題ではない。水のフレームフリー生成は、水素および酸素を、発火させない条件下で反応させることによって行なう。これは、水素分子が貴ガスまたは窒素などの希釈剤と混合されている希薄水素流を与えることによって行なうことができる。この希薄水素の使用は、爆発の危険も減少させるしまたはなくする。これは、複雑なインターロック、火炎検出器等の必要性をなくすことにより、装置設計を簡単にすることができる。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成しつつ、半導体装置の生産性を向上することが可能な半導体装置の製造方法を提供する。

【解決手段】第1の圧力の不活性雰囲気中において、第1の加熱温度の第1の加熱処理により、ソース・ドレイン拡散層のシリコンとソース・ドレイン拡散層上の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜を形成し、第2の圧力の酸化性雰囲気において、第2の加熱温度の第2の加熱処理により、素子分離絶縁膜の上の金属膜の少なくとも表面を選択的に酸化して、金属酸化膜を形成し、第1の加熱温度および第2の加熱温度よりも高い第3の加熱温度の第3の加熱処理により、シリサイド膜のシリコンの濃度を増加し、素子分離絶縁膜上の金属酸化膜および金属膜の未反応部分を選択的に除去する。

(もっと読む)

半導体装置の製造方法

【課題】面方位が(110)面あるいはこれと等価な面であるシリコン層上に形成する酸化膜厚の制御を行うことのできる半導体装置の製造方法を提供すること。

【解決手段】面方位が(110)面あるいはこれと等価な面であるシリコン基板1表面の一部に、リンのイオン注入を行って、端部の不純物濃度が連続的に変化した第1の不純物領域2Aを形成する工程と、熱酸化を行って、シリコン基板1上に端部の厚さが連続的に変化したシリコン酸化膜3を形成する工程と、を含むこと、を特徴とする。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は、半導体基板に第1導電型不純物イオンを注入して第1ウェルを形成する段階、半導体基板に第2導電型不純物を注入して、第1ウェルの一領域と重なる拡張されたドレインを形成する段階、半導体基板に第2導電型不純物を注入して、拡張されたドレイン下部の半導体基板内に、第1ウェルの他の領域と重なるようにして第1導電型の第2ウェルを形成する段階、拡張されたドレインと一部重なる第1ウェル上にゲートを形成する段階、及びゲートの一側における拡張されたドレイン領域に第2導電型不純物を注入してドレイン領域を形成する段階と、を含む。

(もっと読む)

垂直置換ゲートトランジスタと集積可能な容量の構造及び作製法

【課題】垂直MOSFETデバイス及び容量に関連したプロセス及び構成を提供する。

【解決手段】半導体デバイスは半導体材料の第1の層と、第1の層中に形成された第1のソース/ドレイン領域を有する電界効果トランジスタを含む。チャネル領域は、第1の層上に形成され、第2のソース/ドレイン領域235はチャネル領域上に形成される。集積回路構造は底部プレート266、誘電体層258及び最上部容量プレート259を有する容量を更に含む。作製方法において、電界効果トランジスタのソース領域及びドレイン領域から成るグループから選択された第1のデバイス領域が、半導体層上に形成される。第1の電界効果トランジスタゲート領域265が、第1のデバイス領域上に形成される。間にはさまれた誘電体層を有する最上部及び底部層も、半導体層上に形成される。別の実施例において、容量層は半導体層中に形成された溝又は窓内に形成される。

(もっと読む)

半導体装置の製造方法

【課題】Pt残留物、Pt汚染物あるいはPt膜を効果的にエッチングし、且つ、エッチング装置の金属部材の腐食進行を抑制することができる半導体装置の製造方法を提供する。

【解決手段】シリコンを含む半導体基板1上または半導体基板1上に形成されたシリコンを含む導電膜4上に、貴金属膜または貴金属を含む金属膜を形成する工程(a)と、工程(a)の後、半導体基板1に対して熱処理を行い、半導体基板1上または導電膜4上に貴金属を含むシリサイド膜7を形成する工程(b)と、工程(b)の後、第1の薬液を用いて未反応の貴金属を活性化する工程(c)と、第2の薬液を用いて工程(c)で活性化された未反応の貴金属を溶解する工程(d)とを行う。工程(d)は、工程(c)から30分以内に行う。

(もっと読む)

ホウ素ドープ半導体ナノワイヤ及びその製造方法

【課題】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤ及びその製造方法を提供する。

【解決手段】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤは、次の工程を含む製造方法により製造できる。

工程(1):半導体原料ガスを用いて、基板上にIV族半導体ナノワイヤを成長させる;

工程(2):ジボランガスのみを導入することにより、前記半導体ナノワイヤの表面にホウ素膜を堆積させる;

工程(3):表面にホウ素膜を堆積させた前記ホウ素膜付き半導体ナノワイヤを、半導体ナノワイヤ(本体)の融点以下の温度で熱アニールする。

(もっと読む)

処理装置

【課題】 被処理体に存在する少なくとも2層の積層膜に対しウェットエッチングによる除去処理を行う際に、エッチング選択性の問題が生じず、十分なエッチング速度で2層をエッチング除去することができる処理装置を提供すること。

【解決手段】 第1処理液を収容部2内の被処理体Wに供給して第1の膜に接触させ、第1の膜のエッチングを進行させる第1処理液供給部15と、第1処理液とは状態が異なる第2処理液を収容部2内の被処理体Wに供給して第2の膜に接触させ、第2の膜のエッチングを進行させる第2処理液供給部17と、第1の膜の除去状態を検出する検出部31と、検出部31の検出値に基づいて、第1の膜が除去されたと判断した場合に、切り換え部13に、処理液を第1処理液から第2処理液に切り換える指令を送信する制御部32とを具備し、検出部31は、被処理体Wに接触した第1処理液の所定物質の濃度を測定する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

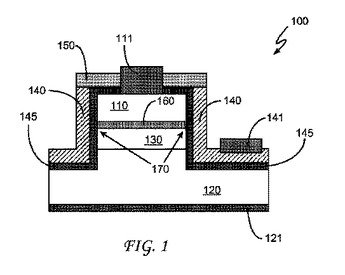

トンネル電界効果トランジスタ及びその製造方法

トンネル電界効果トランジスタ(TFET)は、ソース領域(110、210)、ドレイン領域(120、220)、ソース領域とドレイン領域との間のチャネル領域(130、230)、及びチャネル領域に隣接するゲート領域(140、240)を含む。ソース領域は、第1のIII族材料と第1のV族材料とを有する第1の化合物半導体を含み、チャネル領域は、第2のIII族材料と第2のV族材料とを有する第2の化合物半導体を含む。ドレイン領域は、第3のIII族材料と第3のV族材料とを有する第3の化合物半導体を含む。  (もっと読む)

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置、光ディスク装置

【課題】電流利得のばらつきを低減することができる半導体装置を提供する。

【解決手段】第1導電型の半導体基体1と、この半導体基体1の表面の一部に形成された、バイポーラトランジスタの第2導電型のコレクタ層2と、このコレクタ層2の一部に形成された、バイポーラトランジスタの第1導電型のベース層6と、このベース層6の一部に形成された、バイポーラトランジスタの第2導電型のエミッタ層7と、このエミッタ層7の直下の領域を除いた部分の半導体基体1に形成された、第1導電型の半導体層9とを含む半導体装置を構成する。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを高選択的に除去することのできる半導体装置の製造方法を提供すること。

【解決手段】半導体装置1の製造工程において、シリコン基板2上にゲート絶縁膜8を形成し、このゲート絶縁膜8上にダミーゲート32を形成する。ダミーゲート32の側面には、サイドウォール10を形成する。サイドウォール10の形成後、ダミーゲート32を被覆する第1絶縁層17を形成し、第1絶縁層17の表面がダミーゲート32の表面と面一となるように加工する。第1絶縁層17の加工後、ダミーゲート32に、ダミーゲート32とサイドウォール10とのエッチング選択比を確保可能なエッチング液を供給することにより、ダミーゲート32をウェットエッチングする。そして、ダミーゲート32のエッチングにより現れるゲート絶縁膜8上に、金属材料からなるゲート電極9を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】nMOS及びpMOSの双方において低い閾値電圧を実現することができ、製造コストが低い半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上の全面にシリコン酸窒化膜5を形成し、シリコン酸窒化膜5上にランタン酸化膜6を形成し、pMOS領域RpMOSからランタン酸化膜6を除去する。次に、全面に高誘電率膜である窒化ハフニウムシリケイト膜7を形成し、アルミニウム含有窒化チタン膜8を形成し、ポリシリコン膜9を形成し、これらの積層膜をゲート電極形状に加工する。次に、ソース・ドレイン領域12及び13に不純物を導入し、これらの不純物を活性化させるアニール処理を利用して、アルミニウム含有窒化チタン膜8中に含まれるアルミニウムを、pMOS領域RpMOSにおけるシリコン酸窒化膜5と窒化ハフニウムシリケイト膜7との界面まで拡散させる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】結晶欠陥が少なく結晶性の高い単結晶シリコン層が絶縁膜上に形成されてなる半導体装置の製造方法及び半導体装置を得るという課題があった。

【解決手段】基板1の一面1aに絶縁膜2を形成する工程と、絶縁膜2を開口して基板1を露出させる穴2cを形成する工程と、穴2cの内壁面を覆うように結晶成長補助膜3を形成する工程と、穴2cを充填するとともに、絶縁膜2の前記基板と反対側の面2aを覆うように非結晶シリコン層を形成する工程と、前記非結晶シリコン層を、レーザーアニール法により単結晶シリコン層5とする工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法

【課題】微細化された3次元的なデバイスを実現し得る、半導体装置の製造方法を提供する。

【解決手段】開示される、本発明の一実施形態による、半導体装置の製造方法によれば、ライン・アンド・スペース状の第2の層12を、第2の層12が延在する方向と交わる方向に延びるライン・アンド・スペース状の第8の層25をマスクとしてエッチングすることにより、二次元的に配列される第2の層12を得、これにより下地層をエッチングすることにより、二次元的に配列されるピラーを形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】複数回の露光処理によりゲート加工を行う半導体装置の製造方法に関し、工程数の増加等の問題を抑制する。

【解決手段】端部同士が隙間を挟んで対向する少なくとも一対のゲート電極を形成する半導体装置の製造方法であって、当該方法では、基板(111)上に、ゲート絶縁膜(112)とゲート電極層(113X)とを形成し、前記ゲート電極層上に形成された第1のレジスト(202)又は第1の反射防止膜(201)をマスクとして、前記ゲート電極層を加工することにより、前記ゲート電極層を、前記隙間が形成される領域から除去して、前記ゲート電極層に穴(121)を形成し、前記穴が形成された前記ゲート電極層上に形成された第2のレジスト(302)又は第2の反射防止膜(301)をマスクとして、前記ゲート電極層を加工することにより、前記ゲート電極層から、前記端部同士が前記隙間を挟んで対向する前記少なくとも一対のゲート電極(113)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスにおいてフォトレジスト構造等の追加工程を必要としない、非対称なDSS構造の半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上にゲート絶縁膜21を介して形成されたゲート電極22と、ゲート電極22の側面に形成されたオフセットスペーサ13、23と、一方のオフセットスペーサ23の側面に形成されたゲート側壁27と、半導体基板2中のゲート絶縁膜21下に形成されたチャネル領域25と、半導体基板2内のチャネル領域25を挟む領域に形成され、チャネル領域25側に導電型不純物が偏析して形成されたエクステンション領域24aを有するソース・ドレイン領域24と、ソース・ドレイン領域24上にオフセットスペーサ13に接して形成されたシリサイド層16、及び、ゲート側壁27に接して形成されたシリサイド層26と、を有した半導体装置1とする。

(もっと読む)

半導体装置、その製造方法および固体撮像装置

【課題】本発明は、gmの低下を抑制し、gds、gmbを維持して、MOSトランジスタの高性能化を可能とする。

【解決手段】半導体基板11上にゲート絶縁膜12を介して形成されたゲート電極13と、前記ゲート電極13のソース側の前記半導体基板11に形成されたエクステンション領域14と、前記ゲート電極13のソース側の前記半導体基板11にエクステンション領域14を介して形成されたソース領域16と、前記ゲート電極13のドレイン側の前記半導体基板11に形成されたLDD領域15と、前記ゲート電極13のドレイン側の前記半導体基板11にLDD領域15を介して形成されたドレイン領域17を有し、前記エクステンション領域14は前記LDD領域16よりも濃度が高く、前記LDD領域16よりも浅く形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】バルク基板を用いてもショートチャネル効果の抑制を効果的に発揮することができるFinFET構造を有する半導体装置及びその製造方法を得る。

【解決手段】Si基板1上にSiCエピタキシャル層2が形成され、SiCエピタキシャル層2の突出部2t上にSiエピタキシャル層3が形成される。突出部2t及びSiエピタキシャル層3は共に第1の方向に延びて、一方向延在形状を呈している。Siエピタキシャル層3の上面上及び両側面上には酸化膜8,窒化膜9及びゲート酸化膜20が形成される。酸化膜8,窒化膜9及びゲート酸化膜20を介して、Siエピタキシャル層3の上面上及び側面上にゲート電極G2が形成される。

(もっと読む)

141 - 160 / 489

[ Back to top ]