Fターム[5F140AA40]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 工程の簡略化 (489)

Fターム[5F140AA40]に分類される特許

101 - 120 / 489

半導体デバイスの製造方法および半導体デバイス

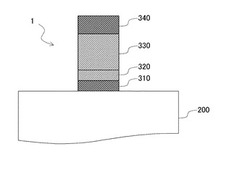

【課題】下地膜の結晶性の影響を抑え、高誘電率の結晶構造としたキャパシタ絶縁膜とする。

【解決手段】基板200の上に形成された結晶質膜310の上に非晶質膜320を形成する非晶質膜形成工程と、非晶質膜320の上に結晶質膜310の結晶構造とは独立して制御される結晶構造を持つ絶縁膜330を形成する結晶性絶縁膜形成工程と、を有する。結晶性絶縁膜形成工程においては、基板200を加熱して前記絶縁膜330の少なくとも一部を正方晶系へ相転移させる相転移工程と、を有する。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

静電気保護素子及びその製造方法

【課題】リーク電流の少ない静電気保護素子を提供する。

【解決手段】半導体基板100nと、半導体基板内に形成され、第1の導電型の不純物が拡散された第1のウェル101と、第1のウェル内に、第1のウェルの一部の領域を挟んで形成され、第2の導電型の不純物が拡散されたコレクタ領域110及びエミッタ領域112と、第1のウェル内に、前記エミッタ領域と分離する第1の分離領域102を挟んで形成され、第1のウェル内に拡散された不純物の濃度よりも高い濃度の、第1の導電型の不純物が拡散されたベース拡散領域114と、前記エミッタ領域下方から前記エミッタ領域と前記ベース拡散領域との間までの第1のウェル内の領域に形成され、第2の導電型の不純物が拡散された拡散領域103aとを備えた静電気保護素子。

(もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

単結晶ゲルマニウムまたはシリコンゲルマニウムを形成する方法

【課題】基板中に形成されたトレンチ中に、単結晶のゲルマニウムまたはシリコンゲルマニウムを形成する改良された方法を提供する。

【解決手段】誘電体分離3(例えばSTI)を有する基板1を準備する工程と、基板材料1(例えばSi)のトレンチエッチング4を行う工程と、トレンチ4内への充填層5(例えばGe)の選択成長を行う工程と、略溶融温度での充填層6の加熱により、充填層5(例えばGe)の再結晶化7により達成される。

(もっと読む)

半導体装置、半導体装置の製造方法および基板処理装置

【課題】低コストで必要な仕事関数及び耐酸化性を有する金属膜を備えた半導体装置を提供する。

【解決手段】基板上に形成された絶縁膜と、絶縁膜に隣接して設けられた金属膜と、を有し、金属膜は、第1の金属膜と第2の金属膜との積層構造を有しており、第1の金属膜は第2の金属膜よりも耐酸化性が高い物質で構成され、第2の金属膜は4.8eVよりも高い仕事関数を有する第1の金属膜とは異なる物質で構成され、第1の金属膜は第2の金属膜と絶縁膜との間に設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを集積する場合に製造工程数の削減を実現できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、アクティブ領域11を横断しゲート電極10Aよりも長さが短いゲート電極10Bを形成する工程と、ゲート電極10A,10Bをマスクとして、アクティブ領域11に不純物を斜めイオン注入することにより、ゲート電極10Aのゲート長方向両側の領域に互いに連続しない不純物拡散領域20a,20bを形成するとともに、ゲート電極10Bのゲート長方向両側の一方の領域から他方の領域に亘って連続する不純物拡散領域20g,20hを形成する斜めイオン注入工程とを含む。

(もっと読む)

制御されたアニールによる炭化シリコンパワーデバイスの製造方法

【課題】深いp型注入領域から浅いn型注入領域を囲む炭化シリコンの表面への好ましい拡散が可能な高性能炭化シリコン・パワーデバイスを製造する。

【解決手段】炭化シリコン基板の表面に開口部を確定し、その開口部を通して炭化シリコン基板内にp型ドーパントを深いp型注入領域を形成する注入エネルギー及び注入量で注入し、その開口部を通して炭化シリコン基板内にn型ドーパントを深いp型注入領域と比較して浅いn型注入領域を形成する注入エネルギー及び注入量で注入する。深いp型注入領域を横方向へ浅いn型注入領域を囲む炭化シリコン基板の表面まで拡散させるのに十分で、深いp型注入領域を縦方向に浅いn型注入領域を通って、炭化シリコン基板の表面まで拡散させることがないように、深いp型ドーパントと浅いn型ドーパントを1650℃未満だが好ましくは約1500℃よりも高い温度で約5分から約30分の間だけアニールする。

(もっと読む)

半導体素子加工方法

【課題】本発明は、微細半導体素子の加工方法にかかわり、特に、通常high-k/メタルゲートと呼ばれる構造の素子の微細化に適した加工方法に関する。

【解決手段】Si基板上に形成されたHfあるいはZrを含む絶縁膜とその上層あるいは下層あるいは膜中に存在するMg,YあるいはAlとを含む堆積膜の除去を、ドライエッチングとウエットエッチングを、ウエットエッチングを先にして少なくとも1回繰り返して行う。

(もっと読む)

半導体装置の製造方法

【課題】高耐圧な半導体装置の製造方法を提供する。

【解決手段】半導体層に対してマスクを用いて選択的にイオン注入を行い、半導体層に第1導電型の第1の半導体領域と、前記第1の半導体領域よりも第1導電型不純物濃度が低い第1導電型の第2の半導体領域とを同時に形成する工程と、第1の半導体領域上に第2導電型のソース領域を形成する工程と、第2の半導体領域上であってソース領域との間にゲート電極を挟む位置に第2導電型のドレイン領域を形成する工程と、半導体層におけるゲート電極とドレイン領域との間の表層部にドレイン領域に接しドレイン領域よりも不純物濃度が低い第2導電型のドリフト領域を形成する工程とを備えている。

(もっと読む)

気体感応型の半導体装置

【課題】気体感応型の半導体装置を、補償の手間を少なくする、簡単で確実な信号形成および信号評価に関して改良する。

【解決手段】ゲート電極、および/または、このゲート電極を半導体チャネルから絶縁するゲート絶縁層、および/または、ゲート電極と半導体チャネルとの間に設けられるゲートスタック層が2つの面セクションを有し、この2つの面セクションは、複数の気体に対して異なる感度を有する。

(もっと読む)

シリサイドの形成方法及び半導体装置

【課題】 ウェット洗浄工程を増加させることなく、かつ、より低温でシリサイドを形成することが可能なシリサイドの形成方法を提供すること。

【解決手段】 表面にシリコンとシリコン酸化物とが露出している基板101上にシリサイドを形成するシリサイドの形成方法であって、基板101の温度を400℃以上として、シリコンとシリコン酸化物とが露出している基板101の表面上にマンガン有機化合物ガスを供給し、基板101の表面に露出したシリコンを選択的にマンガンシリサイド化する。

(もっと読む)

絶縁膜形成方法、絶縁膜形成装置及び半導体装置

【課題】半導体基板に対し簡易な手法により均質な絶縁膜を高速に形成できるようにする。

【解決手段】絶縁膜形成装置1は、堆積部10の電子ビーム蒸着源12からハフニウム金属の原子線を照射して、基板70のシリコン酸化膜72上に液体状のハフニウム微粒子73を堆積させて堆積状態とし、照射部20のプラズマ源22から窒素原子、活性窒素分子及び窒素イオンでなる活性粒子74を照射することにより、表面に窒化ハフニウムシリケート膜76を形成すると共にシリコン酸化膜72をシリコン酸窒化膜75に変化させ、基板70を成膜状態とする。この結果絶縁膜形成装置1は、基板70へのハフニウム微粒子73の堆積処理及び窒素プラズマでなる活性粒子74の照射処理を行うことにより、高誘電率ゲート絶縁膜として機能し得る窒化ハフニウムシリケート膜76を短時間で容易に形成することができる。

(もっと読む)

半導体装置の耐圧シミュレーション方法およびシミュレーション装置

【課題】シミュレータの解析領域を縮小した場合であっても計算結果を保証し得る半導体装置の耐圧シミュレーション方法およびかかるシミュレーション方法を実行するシミュレーション装置を提供する。

【解決手段】

半導体装置に含まれるn型領域およびp型領域と同一の不純物濃度を有するnpn構造若しくはpnp構造を含む接合構造に対して一次元シミュレーションを行って、半導体装置における空乏層についての一次元シミュレーション値を取得する。少なくとも1つのpnジャンクションを含む半導体装置の一部である対象領域について、一次元シミュレーション値を用いて多次元シミュレーションを行って、対象領域内のpnジャンクションを逆バイアスしたときの対象領域内部における一次元シミュレーション値に基づく空乏層のエッジ位置を算出する。空乏層のエッジ位置が対象領域内の所定位置に達したときの対象領域への印加電圧を半導体装置の耐圧と推定する。

(もっと読む)

トレンチDMOSトランジスタの製造方法

トレンチDMOSトランジスタの製造方法であって、半導体基板上に酸化物層及びバリア層を形成するステップと、トレンチを形成するために、酸化物層及び半導体基板をエッチングするステップと、トレンチの内壁にゲート酸化物層を形成するステップと、バリア層上にポリシリコン層を形成し、トレンチを充填するステップと、トレンチゲートを形成するために、ポリシリコン層をエッチバックするステップと、バリア層及び酸化物層を除去するステップと、拡散層を形成するために、トレンチゲートの両側の半導体基板内にイオンを注入するステップと、拡散層上をフォトレジスト層で覆い、ソース/ドレイン配置を定義するステップと、拡散層内にイオンを注入するステップと、トレンチゲートの両側に側壁を形成するステップと、拡散層及びトレンチゲート上に金属シリサイド層を形成するステップとを含む。低コスト及び改善された製造効率を伴う効果的な結果が達成される。  (もっと読む)

(もっと読む)

電界効果トランジスタの製造方法

【課題】高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタの製造方法を実現する。

【解決手段】誘電性絶縁部層2’によって被覆されているバルクシリコンウエハ基板1’上に島状の各活性エリア10を互いに隣り合うようにそれぞれ設定する。バルクシリコンウエハ基板1’の表面上において、各活性エリア10を電界効果トランジスタの本体領域をフィン部3、5の形状で突出するように露出させて形成するために、誘電性絶縁部層2’を厚さ方向にエッチバックして絶縁体層2を形成する。上記本体領域に、チャネル領域部、上記チャネル領域部上のゲート誘電体8、ゲート誘電体8上のゲート電極4、および、ゲート電極4の自己整合マスクにより、チャネル領域部とは反対の伝導性型である不純物原子のドープによりソース領域部5およびドレイン領域部3を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】同一の半導体基板上に、高性能な低電圧MISFET、高信頼なMONOS型不揮発性メモリおよび高電圧MISFETを形成する。

【解決手段】ロジック回路などに使用される低電圧MISFETの形成領域において、キャップ酸化膜をマスクにすることによってダミーゲート電極上にシリサイドが形成されるのを防ぎ、ダマシンプロセスを用いて低電圧MISFETのゲートをhigh−k膜18およびメタルゲート電極20で形成する際の形成工程を簡略化する。また、ダミーゲート電極除去時のRIEによりダメージを受けたゲート絶縁膜を一旦除去し、新たにゲート酸化膜17を形成することで素子の信頼性を確保する。

(もっと読む)

高ゲルマニウム濃度のSiGeストレッサの形成方法

【課題】SiGeストレッサの形成方法と集積回路のトランジスタ構造を提供する。

【解決手段】SiGeストレッサを形成する方法であって、前記方法は、ソース領域とドレイン領域間にチャネルを有する半導体基板上のソース領域とドレイン領域の少なくとも1つに第1SiGe層を堆積するステップ、及び前記第1SiGe層の上部を酸化層に変換し、前記第1SiGe層の底部を第2SiGe層に変換するステップを含み、前記第2SiGe層は、前記第1SiGe層より高いGe濃度を有する方法。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】 極浅拡散層を形成することが可能な半導体装置の製造方法及び半導体製造装置

を提供することを目的とする。

【解決手段】

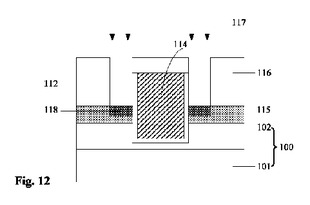

半導体基板100表面をアモルファス化することにより半導体基板100表面にアモル

ファス層111を形成するアモルファス層形成工程と、ドーパントを含むガス雰囲気中で

半導体基板100にマイクロ波を照射することにより、アモルファス層111にドーパン

トを拡散させるとともにドーパントの活性化を行い、半導体基板100に拡散層112を

形成する拡散層形成工程と、を具備する。

(もっと読む)

半導体素子およびその製造方法

【課題】半導体素子の低オン抵抗化を実現し、全体の製造工程数を低減する半導体素子およびその製造方法を提供すること。

【解決手段】ソース・ドレイン領域を形成する際のイオン注入時に、低耐圧横型トレンチMOSFETでは、ドレイン形成用の開口部がトレンチ側壁から離れ、ソース形成用の開口部がトレンチ側壁に達し、トレンチ横型パワーMOSFETでは、ソース形成用の開口部がトレンチ側壁から離れ、ドレイン形成用の開口部がトレンチ側壁に達するパターンのマスクを用いる。このマスクを用いて、高ドーズ量および低加速電圧で行うイオン注入と、低ドーズ量および高加速電圧で行うイオン注入を連続して行うことによって、低耐圧横型トレンチMOSFETのLDD領域と、トレンチ横型パワーMOSFETのLDD領域とを同時に形成する。

(もっと読む)

101 - 120 / 489

[ Back to top ]