Fターム[5F140AB01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 複合(回路要素) (3,149) | MOSIC、MISIC (2,326)

Fターム[5F140AB01]の下位に属するFターム

E/EMOS、E/DMOSを構成するもの (22)

CMOSを構成するもの (1,656)

Fターム[5F140AB01]に分類される特許

161 - 180 / 648

半導体装置及び半導体装置の製造方法

【課題】半導体装置全体としてみたとき、微細化によるチップ面積の減少を図りつつ、各素子に必要とされる特性を維持・向上させる。

【解決手段】半導体装置は、FinFET10と、FinFET10と同一のチップ上に設けられたPlanarFET20とを具備する。PlanarFETの第2ゲート絶縁層24は、FinFET10の第1ゲート絶縁層14よりも厚い。

(もっと読む)

半導体装置及びその製造方法

【課題】内部回路の誤動作を誘発させない保護回路を有する半導体装置を提供する。

【解決手段】P型Si基板101と、ESD保護素子1Aと、被保護素子1Bとを備えた半導体装置1であって、ESD保護素子1Aは、ソースN型拡散領域107Aと、P型Si基板101内においてソースN型拡散領域107Aを覆い、ソースN型拡散領域107Aの下方から少なくともゲート電極106Aの下方の一部まで形成され、P型Si基板101の基本領域よりもP型不純物濃度が高い高濃度P型拡散領域103とを備え、被保護素子1Bは、ドレインN型拡散領域108Bと、P型Si基板101内においてドレインN型拡散領域108Bと接する低濃度P型拡散領域104とを備え、ESD保護素子1Aのドレイン電極112Aと被保護素子1Bのドレイン電極112Bとが接続され、高濃度P型拡散領域103は、低濃度P型拡散領域104よりもP型不純物濃度が高い。

(もっと読む)

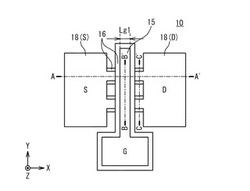

半導体装置

【課題】小型の静電破壊保護トランジスタを有する半導体装置を提供する。

【解決手段】第1導電型の半導体層12に、ゲート絶縁膜13を介して形成されたゲート電極14と、ゲート電極14のゲート幅方向Yに沿って形成された第2導電型の第1不純物拡散層15と、ゲート幅方向Yに沿って第1不純物拡散層15と対向配置された本体部16aと、本体部16bからゲート電極14と反対側に突出した複数の凸部16bとを有し、ゲート電極14のゲート長方向Xの幅Wd1が第1不純物拡散層15のゲート長方向Xの幅Ws1より大きい第2導電型の第2不純物拡散層16と、を備えた絶縁ゲート電界効果トランジスタ17を具備する。

(もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ分離構造を有する半導体装置においてトランジスタのドレイン電流の減少などを防止する。

【解決手段】半導体基板10の主表面に活性領域11を分離するトレンチ埋込材21を備え、この埋込材の表面を、少なくとも半導体基板10に接する部分で半導体基板10の主表面より所定高さ落ち込むように形成する。

(もっと読む)

半導体装置

【課題】トランジスタ本来の特性を出すことが可能な配線パターンの第1配線層を有する半導体装置を提供する。

【解決手段】半導体基板10の表面に延在し、所定間隔を有して交互に配置されたソース領域20及びドレイン領域30と、該ソース領域20又は該ドレイン領域30とコンタクトホール60、60aを介して接続されたフィンガー状の配線75、75a、75bを複数含む第1配線層70、70aと、該第1配線層70、70aとスルーホール80、80aを介して接続された第2配線層90とを有する半導体装置であって、前記第1配線層70、70aは、前記スルーホール80、80aが形成されないスルーホール非形成領域74、74a、74bの配線幅が、前記スルーホール80、80aが形成されるスルーホール形成領域73、73a、73bの配線幅よりも広い前記フィンガー状の配線75、75a、75bを含む。

(もっと読む)

半導体装置

【課題】電流特性の低下を防ぐ半導体装置を提供する。

【解決手段】nチャネル型の横型IGBT10では、N-エピタキシャル層4とはpベース11を介在させて隔てられているP+拡散層12と、エミッタ領域としてのN+拡散層13とには、金属シリサイド層9aが形成されている。一方、N-エピタキシャル層4との接合面がpn接合面となるコレクタ領域としてのP+拡散層14には、金属シリサイド層は形成されていない。

(もっと読む)

半導体装置の製造方法

【課題】

製造工程を簡略化しつつ、特性の優れた第1のMOSトランジスタと第2のMOSトランジスタとを製造する半導体装置の製造方法を提供する。

【解決手段】

半導体基板に、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域を画定する素子分離領域を形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域に第1導電型の不純物をイオン注入し、第1導電型のウェルを形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域上に絶縁ゲート電極を形成し、第2のMOSトランジスタのドレイン領域を覆うマスクを介して、半導体基板法線方向から傾いた複数方向から第1導電型の不純物をイオン注入し、第1のMOSトランジスタ領域の前記絶縁ゲート電極下方に対称的なチャネルドーズ領域、第2のMOSトランジスタ領域の前記絶縁ゲート電極下方に非対称なチャネルドーズ領域を形成し、半導体装置を製造する。

(もっと読む)

電界効果トランジスタのソース延長部及びドレイン延長部が異なるドーパントで画定される半導体構成体の構成及び製造

【課題】 半導体ボディの上部表面に沿って設けられた絶縁ゲート電界効果トランジスタ(100)は、チャンネルゾーン(244)によって横方向に分離された一対のソース/ドレインゾーン(240及び242)を有している。

【解決手段】 ゲート電極(262)が該チャンネルゾーン上方でゲート誘電体層(260)の上側に存在している。各ソース/ドレインゾーンは、主要部分(204M又は242M)及び該主要部分と横方向に連続的であり且つ該ゲート電極下側を横方向に延在する一層軽度にドープした横方向延長部(240E又は242E)を包含している。該横方向延長部は、該チャンネルゾーンを上部半導体表面に沿って終端させており、異なる原子量の一対の半導体ドーパントによって夫々ほぼ画定される。該トランジスタが非対称的装置であり、該ソース/ドレインゾーンはソース及びドレインを構成する。該ソースの横方向延長部は該ドレインの横方向延長部よりも一層軽度にドープされており且つ一層高い原子量のドーパントで画定される。

(もっと読む)

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

調整した垂直窒素濃度分布を具備する窒化ゲート誘電体層を有する電界効果トランジスタの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(110,114又は122)のゲート誘電体層(500,566又は700)は、垂直濃度分布を有する窒素を含有している。

【解決手段】 該垂直濃度分布は、上側に位置しているゲート電極(502,568又は702)内のボロンが該ゲート誘電体層を介して下側のチャンネルゾーン(484,554又は684)内に著しく浸透することを防止し同時に該ゲート誘電体層から下側に存在する半導体ボディ内への窒素の移動を回避するために特別に調整されている。該チャンネルゾーン内の不所望のボロンから及び該半導体ボディにおける不所望の窒素から発生する場合がある損傷は実質的に回避される。

(もっと読む)

複数の局所的濃度最大によって画定されたソース/ドレイン延長部を有する電界効果トランジスタの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(100W)は、半導体ボディのボディ物質(180)のチャンネルゾーン(244)によって横方向に分離されているソース(980)及びドレイン(242)を有している。

【解決手段】 ゲート電極(262)が該チャンネルゾーンの上方でゲート誘電体層(260)の上側に位置している。該ボディ物質の一層高度にドープしたポケット部分(250)が、通常、該ソースのみにほぼ沿って延在しており、従って該IGFETは非対称的装置である。該ソースを画定する半導体ドーパントはソース延長部を画定する場合に複数の局所的濃度最大に到達する。2つのこの様な局所的濃度最大に到達する半導体ドーパントで該ソース延長部を画定する場合に関与する手順は、3個の絶縁ゲート電界効果トランジスタ用の相互に異なる特性のソース/ドレイン延長部を2つのソース/ドレイン延長部ドーピング操作のみで画定することを可能とする。

(もっと読む)

非対称的チャンネルゾーン及び異なる構成としたソース/ドレイン延長部を有する非対称的電界効果トランジスタの構成及び製造

【課題】 非対称的絶縁ゲート電界効果トランジスタ(100又は102)は半導体ボディのボディ物質(180又は182)のチャンネルゾーン(244又は284)によって横方向に分離されたソース(240又は280)及びドレイン(242又は282)を有している。

【解決手段】 ゲート電極(262又は302)が該チャンネルゾーンの上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の一層高度にドープしたポケット部分(250又は290)がほぼ該ソースのみに沿って延在している。該ソースは、主要ソース部分(240M又は280M)と、一層軽度にドープした横方向ソース延長部(240E又は280E)とを有している。該ドレインは、主要ドレイン部分(242M又は282M)と、一層軽度にドープした横方向ドレイン延長部(242E又は282E)とを有している。該ドレイン延長部は該ソース延長部よりも一層軽度にドープされている。これら2つの延長部を画定する半導体ドーパントの最大濃度は、該ソース延長部におけるよりも該ドレイン延長部において一層深くに発生する。付加的に又は代替的に、該ドレイン延長部は該ソース延長部よりも該ゲート電極下側を更に横方向に延在する。これらの特徴はスレッシュホールド電圧が動作時間に関して高度に安定であることを可能とする。

(もっと読む)

ソース/ドレイン延長部又は/及びハローポケットと組み合わせて空のウエルを使用した電界効果トランジスタの構成及び製造

【課題】 混合信号適用例を含むアナログ及びデジタル適用例用のIGFETを与える半導体製造プラットフォームに適した対称的及び非対称的の両方の絶縁ゲート電界効果トランジスタ(「IGFET」)が、高性能を達成する上で空のウエル領域を使用する。

【解決手段】 各空のウエルの上部近くにおいては半導体ウエルドーパントが比較的少量である。各IGFET(100,102,112,114,124又は236)は、空のウエル(180,182,192,194,204又は206)のボディ物質のチャンネルゾーンによって横方向に分離された一対のソース/ドレインゾーンを有している。ゲート電極が該チャンネルゾーン上方でゲート誘電体層の上側に位置している。各ソース/ドレインゾーン(240,242,280,282,520,522,550,552,720.722、752又は752)が主要部分(240M,242M,280M,282M,520M,522M,550M,552M,720M,722M,752M又は752M)及び一層軽度にドープした横方向延長部(240E,242E,280E,282E,520E,522E,550E,552E,720E,722E,752E又は752E)を有している。代替的に又は付加的に、該ボディ物質の一層高度にドープしたポケット部分(250又は290)が該ソース/ドレインゾーンの内の一方に沿って延在する。存在する場合には、該ポケット部分は典型的に該IGFETを非対称的装置とさせる。

(もっと読む)

ソース/ドレイン延長部、ハローポケット及びゲート誘電体厚さの異なる構成を有する同極性の電界効果トランジスタの構成及び製造

【課題】 一群の高性能同極性絶縁ゲート電界効果トランジスタ(100,108,112,116,120及び124又は102,110,114、118,112及び126)が、アナログ及び/又はデジタル適用例用の広く多様なトランジスタを提供する半導体製造プラットフォームに適した横方向ソース/ドレイン延長部、ハローポケット、及びゲート誘電体厚さの選択可能な異なる構成を有している。

【解決手段】 各トランジスタは、一対のソース/ドレインゾーン、ゲート誘電体層、及びゲート電極を有している。各ソース/ドレインゾーンは主要部分及び一層軽度にドープした横方向延長部を有している。該トランジスタの内の一つのソース/ドレインゾーンの内の一つの横方向延長部が該トランジスタの別のもののソース/ドレインゾーンの内の一つの横方向延長部よりも一層高度にドープされており又は/及びそれよりも上部半導体表面下側により少ない深さに延在している。

(もっと読む)

半導体装置及びその製造方法

【課題】 リーク電流の低減を実現しながらも従来に比べて更に素子サイズを縮小させることが可能な、高耐圧MOSトランジスタを実現する。

【解決手段】 P型ウェル10上に、チャネル領域chを隔てて、ドレイン領域12及びドレイン側ドリフト領域7を含むN型の第一不純物拡散領域と、ソース領域12及びそース側ドリフト領域8を含むN型の第二不純物拡散領域が形成されている。また、第一不純物拡散領域の一部上方、前記チャネル領域の上方、及び前記第二不純物拡散領域の一部上方にわたってゲート酸化膜6を介してゲート電極20が形成されている。ゲート電極20は、N型にドープされており、第一及び第二不純物拡散領域の上方に位置する部分の電極20bの不純物濃度が、前記チャネル領域の上方に位置する部分20aの不純物濃度よりも低濃度である。

(もっと読む)

半導体装置

【課題】対基板耐圧が向上しチップシュリンクも実現可能な、DTI構造を有する半導体装置を提供する。

【解決手段】例えばP型の基板1と、この基板1上に形成されたN型のEPI層2と、基板1とEPI層2とにわたって形成されたN型の第1の埋め込み層(埋め込み層3)と、この第1の埋め込み層の下に形成され埋め込み層3よりも不純物濃度の低いN型の第2の埋め込み層(埋め込み層12)と、EPI層2の表面から埋め込み層12、埋め込み層3を貫通して基板1内に達するDTI4と、を備えた半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】直接トンネル電流が流れる程度に薄膜化されたゲート絶縁膜におけるゲート電極からのドーパント原子の基板への拡散を防止すると共に、ゲートリーク電流を低減できるようにする。

【解決手段】第1の素子形成領域51及び第2の素子形成領域52に区画された半導体基板11上に、酸化膜からなる第1のゲート絶縁膜13Aを形成する。次に、第1のゲート絶縁膜13Aの第2の素子形成領域52に含まれる部分を除去し、半導体基板11に対して酸窒化性雰囲気で熱処理を行なうことにより、第2の素子形成領域52上に膜厚が第1のゲート絶縁膜13Aよりも小さい酸窒化膜からなる第2のゲート絶縁膜15Bを形成する。次に、第1のゲート絶縁膜13B及び第2のゲート絶縁膜15Bを窒素プラズマに暴露することにより、窒素原子をさらに導入された第1のゲート絶縁膜13C及び第2のゲート絶縁膜15Cを形成する。

(もっと読む)

半導体素子、半導体装置および半導体素子の製造方法

【課題】ESD保護素子が集積された回路全体の製造コストを低減する。

【解決手段】ESD保護素子100は、nチャネルGGFET構造を有している。ESD保護素子100において、第1p+低抵抗領域41は、第1pウエル領域4の一部に、第1p++コンタクト領域5とその下の領域、n++ソース領域8とその下の領域、第1LDD領域6とその下の領域、第1ゲート絶縁膜12の下の領域、第2LDD領域7とその下の領域、およびn++ドレイン領域9の一部とその下の領域に設けられている。第1p+低抵抗領域41のn++ドレイン領域9側の端部から、第1ゲート電極13のn++ドレイン領域9側の端部までの第1エクステンション距離(LBP1)は、0〜0.3μmの範囲内にある。ESD保護素子100の第1p+低抵抗領域41は、高耐圧デバイスの低抵抗領域と同時に形成される。

(もっと読む)

半導体素子の製造方法

【課題】欠陥が低減され膜質が良好なゲート酸化膜を有する半導体素子を製造する。

【解決手段】基板2のフィールド領域の表面にフィールド酸化膜4を形成する工程と、フィールド酸化膜4を形成した基板2の第1アクティブ領域および第2アクティブ領域の表面に第1ゲート酸化膜11A,11Bを形成する工程と、第1ゲート酸化膜11A,11Bに第1純水ヒーリングを施す工程と、第2アクティブ領域における第1ゲート酸化膜11Bを除去する工程と、第1アクティブ領域および第2アクティブ領域の表面に第2ゲート酸化膜12A,12Bを形成する工程と、第2ゲート酸化膜12A,12Bに第2純水ヒーリングを施す工程と、第1アクティブ領域および第2アクティブ領域における第2ゲート酸化膜12A,12B上にゲート電極8を形成する工程と、をこの順に有する半導体素子の製造方法。

(もっと読む)

161 - 180 / 648

[ Back to top ]