Fターム[5F140AB01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 複合(回路要素) (3,149) | MOSIC、MISIC (2,326)

Fターム[5F140AB01]の下位に属するFターム

E/EMOS、E/DMOSを構成するもの (22)

CMOSを構成するもの (1,656)

Fターム[5F140AB01]に分類される特許

201 - 220 / 648

半導体装置及びその製造方法

【課題】 半導体装置におけるトランジスタの熱破壊を防止し得るとともに、安全動作領域(SOA)を拡大しトランジスタ設計の自由度を高め得る半導体装置及びその製造方法を提供すること。

【解決手段】 トランジスタセルを並列にチップ内に均一に配置した半導体装置において、チップの面中央部にトランジスタセルの不動作領域を形成する。不動作領域を形成手段として、1)ソースとドレインのn型拡散層を設けない方法 2)ソースとドレインのコンタクト窓を開けない方法 3)ゲート電極を分岐してソースに接続する方法を採る。また、不動作領域の形成に代えて当該領域のトランジスタセルの閾値電圧を高くして動作電流を低くする手段を採ることもできる。

(もっと読む)

酸化膜の作成方法及び半導体装置の製造方法

【課題】低温の酸化処理により酸化膜を形成する。

【解決手段】酸化膜の作成方法は、主鎖にSi−N結合を有する高分子化合物を含む第1の膜16と主鎖にSi−O結合を有する高分子化合物を含む第2の膜15とを積層する工程と、前記第1の膜16及び前記第2の膜15を水蒸気又は水性の雰囲気中で加熱処理し、前記第1の膜16及び前記第2の膜15を酸化膜18に変化させる工程と、を具備する。

(もっと読む)

半導体装置

【課題】トランジスタ対を有する半導体装置において、回路面積の増大を抑えつつ、対をなすトランジスタの特性のアンバランスを抑制する。

【解決手段】トランジスタ1a,1bは活性領域パターンが互いに同一である領域A1a,A1bを有し、トランジスタ2a,2bは活性領域パターンが互いに同一である領域A2a,A2bを有する。トランジスタ2a,2bの活性領域13a,13bは、チャネル長方向の長さがトランジスタ1a,1bの活性領域11a,11bよりも長く、領域A2a,A2bは領域A1a,A1bよりもチャネル長方向の幅が狭い。

(もっと読む)

半導体装置の製造方法

【課題】複数回の露光処理によりゲート加工を行う半導体装置の製造方法に関し、工程数の増加等の問題を抑制する。

【解決手段】端部同士が隙間を挟んで対向する少なくとも一対のゲート電極を形成する半導体装置の製造方法であって、当該方法では、基板(111)上に、ゲート絶縁膜(112)とゲート電極層(113X)とを形成し、前記ゲート電極層上に形成された第1のレジスト(202)又は第1の反射防止膜(201)をマスクとして、前記ゲート電極層を加工することにより、前記ゲート電極層を、前記隙間が形成される領域から除去して、前記ゲート電極層に穴(121)を形成し、前記穴が形成された前記ゲート電極層上に形成された第2のレジスト(302)又は第2の反射防止膜(301)をマスクとして、前記ゲート電極層を加工することにより、前記ゲート電極層から、前記端部同士が前記隙間を挟んで対向する前記少なくとも一対のゲート電極(113)を形成する。

(もっと読む)

半導体装置

【課題】コンタクトの位置ずれが回路の特性に与える影響を低減した半導体装置を提供する。

【解決手段】この半導体装置は、半導体層10に設けられた素子分離膜20と、素子分離膜20により区画された素子形成領域と、素子形成領域上及び素子分離膜20上を延伸しているゲート配線140と、ゲート配線140の側壁に形成されたサイドウォール150と、素子分離膜20上に位置するゲート配線140に接続するコンタクト200とを備える。ゲート配線140の側壁は、少なくとも上部においてコンタクト200に接触してる領域144を有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の側壁を熱酸化させて修復する際に、Ti元素を含む金属材料からなるゲート電極膜の酸化を抑制する。

【解決手段】基板上に形成されたゲート絶縁膜の側壁にプラズマによって活性化させた反応ガスを供給する工程を有する半導体装置の製造方法であって、ゲート絶縁膜上にはTi元素を含む金属材料からなるゲート電極膜が形成されており、前記反応ガス中に含まれるO2ガスの流量を、前記反応ガス中に含まれるH2ガスの流量の1/19以下とする。

(もっと読む)

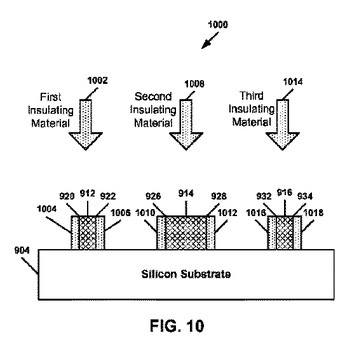

フィン電界効果トランジスタ(フィンFET)デバイスの製造方法

フィン電界効果トランジスタ(フィンFET)を用いた半導体の製造方法が開示される。特定の実施形態の方法は、第一の幅によって離隔された第一の側壁及び第二の側壁を有する第一のダミー構造体をシリコン基板上に堆積させるステップを含む。また、本方法は、第一のダミー構造体を堆積させるのと同時に第二のダミー構造体をシリコン基板上に堆積させるステップも含む。第二のダミー構造体は、第二の幅によって離隔された第三の側壁及び第四の側壁を有する。第二の幅は第一の幅よりも実質的に大きい。第一のダミー構造体を用いて略第一の幅によって離隔された第一の対のフィンを形成する。第二のダミー構造体を用いて略第二の幅によって離隔された第二の対のフィンを形成する。  (もっと読む)

(もっと読む)

複数のトランジスタゲートの形成方法、および少なくとも二つの異なる仕事関数を有する複数のトランジスタゲートの形成方法

少なくとも二つの異なる仕事関数を有する複数のトランジスタゲートを形成する方法は、異なる幅を有する基板上に第一および第二のトランジスタゲートを形成するステップを含み、第一の幅は第二の幅よりも狭い。材料は、第一および第二のゲート上を含む基板上に堆積される。エッチングチャンバー内で、材料は、第一および第二のゲートの双方の上からエッチングされ、第一のゲートの導電性材料を露出し、第二のゲート上に支持された材料の厚さを減少させ、材料によって被覆された第二のゲートをそのまま残す。エッチング後に、エッチングチャンバー内のそのままの位置で、基板は少なくとも300℃の基板温度で金属を含むプラズマに対して暴露され、第二のゲートの仕事関数と比較して、第一のゲートの仕事関数を改変するために、第一のゲートへと金属を拡散させる。  (もっと読む)

(もっと読む)

半導体装置

【課題】起動回路と周辺回路とを併せて集積化し得る半導体装置を提供する。

【解決手段】領域411においては、素子分離領域により規定されるドレイン領域121にボディ領域が形成され、ボディ領域にN型のソース領域が形成される。ドレイン領域121とN型のソース領域との間に第1のゲート電極20が配置される。素子分離領域は開口部133が形成されたループ状部と、開口部133を介してドレイン領域121に接続された延在領域122を規定する部分とを備える。延在領域122に、N型のソース引出領域が形成される。内部回路412においては、ドレイン領域121にP型のボディ領域が形成され、P型のボディ領域にN型のソース領域が形成され、ドレイン領域121とN型のソース領域との間に第2のゲート電極331が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル幅が狭い場合においても、eWFが十分に低減された閾値電圧が低い半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11と、半導体基板11の上に形成され、第1の元素と第2の元素とを含むゲート絶縁膜26と、ゲート絶縁膜26の上に形成されたゲート電極27とを備えている。ゲート絶縁膜26は、半導体基板11側においてゲート電極27側と比べて第1の元素の含有量が多く、ゲート電極27側において半導体基板11側と比べて第2の元素の含有量が多い。

(もっと読む)

ファセットされたシリサイドコンタクトを有する半導体デバイス及び関連する製造方法

【解決手段】

開示される主題は、半導体トランジスタデバイス及び、従来のシリサイドコンタクトと比較して増大された実効サイズを有するシリサイドコンタクトを形成するために利用することができる関連する製造技術に関する。ここに開示されるプロセスに従って製造される半導体デバイス(200)は、半導体材質(102)の層と、半導体材質(102)の層を覆うゲート構造(112,128)とを含む。チャネル領域(218)が半導体材質(102)の層内に形成され、チャネル領域(218)はゲート構造(112,128)の下層となる。半導体デバイス(200)はまた、半導体材質(102)の層内のソース及びドレイン領域(216)を含み、チャネル領域(218)はソース及びドレイン領域(216)の間に配置される。また、半導体デバイス(200)はソース及びドレイン領域(216)を覆うファセット形状シリサイドコンタクト区域(210,308,406)を含む。

(もっと読む)

半導体装置

【課題】 従来の比例縮小側(係数α、α>1)を適用した平面型MOSTのしきい電圧のばらつきの標準偏差σ(VT)が、微細化とともに、すなわちαを大きくするとともに大きくなり、動作電圧が低くできないという問題がある。

【解決手段】 フィンの高さをチャンネル長よりも高くしたFinFET構造によって上記の問題を解決する。

(もっと読む)

トランジスタ型保護素子、半導体集積回路およびその製造方法

【課題】保護素子のターンオン電圧を決める制約を少なくする。

【解決手段】半導体基板1、Pウェル2、ゲート電極4、ソース領域5、ドレイン領域6および抵抗性降伏領域8を有する。抵抗性降伏領域8はドレイン領域6に接し、ゲート電極4直下のウェル部分と所定の距離だけ離れたN型半導体領域からなる。ドレイン領域6または抵抗性降伏領域8に接合降伏が発生するドレインバイアスの印加時に抵抗性降伏領域8に電気的中性領域(8i)が残るように、抵抗性降伏領域8の冶金学的接合形状と濃度プロファイルが決められている。

(もっと読む)

半導体装置の製造方法、熱酸化処理方法及び熱酸化処理装置

【課題】本発明は、熱酸化処理方法に関し、膜厚均一性の高いゲート酸化膜を形成することができる半導体装置の製造方法、熱酸化処理方法及び熱酸化処理装置を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、モニタウェハM1の裏面と第1の製品ウェハ#2の表面を対向させ、且つ第1の製品ウェハ#2の裏面と第2の製品ウェハ#3の表面を対向させ、且つモニタウェハM1、第1及び第2の製品ウェハ#2、#3それぞれの裏面にシリコン窒化膜23が形成された状態で熱酸化処理装置内に配置し、熱酸化処理装置によってモニタウェハM1、第1及び第2の製品ウェハ#2、#3それぞれの表面に熱酸化膜を形成する工程を具備することを特徴とする。

(もっと読む)

半導体装置

【課題】チップの占有面積を有効に活用する。

【解決手段】P型半導体基板11上にN型エピタキシャル層12が形成され、LDMOSとJFETに共通なドレイン領域121を規定するP型素子分離領域13が形成される。ドレイン領域121内にボディ領域15が形成され、ボディ領域15内にN型ソース領域16が形成され、ドレイン領域121とソース領域16間のチャネル領域上にゲート電極20が配置され、LDMOSが形成される。ボディ領域15とP型素子分離領域13との間にJFETのソースとなるN型領域が形成される。ドレインに正のドレイン電圧が印加されると、PN接合が逆バイアスされ、ボディ領域15と分離領域13と半導体基板11とから空乏層が延び、JFETのチャネルを制御する。

(もっと読む)

半導体電子デバイスおよび半導体電子デバイスの製造方法

【課題】耐圧性が高く反りが小さくオン抵抗が低い半導体電子デバイスおよびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された、該基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層と、前記バッファ層上に形成された、窒化物系化合物半導体からなる半導体動作層と、窒化物系化合物半導体からなり、前記バッファ層直下から前記電子走行層内部までのいずれかの位置に形成され、凹凸形状の境界面を有する下層領域と上層領域とを有し、該下層領域から該上層領域へ延伸する貫通転位が該境界面において屈曲している転位低減層と、を備える。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、製造条件のばらつきにより、保護素子よりも先に被保護素子がオン動作し、過電圧から被保護素子が保護し難いという問題があった。

【解決手段】本発明の半導体装置では、保護素子1とMOSトランジスタ15との構成の一部を共用する。そして、保護素子1を構成するN型の拡散層8とMOSトランジスタ15を構成するN型の拡散層19を同一工程で形成するが、N型の拡散層8の拡散幅W3が、N型の拡散層19の拡散幅W4よりも広くなる。この構造により、出力端子に過電圧が印加された際に、MOSトランジスタ15よりも保護素子1の方が先にオン動作し、アバランシェ電流からMOSトランジスタ15が保護される。

(もっと読む)

半導体デバイスシミュレーション方法およびこれを実行する半導体デバイスシミュレーション装置

【課題】 計算コストの低減に対して有利な半導体デバイスシミュレーション方法およびこれを実行する半導体デバイスシュミレーション装置を提供する。

【解決手段】 デバイスシミュレーション方法は、非等方的な散乱過程の処理に関して、運動量緩和時間の逆数を計算し、前記運動量緩和時間の逆数を用いてフリーフライト時間を計算するステップS101と、前記フリーフライト時間後の時刻を計算するステップS102と、前記フリーフライト時間の間のドリフト過程の計算を行うステップS103と、散乱後の波数を等方的散乱であるとみなして散乱過程を計算するステップS104とを具備する。

(もっと読む)

半導体装置

【課題】 複数チャネル出力回路を構成する複数のトランジスタを持つ半導体装置においてセルサイズ縮小および信頼性向上を図る。

【解決手段】 複数のチャネル回路構成において、共通の機能を有する複数のチャネルのトランジスタ群を共通のトレンチ溝で囲い、機能の異なるトランジスタ郡に対して絶縁素子分離されていて、ハイサイド側の隣接するトランジスタのコレクタ部を共有化してVH電源に接続すると共に、ローサイド側の隣接するチャネルのトランジスタ群のエミッタ部を共有化してGND電源に接続する。

(もっと読む)

電界効果トランジスタ、メモリセル、および電界効果トランジスタの製造方法

【課題】洗浄工程で活性領域が倒れたり、変形したりするのを防いだ電界効果トランジスタを提供する。

【解決手段】半導体基板の表面に、FETの動作時にチャネルが発生する部位を含む4つの柱状活性領域を有し、各々の柱状活性領域は梁フィールド酸化膜8により分離され、各々の柱状活性領域の側面に接するようにゲート絶縁膜10を介してゲート電極11aおよび11bが設けられ、柱状活性領域の上面にはドレイン電極に相当する上部拡散層14dと、シリコン基板1の表面にソース電極に相当する下部拡散層9a、9b、9cおよび9dとが設けられた構成である。

(もっと読む)

201 - 220 / 648

[ Back to top ]