Fターム[5F140AB01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 複合(回路要素) (3,149) | MOSIC、MISIC (2,326)

Fターム[5F140AB01]の下位に属するFターム

E/EMOS、E/DMOSを構成するもの (22)

CMOSを構成するもの (1,656)

Fターム[5F140AB01]に分類される特許

121 - 140 / 648

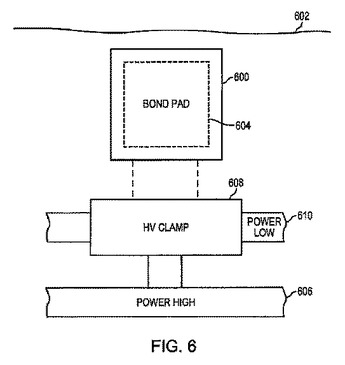

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】アンテナ効果によるゲート酸化膜の破壊等を防止するとともに、半導体装置の動作の遅延を抑制すること。

【解決手段】本発明の一態様に係る半導体装置は、前段出力トランジスタA1に金属配線A2aを介して接続された入力トランジスタゲート電極A9を有する入力トランジスタA3と、入力トランジスタゲート電極A9に抵抗素子A4を介して接続されたダミートランジスタA5を備える。抵抗素子A4は、入力トランジスタA3の後段に設けられ、金属配線A2aに接続されている。抵抗素子A4とダミートランジスタA5は、金属配線A2bを介して接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動電流が大きくリーク電流の少ない低消費電力のMISトランジスタを有する半導体装置及びその製造方法を提供する。

【解決手段】チャネル領域を有する半導体基板と、チャネル領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、半導体基板内にチャネル領域を挟むように配置されたソース拡散層及びドレイン拡散層と、ソース拡散層側の半導体基板内に形成された第1のポケット不純物層と、ドレイン拡散層側の半導体基板内に形成された第2のポケット不純物層とを有し、第1のポケット不純物層は、ソース拡散層のエクステンション不純物層の濃度ピーク位置よりも深い位置に濃度ピークを有しており、第2のポケット不純物層は、ドレイン拡散層のエクステンション不純物層の濃度ピーク位置よりも浅い位置に濃度ピークを有している。

(もっと読む)

半導体装置

【課題】本発明は、逆流電流への耐性を高めるレイアウトパターンを有する半導体装置を提供することを目的とする。

【解決手段】半導体基板10の表面領域に形成され、対向して延在するソース領域20及びドレイン領域30、31、32、33と、前記半導体基板の表面上に形成され、前記ソース領域20及びドレイン領域の間で前記ソース領域に沿って延在するゲート40とを含む複数のトランジスタセルと、前記複数のトランジスタセルの周囲を囲み、前記半導体基板10の基準電位を定める基板電極80とを備えた半導体装置100、101、102において、

前記半導体基板の表面領域の、前記ゲートに両側を挟まれた前記ドレイン領域の延在方向における端部と、前記基板電極との間の前記ドレイン領域の延長線上に、前記ドレイン領域と同電位の電流集中緩和電極70、71、72が設けられたことを特徴とする。

(もっと読む)

マルチフィン高さを有するFinFET

【課題】マルチフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、半導体基板と、半導体基板上のFinFETと、を含む。FinFETは、半導体フィンと、半導体フィンの頂面および側壁上のゲート誘電体と、ゲート誘電体上のゲート電極と、半導体フィン一端に位置するソース/ドレイン領域と、を備える。一対の第一STI領域は、ソース/ドレイン領域の一部分の真下に位置する部分を含み、一対の第一STI領域は、半導体ストリップにより分離され、且つ、半導体ストリップに隣接する。一対の第一STI領域は、更に、第一頂面を有する。一対の第二STI領域は、ゲート電極の真下に位置する部分を含み、一対の第二STI領域は、半導体ストリップにより互いに分離され、且つ、半導体ストリップに隣接する。第二STI領域は、第一頂面より高い第二頂面を有する。

(もっと読む)

FINFETSおよびその形成方法

【課題】フィン電界効果トランジスタのソース/ドレイン構造を提供する。

【解決手段】基板上のフィンチャネル本体110a、110b、フィンチャネル本体110a、110b、上に配置されたゲート電極115、およびフィンチャネル本体110a、110b、に隣接して配置され、どのフィン構造も実質的に含まない、少なくとも1つのソース/ドレイン(S/D)領域120a,120b及び125a,125bを含むフィン電界効果トランジスタ(FinFET)。

(もっと読む)

半導体装置、半導体集積回路装置及び半導体装置の製造方法

【課題】高耐圧且つ低オン抵抗な半導体装置及びこれを含む半導体集積回路装置を歩留まり良く、安価に提供する。

【解決手段】第1導電型の半導体基板(1)と、前記第1導電型と反対の第2導電型であって前記半導体基板の表面側に形成されたソース領域(11)、低濃度ドレイン領域(12)及び高濃度ドレイン領域(13)と、前記半導体基板上に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極と、を備える半導体装置(10)であって、

前記ゲート電極は、前記低濃度ドレイン領域の少なくとも一部を覆うように形成され、且つ、前記低濃度ドレイン領域の上方において開孔(16)を有することを特徴とする半導体装置。前記低濃度ドレイン領域と高濃度ドレイン領域とは互いに隣接することが好ましい。

(もっと読む)

半導体装置

【課題】パワーデバイスとCMOSデバイスとを混載することができ、パワーデバイスのアバランシェ耐量及びESD耐量が高い半導体装置を提供する。

【解決手段】半導体基板11の上部にP型のウェル12を形成し、ウェル12にSTI13を選択的に設け、STI13の開口部14内にSTI13の側面13aに接するようにN+型のソース層17及びドレイン層18を相互に離隔して形成する。また、ソース層17とドレイン層18との間に、P+型のコンタクト層19を形成する。コンタクト層19はソース層17に接し、STI13からは離隔するように形成する。更に、ソース電極21をソース層17及びコンタクト層19に接続し、ドレイン電極22をドレイン層18に接続し、STI13上に側面13aに沿ってゲート電極23を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの面積を小さくしてもフリッカノイズを低減できる半導体装置を提供する。

【解決手段】本発明の一態様の半導体装置は、シリコン基板1に形成された第1及び第2のP型低濃度不純物層3a,3bと、シリコン基板1に埋め込まれて形成され、第1及び第2のP型低濃度不純物層の相互間に位置する埋め込みチャネル層5と、埋め込みチャネル層の上方に位置するシリコン基板の表面上にゲート絶縁膜6を介して形成され、N型不純物が導入されたポリシリコン膜からなるゲート電極と、第1のP型低濃度不純物層3a内における深さが浅い領域に形成されたソース領域及びドレイン領域の一方のP型層13aと、第2のP型低濃度不純物層3b内における深さが浅い領域に形成されたソース領域及びドレイン領域の他方のP型層13bと、を具備することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】MIPS構造等のゲート電極と同時形成が可能であり且つ抵抗が高い抵抗素子を有する半導体装置及びその製造方法を提供する。

【解決手段】基板上に金属含有膜108及びポリシリコン膜109を順次形成する工程と、前記金属含有膜及び前記ポリシリコン膜を抵抗素子形状にパターニングする工程と、前記金属含有膜の少なくとも一部分を除去することにより、前記ポリシリコン膜の下に中空領域119を形成する工程とを備えている。

(もっと読む)

異なる誘電材料を用いたインター装置STI領域とイントラ装置STI領域の形成

【課題】異なる誘電材料を用いたインター装置STI領域とイントラ装置STI領域の形成を提供する。

【解決手段】集積回路構造は、第1装置領域に第1部分、第2装置領域に第2部分を有する基板と、第1装置領域中で、且つ、基板上に位置する2つの絶縁領域と、からなる。2つの絶縁領域は、第1k値を有する第1誘電材料を含む。半導体ストリップは、2つの絶縁領域間に位置し、且つ、2つの絶縁領域に隣接し、2つの絶縁領域の頂面上に、半導体フィンを形成する半導体ストリップの上部分を有する。追加の絶縁領域が、第2装置領域中で、且つ、基板上に位置する。追加の絶縁領域は、第1k値より大きい第2k値を有する第2誘電材料を含む。

(もっと読む)

半導体装置の製造方法

【課題】高耐圧な半導体装置の製造方法を提供する。

【解決手段】半導体層に対してマスクを用いて選択的にイオン注入を行い、半導体層に第1導電型の第1の半導体領域と、前記第1の半導体領域よりも第1導電型不純物濃度が低い第1導電型の第2の半導体領域とを同時に形成する工程と、第1の半導体領域上に第2導電型のソース領域を形成する工程と、第2の半導体領域上であってソース領域との間にゲート電極を挟む位置に第2導電型のドレイン領域を形成する工程と、半導体層におけるゲート電極とドレイン領域との間の表層部にドレイン領域に接しドレイン領域よりも不純物濃度が低い第2導電型のドリフト領域を形成する工程とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 MOSトランジスタの製造工程を削減し、さらには寄生MOSの敷居値電圧が低下するのを抑制する。

【解決手段】 本発明の半導体装置の製造方法は、ゲート電極形成後にウェル拡散層とは逆導電型のチャネル形成用の不純物をイオン注入する製造方法において、フィールド酸化膜30にチャネル形成用の不純物をイオン注入しない製造方法である。従って、本発明の半導体装置は、フィールド酸化膜30にチャネル形成用の不純物がイオン注入されていない構造となる。

(もっと読む)

半導体装置およびその製造方法

【課題】n型MISトランジスタを有する半導体装置の特性ばらつきを低減させる。

【解決手段】シリコン基板1上のメモリ領域RMに形成された、n型導電型である第1トランジスタQ1は、ホウ素を含むメモリ用チャネル領域CH1と、メモリ用ゲート電極GE1の両側壁側下に形成された、n型のメモリ用エクステンション領域ET1および酸素を含む拡散防止領域PA1とを有している。ここで、拡散防止領域PA1はメモリ用エクステンション領域ET1を内包するようにして形成されている。また、拡散防止領域PA1は、少なくともその一部が、メモリ用エクステンション領域ET1とメモリ用チャネル領域CH1との間に配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ナローチャネル特性の劣化を抑制する。

【解決手段】素子分離領域STIは、半導体基板100に形成されたトレンチ104内に設けられており、トレンチ104の側壁上に形成された下地絶縁膜105を有している。素子形成領域100a上にはゲート絶縁膜112が形成されており、ゲート絶縁膜112は高誘電率膜110を有している。高誘電率膜110の第1の部分110aは、素子形成領域100aにおける上面上に形成されており、高誘電率膜110の第2の部分110bは、素子形成領域における上部側面104a上に下地絶縁膜105を介して形成されている。第2の部分110bと下地絶縁膜105との間には、MISトランジスタの閾値電圧を変更する金属を含有する第1のキャップ膜106が設けられている。

(もっと読む)

高耐圧半導体装置および駆動回路

【課題】スイッチング応答速度が速い高耐圧トランジスタ、および電力損失および誤動作を抑制した駆動回路を提供すること。

【解決手段】高耐圧半導体装置は、p-型シリコン基板100上に設けられ、かつp-ウエル領域102に囲まれたn-型領域101と、ドレイン電極120と接続されるドレインn+領域103と、ドレインn+領域103と離れて設けられ、かつドレインn+領域103を囲むpベース領域105と、pベース領域105内に形成されたソースn+領域114と、を備える。また、n-型領域101を貫通し、かつシリコン基板100に達するp-領域131が設けられている。n-型領域101は、p-領域131により、n-型領域101aとn-型領域101bに分離されている。n-型領域101aは、ドレインn+領域103を備えている。n-型領域101bは、フローティング電位を有する。

(もっと読む)

半導体装置の耐圧シミュレーション方法およびシミュレーション装置

【課題】シミュレータの解析領域を縮小した場合であっても計算結果を保証し得る半導体装置の耐圧シミュレーション方法およびかかるシミュレーション方法を実行するシミュレーション装置を提供する。

【解決手段】

半導体装置に含まれるn型領域およびp型領域と同一の不純物濃度を有するnpn構造若しくはpnp構造を含む接合構造に対して一次元シミュレーションを行って、半導体装置における空乏層についての一次元シミュレーション値を取得する。少なくとも1つのpnジャンクションを含む半導体装置の一部である対象領域について、一次元シミュレーション値を用いて多次元シミュレーションを行って、対象領域内のpnジャンクションを逆バイアスしたときの対象領域内部における一次元シミュレーション値に基づく空乏層のエッジ位置を算出する。空乏層のエッジ位置が対象領域内の所定位置に達したときの対象領域への印加電圧を半導体装置の耐圧と推定する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に対する不純物の突き抜けを抑止する。

【課題を解決するための手段】半導体装置の製造方法は、基板上方に成膜した多結晶シリコンをエッチングして基板の第1領域上方に第1ゲート電極を形成し、基板の第2領域上方に第2ゲート電極を形成し、第1領域及び第1ゲート電極を覆う第1パターンを形成し、第2ゲート電極及び第1パターンをマスクにして第2領域に第1不純物を第1ドーズ量で注入して第2領域に第1エクステンション領域を形成し、第1ゲート電極、第1領域及び第2ゲート電極の上面を露出させた第2パターンを形成し、第1エクステンション領域を覆い、第1ゲート電極、第2ゲート電極及び第2パターンをマスクにして第1領域に第2不純物を第1ドーズ量よりも多いドーズ量で注入して第1領域に第2エクステンション領域を形成するとともに、第1ゲート電極及び第2ゲート電極の少なくとも上部をアモルファス化する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

半導体装置とその製造方法

【課題】

高温、長時間のアニールを必要とすることなく、低いオン抵抗を実現可能な高耐圧MOSトランジスタを含む半導体装置を提供する。

【解決手段】

半導体基板の高耐圧トランジスタ用第1導電型領域上にゲート電極を形成し、ゲート電極のドレイン側部分及びドレイン領域を覆う第1のマスクをイオン注入マスクとして、ゲート電極を貫通する加速エネルギで第1導電型の不純物イオンを注入して、ソース領域で深く、ゲート電極下方で浅いチャネルドーズ領域を形成し、ゲート電極のドレイン側部分及びドレイン領域を覆う第2のマスク及びゲート電極をイオン注入マスクとして第2導電型の不純物をイオン注入してソースエクステンション領域を形成し、半導体装置を製造する。

(もっと読む)

121 - 140 / 648

[ Back to top ]