Fターム[5F140AB01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 複合(回路要素) (3,149) | MOSIC、MISIC (2,326)

Fターム[5F140AB01]の下位に属するFターム

E/EMOS、E/DMOSを構成するもの (22)

CMOSを構成するもの (1,656)

Fターム[5F140AB01]に分類される特許

81 - 100 / 648

半導体装置、及びその製造方法

【課題】高品質な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成される半導体領域、半導体領域内に形成され、互いに分離されているソース領域及びドレイン領域、半導体領域内に形成され、ソース領域及びドレイン領域を分離するチャネル領域、チャネル領域上に形成され、1×1019atoms/cm2よりも大きいピーク濃度で、Si、O、またはNとは異なる少なくとも一つの要素を有する界面酸化層、及び界面酸化層上に形成され、実質的に界面酸化層に隣接する深さでhigh―k/界面酸化層接合面を有するhigh―k絶縁層を有するMOS(metal-oxide-semiconductor)トランジスタを備え、少なくとも一つの要素のピーク濃度の少なくとも一つの深さは、実質的にhigh―k/界面酸化層接合面よりも下に位置する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、ゲート絶縁膜の一方の側のみに、容易に、かつ精度良く、バーズビークを形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】斜めイオン注入により、マスク膜にイオンを注入することで、シリコン酸化膜及びシリコン窒化膜を介して、ゲート絶縁膜の第1の側面と第1の不純物拡散領域の上面とで構成される角部に形成されたマスク膜のエッチング速度を、他の部分に形成されたマスク膜よりも速くし、次いで、ウエットエッチングにより、角部に形成されたマスク膜を選択的に除去して、シリコン窒化膜の表面の一部を露出させ、次いで、ウエットエッチングにより、マスク膜から露出されたシリコン窒化膜を選択的に除去して、シリコン酸化膜の表面の一部を露出させ、その後、熱酸化法により、ゲート絶縁膜の第1の側面側にバーズビークを形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極上のキャップ膜が厚く、隣接するトランジスタ間の空間のアスペクト比が大きいトランジスタに、適切な濃度プロファイルを有するハロー領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】一実施の形態による半導体装置の製造方法は、基板上に第1および第2のゲート電極を形成する工程と、前記第1および第2のゲート電極下に第1および第2のハロー領域をそれぞれ形成する工程と、前記第1および第2の絶縁膜に底面および側面をそれぞれ覆われた第1および第2のキャップ膜を形成する工程と、を含む。前記第1のハロー領域は、第1の不純物を、前記第2の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。前記第2のハロー領域は、第2の不純物を、前記第1の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板上に形成されたFETのソース側のエクステンション領域の抵抗値を低減し、半導体装置の動作速度を向上することができる技術を提供する。

【解決手段】ゲート電極4dの側壁に、ゲート電極4dのゲート長方向の幅が異なる第1サイドウォール6wおよび第2サイドウォール6nをそれぞれ形成する。これにより、第1サイドウォール6wおよび第2サイドウォール6nの形状によって第1サイドウォール6wおよび第2サイドウォール6nの下部に自己整合的に形成されるエクステンション領域37、38の半導体基板SBの上面の幅をそれぞれ異なる長さで形成する。

(もっと読む)

半導体装置、およびその製造方法

【課題】従来に比して高いESD耐量性能を有するESD保護回路を備えた半導体装置、およびその製造方法を提供する。

【解決手段】内部回路に用いられる第1の半導体素子と、静電気による内部回路の破壊を抑制するESD保護回路として用いられる第2の半導体素子とを備える半導体装置の製造方法であって、基板に第1の半導体素子および第2の半導体素子各々についての端子領域層を形成する端子領域層形成ステップと、基板上の前記第2の半導体素子の端子領域層を除く領域について結晶欠陥を形成させる処理を施す欠陥形成ステップと、金属膜を第1の半導体素子および第2の半導体素子各々の端子領域層表面に形成する金属膜形成ステップと、金属膜と、第1の半導体素子および第2の半導体素子各々の端子領域層とをシリサイド化するシリサイド化ステップとを含む、半導体装置の製造方法である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】小型化できると共に安定的に高耐圧化できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、P型の半導体基板1と、半導体基板1の表面のP−型の拡散領域2a,2bと、拡散領域2bに隣接した本体部、及び、拡散領域2bと拡散領域2bの下方の半導体基板1との間に挟まれた外縁部を有するN型の拡散領域3と、x方向に並んで拡散領域2a,2bに形成されたN+/N++型のソース領域7及びドレイン領域8,9と、第1ゲート電極11と、を有する第1のMOSトランジスタ100と、拡散領域3の外縁部の上方の拡散領域2bに形成され、一端がx方向に延びて拡散領域3の本体部と接続している、N+型の拡散領域5を有する半導体素子Sと、を備える。第1のMOSトランジスタ100と半導体素子Sの拡散領域5とは、y方向に並んで、拡散領域2bで電気的に分離されている。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

半導体装置及びその製造方法

【課題】保護膜としてSiN膜が使用されている場合であっても、素子動作特性の変動を軽減することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置2は、ドレインドリフト領域12を有する半導体基板11と、ドレインドリフト領域12上に形成されたフィールド酸化膜17と、ゲート電極18と、中間絶縁膜17と、メタル層21,22と、これらを覆うSiN膜23と、SiN膜23上にO3−TEOSを用いたCVD法により形成され、カーボンを含有するPSG膜24とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、素子面積を縮小可能で高耐圧なMOS型電界効果トランジスタを備える半導体装置及びその製造方法を提供する。

【解決手段】

本実施形態の半導体装置100は、半導体基板10と、半導体基板10に設けられた素子分離領域14a,14bと、隣接する素子分離領域で区画された素子領域上に半導体基板10上に設けられたゲート絶縁膜12と、ゲート絶縁膜12上に設けられたゲート電極13と、ゲート電極13の直下近傍の素子領域表面に設けられたソース・ドレイン拡散領域11a,11bと、前記ソース・ドレイン拡散領域11a,11b上に設けられたコンタクトプラグ15a,15bとを備え、ゲート絶縁膜12のドレイン側の膜厚は、ゲート絶縁膜12のソース側の膜厚より厚いことを特徴とする。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

電界効果トランジスタの高電圧動作方法とそのバイアス回路

【課題】 ICないしLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該ICないしLSI中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートを分割してドレインにより近い分割ゲートへドレイン電位により近い電位でかつドレイン電位に応じて変化する電位を供給する手段をとる。

(もっと読む)

静電気保護用のMOS型半導体装置

【課題】ESD素子のESD耐量を向上させる。

【解決手段】ESD素子21は半導体基板1表面に形成したP型ウェル領域2上にゲート絶縁膜を介して、一方向に延びた複数本のゲート電極3が相互に平行に設けられており、P型ウェル領域2の表面におけるゲート電極3の直下域がチャネル領域9になっている。そして、チャネル領域9間の領域がN+ソース領域5又はN+ドレイン領域4となっており、N+ソース領域5とN+ドレイン領域4とは交互に配列されている。そして、並列して隣接するゲート電極3間に位置するN+ドレイン領域4を分割し、かつ隣接するゲート電極3を接続するようにゲート電極接合領域10を設ける。なお、ゲート電極接合領域10の直下域にはチャネル領域9と同一の不純物濃度を有する領域11が設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】異なるチャネル長のトランジスタを有し、かつ、コンタクト抵抗の増加およびオン電流の減少を防止できる半導体装置の提供。

【解決手段】ピラートランジスタTr1と、前記ピラートランジスタTr1の下部拡散層7aへ信号または電源を供給するとともに、ポリシリコン層10aからの固相拡散し、下部拡散層7aを形成することにより、前記ピラートランジスタTr1のチャネル長d1を厚みにより制御する前記ポリシリコン層10aと、を具備してなることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】高耐電圧により大電流化が可能で、オン抵抗が低く高速動作が可能で、高集積化と省エネルギーが可能で、素子間分離の容易な、電気熱変換素子駆動用の半導体装置を提供する。

【解決手段】電気熱変換素子とそれに通電するためのスイッチング素子とがp型半導体基体1に集積化されている。スイッチング素子は、半導体基体1の表面に設けられたn型ウェル領域2と、それに隣接して設けられチャネル領域を提供するp型ベース領域6と、その表面側に設けられたn型ソース領域7と、n型ウェル領域2の表面側に設けられたn型ドレイン領域8,9と、チャネル領域上にゲート絶縁膜を介して設けられたゲート電極4とを有する絶縁ゲート型電界効果トランジスタである。ベース領域6は、ドレイン領域8,9を横方向に分離するように設けられた、ウェル領域2より不純物濃度の高い半導体からなる。

(もっと読む)

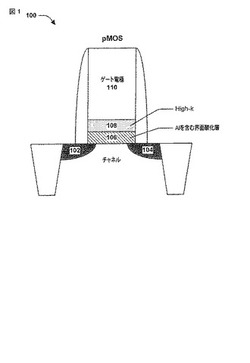

面エピ形状とソース/ドレインの部分的に覆われるシリサイド周辺とに関するフィンフェット

【課題】低い寄生抵抗(例えば、Rpara)および/または高い駆動電流の改善された特性を有するフィンフェットを提供する。

【解決手段】フィンフェット100およびフィンフェットの製造方法が提供される。フィンフェットは、半導体基板106上に、2つまたは複数のフィン102,104と、前記フィンの側面に設けられるエピタキシャル層108,110と、前記エピタキシャル層の表面上を覆うように設けられる金属−半導体化合物112,114とを備える。フィンは、前記半導体基板の表面上に対して実質的に垂直な側面を有する。前記エピタキシャル層は、前記フィンの側面に対して斜角を有して延設される表面を有する。フィンフェットは、前記金属−半導体化合物上に設けられるコンタクト116を含み得る。

(もっと読む)

半導体装置の製造方法

【課題】溝内の一部のみを覆うマスクパターンを、フォトレジスト膜を用いて形成する必要のない半導体装置の製造方法を提供する。

【解決手段】半導体基板1に、第1溝7を形成する工程と、第1溝7に第1絶縁膜8を形成する工程と、上面が第1絶縁膜の上端よりも下方になるように第1溝7内に第1導電膜9を充填する工程と、第1溝7の側面にカーボン膜10を形成する工程と、第1溝7内を第2絶縁膜11で充填する工程と、第1溝7内の側面の一方を覆うカーボン膜10を除去し、第1絶縁膜8の一部を露出させる工程と、第2絶縁膜11と露出された第1絶縁膜8を除去し、半導体基板1の一部を露出する工程と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】最小加工寸法がフィン幅となるFinFETの構造において、極めて制御が困難なリング形状の加工を不要として、加工ばらつきに起因する特性ばらつきの小さなユニットセルを提供する。

【解決手段】ユニットセルは、半導体基板1上に形成された開ループ構造のゲート電極Gと、前記ゲート電極Gの内方となる領域にフィン状に形成されたドレイン領域2と、前記ゲート電極Gの外方となる領域に形成されたフィン状のソース領域3とを有する。前記ドレイン領域2の上にはドレインコンタクト2aが形成され、前記ソース領域3上にはソースコンタクト3aが形成される。

(もっと読む)

半導体装置の製造方法

【課題】工程数が多く、煩雑になる問題を解決する半導体装置の製造方法を提供する。

【解決手段】半導体基板1に第1絶縁膜2を形成し、第1領域Aに第1導電型の第1ウエル層31を形成し、第1領域A以外の第1絶縁膜2上に第1半導体膜3を形成し、第1ウエル層31にトランジスタを形成し、第1半導体膜3及び第1領域Aの第1絶縁膜2の上に、トランジスタのビットコンタクトを兼ねる第2半導体膜7を形成する工程、第2半導体膜7上に、第2領域用B1のマスク8を積層してから、第1または第2導電型ドーパントを注入して第2ウエル層32を形成し、次いで、第2領域B1の少なくとも第2半導体膜7に、ドーパントを注入する工程、第2半導体膜7上に導電膜を積層してから、第1、第2半導体膜3,7及び導電膜を部分的にエッチングして、第1領域Aにトランジスタのビット配線層を、第2領域B1,B2に別の配線層を形成する工程、を具備する。

(もっと読む)

81 - 100 / 648

[ Back to top ]