Fターム[5F140AB01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 複合(回路要素) (3,149) | MOSIC、MISIC (2,326)

Fターム[5F140AB01]の下位に属するFターム

E/EMOS、E/DMOSを構成するもの (22)

CMOSを構成するもの (1,656)

Fターム[5F140AB01]に分類される特許

101 - 120 / 648

半導体装置

【課題】 工程の増加や占有面積の増加もなくオフリーク電流を小さく抑えた、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 素子分離にシャロートレンチ分離領域501を有するESD保護用のN型MOSトランジスタにおいて、ESD保護用のN型MOSトランジスタのゲート電極301下面のゲート絶縁膜を介してP型シリコン基板表面に形成されたチャネル領域の表面に、ESD保護用のN型MOSトランジスタのドレイン領域202から一定の距離を隔てたオフセット領域601を介して、濃いP型の不純物濃度領域からなるP型ブレークダウン領域401を形成した半導体装置とした。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の一部を高誘電体膜で構成した場合に好適な2種ゲート構造を提供する。

【解決手段】基板1上に窒化シリコン膜よりも比誘電率が大きい高誘電体膜、例えば酸化チタン膜6(内部回路のゲート絶縁膜)を堆積した後、酸化チタン膜6の上部に窒化シリコン膜7を堆積する。窒化シリコン膜7は、次の工程で基板1の表面を熱酸化する時に酸化チタン膜6が酸化されるのを防ぐ酸化防止膜として機能する。次に、内部回路領域に窒化シリコン膜7と酸化チタン膜6を残し、I/O回路領域の窒化シリコン膜7と酸化チタン膜6を除去した後、基板1を熱酸化することによって、I/O回路領域の基板1の表面に酸化シリコン膜8(I/O回のゲート絶縁膜)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】工程数の増加を回避し得る半導体装置及びその製造方法を提供する。

【解決手段】低濃度ドレイン領域28hを形成するためのドーパント不純物が導入される所定領域を除く領域に、所定領域から離間するようにチャネルドープ層22dを形成する工程と、半導体基板10上にゲート絶縁膜24を介してゲート電極26dを形成する工程と、ゲート電極の一方の側の半導体基板内に低濃度ソース領域28gを形成し、ゲート電極の他方の側の半導体基板の所定領域に低濃度ドレイン領域28hを形成する工程とを有している。

(もっと読む)

半導体装置

【課題】 占有面積の増加がなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 内部素子のN型MOSトランジスタやその他の内部素子をESDによる破壊から保護するためのESD保護用のN型MOSトランジスタのチャネル領域の下部に、濃いN型の不純物を有するシリコン領域からなる埋め込みN型領域を配置した半導体装置とした。

(もっと読む)

半導体装置及びその製造方法

【課題】ドレイン耐圧を向上させる半導体装置及びその製造方法を提供すること。

【解決手段】基板100表面内に第1、第2拡散層206を形成する工程と、前記基板上に第1トランジスタを形成する工程と、前記ゲート電極の第1側壁及び第2側壁にそれぞれ第1、第2絶縁膜202を形成することにより、前記第1、第2拡散層の表面の一部の領域を被覆する工程と、この第2拡散層上に第3絶縁膜203を形成する工程と、前記第1〜第3絶縁膜、ゲート電極201、及び前記基板表面をそれぞれ第4絶縁膜204で被覆する工程と、前記ゲート電極の表面、及び第3絶縁膜に対して前記第2絶縁膜と前記第3絶縁膜との間の第1領域と相対する第2領域における前記第2拡散層の表面を露出しつつ、前記第1領域における前記第2拡散層の表面が露出しないよう前記第4絶縁膜を除去する工程とを具備する。

(もっと読む)

半導体装置

【課題】トランジスタ間の分離性が良好な半導体装置を提供する。

【解決手段】半導体装置において、第1導電型の半導体基板と、前記半導体基板の上層部分を複数の能動領域に区画する素子分離絶縁膜と、前記能動領域の上部に相互に離隔して形成された第2導電型のソース層及びドレイン層と、前記半導体基板上における前記ソース層と前記ドレイン層との間のチャネル領域の直上域に設けられたゲート電極と、前記半導体基板と前記ゲート電極との間に設けられたゲート絶縁膜と、第1導電型であり、実効的な不純物濃度が前記半導体基板の実効的な不純物濃度よりも高く、前記能動領域における前記ソース層及び前記ドレイン層の直下域に形成され、前記ゲート電極の直下域には形成されていないパンチスルーストッパ層と、を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な電気的特性を有する半導体装置及びその製造方法を提供する。

【解決手段】質量数が比較的小さいドーパント不純物を導入することにより第1のトランジスタ34a及び第2のトランジスタ34bのチャネルドープ層18を形成する工程と、質量数が比較的大きいドーパント不純物を導入することにより第3のトランジスタ34cのチャネルドープ層20を形成する工程と、質量数の比較的小さいドーパント不純物を導入することにより第1のトランジスタのポケット領域26を形成する工程と、質量数の比較的大きいドーパント不純物を導入することにより第2のトランジスタ及び第3のトランジスタのポケット領域36を形成する工程とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの閾値電圧のバックゲート電圧依存性を低減することができる。

【解決手段】半導体装置100は、基板(例えば、P型半導体基板3)と、基板に形成され素子形成領域1を他の領域と分離する素子分離領域2と、を有している。更に、素子形成領域1上に形成されたゲート電極4を有し、ゲート電極4は、素子分離領域2において素子形成領域1を介して互いに対向する第1及び第2領域2a、2bの上にそれぞれ延伸している。更に、ゲート電極4を基準としてチャネル長方向Dに相互に離間するように素子形成領域1に形成された一対の拡散領域(例えば、N型拡散領域5)を有する。第1領域2a及び第2領域2bの上面の少なくとも一部分ずつは、素子形成領域1の上面よりも下に、チャネル幅Wの5%以上の深さに凹んでおり、それら凹み7内にもゲート電極4の一部分ずつが存在している。

(もっと読む)

半導体装置およびその製造方法

【課題】 LDMOSトランジスタにおいて、オン抵抗とのトレードオフ関係で最適化されたオフ耐圧を低下させることなく、チャネル長を短くすることによって飽和電流を増加させる。

【解決手段】 チャネルとなる低濃度ボディ領域10と素子分離膜4の間かつゲート酸化膜8の直下に選択的に低濃度ボディ領域10と逆の極性で濃度が高いショートチャネル領域12を設け、ボディ領域10のゲート酸化膜8直下部分のみを高濃度ソース領域7側に後退させた形状を実現する。

(もっと読む)

半導体装置

【課題】選択素子のビット線方向の長さを短縮する。

【解決手段】半導体装置は、第1導電型の半導体基板10と、半導体基板10に形成された溝に埋設された第1の絶縁膜領域11と、第1の絶縁膜領域11の下面11cを覆うゲート電極WL、ゲート電極WLと半導体基板10の間に設けられるゲート絶縁膜14、を備え、更に、第1の絶縁膜領域11の第1の側面11aを覆う第1の拡散領域15、第1の絶縁膜領域11の第2の側面11bを覆う第2の拡散領域16、及び第2の拡散領域16の上面を覆う第3の拡散領域17とを備え、選択素子は、ゲート電極WL、第1の拡散領域15及び第2の拡散領域16で構成される電界効果トランジスタ、及び基板及び第2及び第3の拡散領域で構成されるバイポーラトランジスタを含む。選択素子の長さが3F(Fは最小加工寸法)で足りるので、埋め込みゲート電極WLを含めて選択素子のビット線方向の長さの短縮が可能。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

MISFET及びその製造方法

【課題】 LDD領域の長さを精度良く調整可能で、高周波動作に適用できる非対称な横方向二重拡散型MISFETを提供する。

【解決手段】 第1導電型のウェル1の上方にゲート絶縁膜3を介してゲート電極5を形成する工程、ウェル1に第2導電型の不純物イオン注入によりドレイン領域7を形成する工程、ウェル1の上方にゲート電極5が形成されるゲート電極領域とドレイン領域7を少なくとも覆い、ゲート電極領域とドレイン領域の間が開口したマスクパターン層を形成する工程、マスクパターン層をマスクとして自己整合的に、マスクパターン層で覆われていない領域に第2導電型の不純物イオン注入によりドレイン領域より低濃度のLDD拡散領域6を形成する工程、及び、ウェル1のゲート電極5を挟んでドレイン領域7の反対側の領域に第2導電型の不純物イオン注入によりLDD拡散領域より高濃度のソース領域を形成する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】DRAM素子のような半導体装置において、半導体基板の溝部におけるゲート電極の埋設状態が良好となり、配線抵抗が低減され、素子特性に優れた半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の表面にゲート電極溝13を形成する工程と、ゲート電極溝13の内面に第1のバリア膜16aを形成する工程と、第1のバリア膜16aをエッチバックして、ゲート電極溝13の底面に第1のバリア膜16aの一部を残存させながら除去する工程と、ゲート電極溝13の内面と残存した第1のバリア膜16aの表面に第2のバリア膜16bを形成する工程と、第2のバリア膜16aの表面にタングステン膜を形成する工程と、このタングステン膜及び第2のバリア膜16bをエッチバックしてゲート電極溝13内にそれぞれ一部を残存させながら各膜を一括除去する工程と、を具備する。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置の製造装置

【課題】希釈された溶液を用いて、貴金属を含む被処理膜等を迅速に且つ効果的にエッチングでき、且つ、設備の稼働率を向上できるようにする。

【解決手段】薬液を調合する薬液調合槽24と、調合された薬液を貯蔵する薬液貯蔵槽28と、貯蔵された薬液を用いて半導体基板を処理する処理チャンバ21とを有する半導体装置の製造装置を用いた半導体装置の製造方法は、薬液調合槽24において、酸化剤と錯化剤とを混合して第1の薬液を調合し、薬液調合槽24において、第1の薬液を活性化する。続いて、薬液貯蔵槽28において、活性化された第1の薬液と純水とを混合し、第1の薬液の濃度及び温度を調整することにより、第1の薬液を希釈した第2の薬液を調整する。続いて、処理チャンバ21に投入された半導体基板に第2の薬液を供給する。

(もっと読む)

半導体装置と論理回路およびその製造方法

【課題】インパクトイオン化MISFETに関して、微細素子において二つの入力によりAND型論理素子動作することを可能とし、素子バラツキを低減することを可能とし、消費電力を低減することを可能とする半導体装置を提供する。

【解決手段】第1導電型または真性である半導体領域の表面上に形成された二つの独立した第一および第二のゲート電極への両者への入力により反転層が形成された場合に、インパクトイオン化によるスイッチング動作が可能となることを特徴とする、半導体装置である。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路(1000)が、中央配置のドレイン拡散領域(1008)及び分散型SCR端子(1010)を備える1つのドレイン構造(1006)と、分散型ドレイン拡散領域(1016)及びSCR端子(1018)を備える別のドレイン構造(1012)とを含むSCRMOSトランジスタを有する。中央配置のドレイン拡散領域とソース拡散領域との間のMOSゲート(1022)がソース拡散領域へ短絡される。SCRMOSトランジスタを有する集積回路を形成するためのプロセスも開示される。  (もっと読む)

(もっと読む)

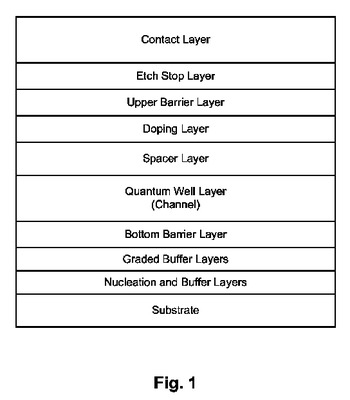

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

量子井戸トランジスタへのコンタクトを形成する方法

半導体へテロ構造内に形成されたデバイスへの低抵抗自己整合コンタクトを供する方法が開示されている。当該方法はたとえば、III-V族及びSiGe/Ge材料系において作製される量子井戸トランジスタのゲート、ソース、及びドレイン領域へのコンタクトを形成するのに用いられてよい。ゲートへのソース/ドレインコンタクト間に比較的大きな空間を生成してしまう従来のコンタクト作製処理の流れとは異なり、当該方法により供されたソースとドレインのコンタクトは自己整合され、各コンタクトは、ゲート電極に対して位置合わせされ、かつ、スペーサ材料を介して前記ゲート電極から分離される。  (もっと読む)

(もっと読む)

101 - 120 / 648

[ Back to top ]