Fターム[5F140AB01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 複合(回路要素) (3,149) | MOSIC、MISIC (2,326)

Fターム[5F140AB01]の下位に属するFターム

E/EMOS、E/DMOSを構成するもの (22)

CMOSを構成するもの (1,656)

Fターム[5F140AB01]に分類される特許

61 - 80 / 648

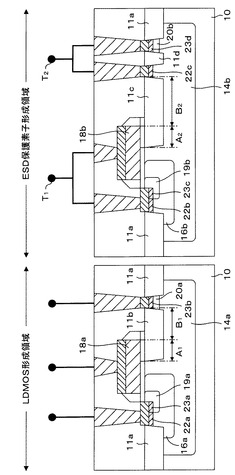

半導体装置及びその製造方法

【課題】LDMOSトランジスタとESD保護素子とを有する半導体装置において、製造工程が簡単であるとともに、所望の特性を確保しつつ従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】LDMOSトランジスタ形成領域のゲート電極18aと素子分離膜11bの重なり幅をA1、ゲート電極18aとドレイン領域23bとの間隔をB1とし、ESD保護素子形成領域のゲート電極18と素子分離膜11cとの重なり幅をA2、ゲート電極18bとアノード領域22cとの間隔をB2としたときに、A1≧A2、且つB1<B2の関係を満足するように、ゲート電極18a、素子分離膜11b、ドレイン領域20a、ゲート電極18b、素子分離膜11c及び前記アノード領域22cを形成する

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数やコストを増加させることなく、信頼性の高い高耐圧pチャネル型トランジスタが形成された半導体装置を提供する。

【解決手段】主表面を有し、かつ内部にp型領域を有する半導体基板SUBと、p型領域PSR上であって主表面に配置された、ドレイン電極DRを取り出すための第1のp型不純物領域PRを有するp型ウェル領域PLDと、主表面に沿う方向に関してp型ウェル領域PLDと接するように配置された、ソース電極SOを取り出すための第2のp型不純物領域PRを有するn型ウェル領域NWRと、主表面に沿う方向に関して、第1のp型不純物領域PRと第2のp型不純物領域PRとの間に配置されたゲート電極GEと、n型ウェル領域NWRの上に配置された、主表面に沿って延びるp型埋め込みチャネルPPRとを含んでいる。上記n型ウェル領域NWRとp型ウェル領域PLDとの境界部は、ゲート電極GEの、第1のp型不純物領域PRに近い側の端部よりも、第1のp型不純物領域PRに近い位置に配置される。

(もっと読む)

マイクロローディング効果を軽減するためのSiGe埋め込みダミーパターンを備えたSiGe装置

【課題】SiGe装置を取り囲んで、SiGeのエピタキシャル成長時にマイクロローディング効果を軽減できるように特別に設計されたSiGe埋め込みダミーパターンを備えた改良されたSiGe装置を提供する。

【解決手段】マイクロローディング効果を軽減するためのダミーパターンを備えた半導体装置は、内部領域200と外部領域400の間に中間環状領域300が設けられた半導体基板1と、基板上、内部領域200に設けられたSiGe装置100と、基板上、中間環状領域300に設けられた複数のダミーパターン20とを含む。複数のダミーパターン20のうち少なくとも1つがSiGeを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置

【課題】高周波特性を低下させることなくLDMOSFETを有するチップの面積を縮小する。

【解決手段】LDMOSFETのソース領域と基板1の裏面に形成されたソース裏面電極36とを電気的に接続するp型打ち抜き層4を不純物を高濃度でドープした低抵抗のp型多結晶シリコン膜もしくは低抵抗の金属膜から形成する。そして、LDMOSFETの基本セルのソース同士を電気的に接続するソース配線は配線24Aのみとし、ソース配線を形成する配線層数は、ドレイン配線(配線24B、29B、33)を形成する配線層数より少なくする。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】構造が簡単なトランジスタにより、サステイン耐圧を改善し且つサステイン耐圧のばらつきの抑制及びトランジスタ形成後のドレイン抵抗及び接合プロファイルの調整が可能な、自由度が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型ウェル102に形成され、互いに並行に延びると共に、ゲート長方向の幅が比較的に大きい第1ゲート電極125と、ゲート長方向の幅が比較的に小さい第2ゲート電極126と、p型ウェル102における第1ゲート電極125及び第2ゲート電極126同士の間に形成されたLDD低濃度領域135と、該p型ウェル102における第1ゲート電極125及び第2ゲート電極126のそれぞれの外側に形成されたLDD中濃度領域134とを有している。LDD低濃度領域135の不純物濃度は、LDD中濃度領域134の不純物濃度よりも低い。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

半導体装置およびその製造方法、固体撮像素子、電子情報機器

【課題】従来のようにトランジスタゲート面積を大きくすることなく、より簡単な製造工程で、トランジスタのソース側ゲート端のイオン注入ダメージにより発生するソース側ゲート端付近の欠陥を低減することにより、ランダムノイズを効果的に低減する。

【解決手段】ドレイン側のLDD領域のN型拡散層11だけがゲート電極6の他方端の下に潜り込んで、ドレイン側のLDD領域のN型拡散層11がゲート電極6と平面視でオーバラップし、ソース側のLDD領域のN型拡散層12はゲート電極6の一方端の下に潜り込まず、ソース側のLDD領域のN型拡散層12がゲート電極6と平面視でオーバラップしておらず、ソース側のLDD領域のN型拡散層12がゲート電極6の一方端と離間して形成されている。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体デバイス及びその駆動方法

【課題】半導体デバイスの小面積化を実現する。

【解決手段】電極と、第1絶縁体と、バンドギャップが2eV以上の第1半導体と、第2絶縁体と、第2半導体とが積層されており、第1半導体に接する1つ以上の電極と、第2半導体に接する2つ以上の電極とを少なくとも備えることを特徴とする半導体デバイス。

(もっと読む)

半導体装置および電力変換器

【課題】部品点数を増やすことなく、SiC半導体装置の結晶劣化の進行を抑制することが可能な半導体素子を提供する。

【解決手段】p型コレクタ域91およびn型コレクタ領域92を含むコレクタ層93と、n型半導体層20と、p型ボディ領域30と、n型エミッタ領域40と、ボディ領域30に接して形成されたチャネルエピ層50と、エミッタ電極45と、ゲート絶縁膜60と、ゲート電極65と、コレクタ電極70とを備える構造とする。双方向導通IGBT100のゲート電極65に印加する電圧が閾値電圧よりも小さい場合、エミッタ電極45からチャネルエピ層50を介してコレクタ電極70へ電流を流すダイオードとして機能させる。

(もっと読む)

半導体装置の製造方法

【課題】レーザ光の照射を利用したエッチング加工による半導体装置の製造方法であって、複雑形状や深くて大きい除去領域等のエッチング加工が必要な広範囲の半導体装置の製造に適用可能で、高いエッチング速度が得られる半導体装置の製造方法を提供する。

【解決手段】単結晶シリコンからなる基板10に対して、焦点位置を移動させてレーザ光Lをパルス照射し、前記単結晶シリコンを部分的に多結晶化して、前記単結晶シリコン中に連続した改質層11を形成する改質層形成工程と、前記改質層11をエッチングして除去するエッチング工程と、を備える半導体装置の製造方法とする。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極断線の確率を下げる。

【解決手段】半導体装置1の製造方法は、シリコン基板2の主面に絶縁体ピラー6を形成する工程と、絶縁体ピラー6の側面に保護膜12を形成する工程と、シリコン基板2の主面にシリコンピラー4を形成する工程と、シリコンピラー4の側面にゲート絶縁膜10を形成する工程と、それぞれシリコンピラー4及び絶縁体ピラー6の側面を覆い、互いに接する第1及び第2のゲート電極11,13を形成する工程とを備える。本製造方法によれば、ダミーピラーとしての絶縁体ピラー6の側面に保護膜12を形成しているので、チャネル用のシリコンピラー4をトランジスタとして加工する際にダミーピラーが削られてしまうことが防止される。したがって、ゲート電極断線の確率を下げることが可能になる。

(もっと読む)

半導体装置の製造方法

【課題】1回のゲート絶縁膜形成工程で複数の厚みのゲート絶縁膜を同一の半導体基板上に形成することができるとともに、ゲート絶縁膜に酸化促進物質による欠陥が発生するのを抑制することができる半導体装置の製造方法の提供。

【解決手段】半導体基板の所定領域に拡散性を有する酸化促進物質を注入する酸化促進物質注入工程と、上記半導体基板に熱処理を行うことで当該半導体基板に上記酸化促進物質の注入量に応じた複数の厚みの酸化膜を形成する酸化膜形成工程と、上記所定領域に注入された酸化促進物質を拡散させることで上記酸化膜中に存在する上記酸化促進物質の濃度を低下させる酸化促進物質拡散工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体デバイス、その製造方法及び集積回路

【課題】電極領域の抵抗を従来よりも一段と低減させることができる半導体デバイス、その製造方法及び集積回路を提供する。

【解決手段】III−V族化合物半導体層4上にニッケル層17を形成し、RTA処理により加熱することで、ニッケルIII−V族合金(Ni-InxGa1-xAsyP1-y合金)からなるソース領域5及びドレイン領域6が形成される。これにより、MOSFET1では、III−V族化合物半導体層4に対して単に不純物をインプラテーションで注入して形成された従来のソース領域及びドレイン領域の寄生抵抗に比べて、ソース領域5及びドレイン領域6の寄生抵抗を一段と低減させることができる。

(もっと読む)

61 - 80 / 648

[ Back to top ]