Fターム[5F140AB06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 複合(回路要素) (3,149) | ダイオード (159)

Fターム[5F140AB06]に分類される特許

1 - 20 / 159

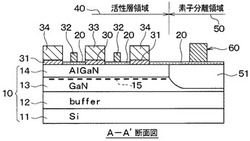

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの特性のばらつきを低減するために有利な技術を提供する。

【解決手段】MOSトランジスタを含む半導体装置の製造方法は、半導体基板の上に形成された第1絶縁膜の上にゲート電極材料層を形成する工程と、前記ゲート電極材料層の上にエッチングマスクを形成する工程と、前記ゲート電極材料層をパターニングすることによりゲート電極を形成する工程と、前記ゲート電極が形成された前記半導体基板の上に第2絶縁膜を形成する工程とを含み、前記ゲート電極を形成する工程では、前記ゲート電極材料層がパターニングされるとともに、少なくとも、前記ゲート電極の側面の下部と、前記第1絶縁膜のうち前記側面に隣接する部分とを保護する保護膜が形成され、前記第2絶縁膜を形成する工程では、前記保護膜を覆うように前記第2絶縁膜が形成される。

(もっと読む)

半導体装置

【課題】チップ面積を増大させずにスナップバック現象を抑制することのできる、IGBTと他の半導体素子とが一体化して配置された半導体装置を提供する。

【解決手段】IGBTとドリフト層を有する他の半導体素子とを備えた半導体装置であって、IGBTのドリフト層と他の半導体素子のドリフト層とが互いに接しており、IGBTのエミッタ層と他の半導体素子のドリフト電界を発生させる電圧が印加される一方の極性層とが互いに導電的に接続されており、IGBTのコレクタ層と他の半導体素子の他方の極性層とが互いに導電的に接続されており、IGBTのドリフト層の他の半導体素子のドリフト層との境界から離れた領域に絶縁層を介して対向する領域をドリフト方向に沿って延伸し、Nチャネル型IGBTではコレクタ側からエミッタ側に向けて電流が流され、Pチャネル型IGBTではエミッタ側からコレクタ側に向けて電流が流される配線部が設けられている。

(もっと読む)

窒化物半導体装置

【課題】内蔵する環流ダイオードの順方向電圧が低く、高耐圧で、低オン抵抗の、ノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】窒化物半導体装置は、基板1、第1の窒化物半導体層3、第2の窒化物半導体層4、及び第2の窒化物半導体層上4に設けられた、ソース電極5、ドレイン電極6、第1のゲート電極9、ショットキー電極10、第2のゲート電極12、を備える。第2の窒化物半導体層4と第1の窒化物半導体層3との界面には、2次元電子ガスが形成される。第1のゲート電極9はノーマリオフ型FET20のゲート電極であり、ソース電極5とドレイン電極6との間に設けられる。ショットキー電極10は、第1のゲート電極9とドレイン電極6との間に設けられる。第2のゲート電極12はノーマリオン型FET21のゲート電極であり、ショットキー電極10とドレイン電極6との間に設けられる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】特性の低下を抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、が含まれている。p型半導体層8に含まれるp型不純物として、少なくとも電子走行層3及び電子供給層5のいずれかを構成する元素と同種の元素が用いられている。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

半導体装置

【課題】小型でコストが低い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、導電形がp形のソース領域と、導電形がp形のドレイン領域と、前記ソース領域と前記ドレイン領域との間に設けられ、導電形がn形のチャネル領域と、前記チャネル領域上に設けられた下側ゲート絶縁膜と、前記下側ゲート絶縁膜上に設けられた下側ゲート電極と、前記下側ゲート電極上に設けられた上側ゲート絶縁膜と、前記上側ゲート絶縁膜上に設けられた上側ゲート電極と、前記下側ゲート電極と前記ソース領域との間に接続されたスイッチング素子と、を備える。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

窒化物系半導体装置

【課題】ダイオード部とトランジスタ部の面積比率を自由に設定することが可能な窒化物系半導体装置を提供することを目的とする。

【解決手段】第1HEMT部30及び第2HEMT部31から成るトランジスタ部1と、第1電極24と電気的に短絡された第1ショットキー電極28及び第1ゲート電極26と電気的に第2ショットキー電極29から成るダイオード部2と、を備えて構成されている。また、第1電極24と第2電極25との間の領域に第1電極24に沿って、第1ゲート電極26及び第1ショットキー電極28が交互に形成され、かつ、第2電極25に沿って、第2ゲート電極27及び第2ショットキー電極29が交互に形成されている。さらに、第1ゲート電極26と第2ゲート電極27とは、対向して形成されており、第1ショットキー電極28と第2ショットキー電極29とは対向して形成されている。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】SiCが用いられる半導体層中において、簡易な工程で再現性よく埋め込み絶縁層を形成する。

【解決手段】単結晶のSiC12の表面の温度を局所的に急激に上昇させ、その後で急激に冷却することによって、単結晶を局所的に非晶質化層30を形成することができる。この非晶質層30は、元の単結晶SiCの導電型や抵抗率に関わらず、高抵抗層(絶縁層)となる。このため、こうした非晶質層を埋め込み絶縁層と同様に使用することができる。このためには、(1)レーザー光を効率的に吸収する層100を局所的に半導体層の上に形成してからレーザー光を照射する、(2)レーザー光を局所的に半導体層に照射する、という2つの手段のいずれかを用いることができる。

(もっと読む)

撮像装置の製造方法

【課題】プラズマ酸化によりシリコン基板上に形成される酸化膜の金属汚染量を低減すること。

【解決手段】酸化膜の形成方法は、不活性ガスと、前記不活性ガスに対する混合割合が0よりも大きく且つ0.007以下である酸化ガスと、を含む混合ガスからプラズマを生成する工程と、前記プラズマを用いてシリコン基板の表面に酸化膜を形成する工程と、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置

【課題】 本発明の目的は、半導体装置単体で負電源を必要とせずにスイッチングが可能な素子を提供することである。

【解決手段】 この発明の半導体装置は、ノーマリオンFETと、一方の電極を前記FETのゲートに、他方の電極を入力端子に電気的に接続されたキャパシタと、アノード電極が前記FETのゲートに、カソード電極が前記FETのソースに電気的に接続されたダイオードと、を前記FETと同一チップ上に形成したことを特徴としており、さらに、前記キャパシタが、前記FETのゲート引き出し電極上に誘電体などの絶縁膜を形成し、形成した前記絶縁膜に金属膜を形成することにより形成されたことが好ましい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】シンカー層を含むエピタキシャル層の厚さを増大させても耐圧性能の向上が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、第1導電型の埋め込み拡散層16Na,16Nd,16Nbを有する支持基板10と、第1導電型と同じ導電型のシンカー層21Na,21Nbを有するエピタキシャル層20と、シンカー層21Na,21Nbから離れた領域でエピタキシャル層20上に形成された電極層31とを備える。支持基板10の上層部は、エピタキシャル層の上面に向けて突出する凸状部10Pa,10Pbを有し、シンカー層21Na,21Nbは、エピタキシャル層20の上面近傍から凸状部10Pa,10Pbにおける埋め込み拡散層16Na,16Nbにまで延在する不純物拡散領域からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の表面に導入された不純物を、前記表面の浅い領域に高精度かつ高濃度で分布させ、不純物が半導体基板の深い領域に拡散することを防ぐことで、半導体装置の歩留まりおよび性能を向上させ、装置の微細化を容易にする。

【解決手段】N型MISトランジスタにおいて、半導体基板300に打ち込まれた炭素が、同じ領域に打ち込まれたホウ素を引き寄せる性質を利用し、ホウ素をN型の不純物として注入したハロー領域306に炭素を共注入して炭素注入層307を形成する。これにより、ホウ素が増速拡散することを防ぎ、ハロー領域306を高い精度で形成することを可能とすることで、微細化された半導体素子の短チャネル効果の発生を抑制する。

(もっと読む)

III−V族トランジスタとIV族ダイオードを含む積層複合デバイス

【課題】III−V族トランジスタとIV族ダイオードからなる積層複合デバイスを提供する。

【解決手段】積層複合デバイスはIV族ダイオードと該IV族ダイオードの上に積層されたIII−V族トランジスタとを備える。IV族ダイオードのカソードがIII−V族トランジスタのソースと接触され、IV族ダイオードのアノードがIII−V族トランジスタのゲートに結合されて前記複合デバイスパッケージの底面上の複合アノードを与え、III−V族トランジスタのドレインが複合デバイスパッケージの底面に対向する上面上の複合カソードを与える。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

1 - 20 / 159

[ Back to top ]