Fターム[5F140AC28]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 歪みを利用したもの (848)

Fターム[5F140AC28]に分類される特許

101 - 120 / 848

III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス、及びその製造方法

【課題】III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス及びその製造方法を提供する。

【解決手段】III−V族材料のエネルギーレベルの密度とドーピング濃度をIII−V族材料とIV族材料のヘテロエピタキシと素子の構造設計によって高める。本発明の方法は、基板100上にダミーゲート材料層を堆積し、フォトリソグラフィでダミーゲート材料層にダミーゲートを区画することと、ダミーゲートをマスクとして使用し、セルフアライン型イオン注入によってドーピングを行い、高温で活性化を行い、ソース−ドレイン108を形成することと、ダミーゲートを除去することと、ソース−ドレインのペアの間の基板にエッチングで凹陥部を形成することと、凹陥部にエピタキシャル法によりチャネル含有スタック素子112を形成することと、チャネル含有スタック素子上にゲート120を形成することと、を含む。

(もっと読む)

単電子ターンスタイルデバイスおよびその製造方法

【課題】より小さな単電子島が作製でき、また、高い精度を必要とせずにトップゲートが配置できるようにする。

【解決手段】形成しようとする細線の延在方向に対して直交して開口部104を挟む2つの箇所に、対向して配置される2つの溝部105を形成する。溝部105は、絶縁層101に到達するまで形成する。次に、酸化シリコン層103を介してシリコン層102の上層部を熱酸化し、シリコン層102をより薄くする。この酸化工程により、開口部104の対向する2つの曲線状の縁部に対応する曲線状の境界部の内側近傍において、層厚方向にくびれるくびれ部107が形成され、くびれ部107においては、シリコン層102の層厚がより薄くなり、層厚方向の量子サイズ効果によりトンネルバリアが形成されるようになる。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層とSi層との界面における抵抗が低いMOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成された、チャネル移動度に実質的な影響を与えないSiGe層15と、SiGe層15上に形成されたSi層16と、半導体基板2、SiGe層15、およびSi層16内のゲート電極12の両側に形成されたn型ソース・ドレイン領域19と、Si層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体素子及びトランジスタ

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができる半導体素子及びトランジスタを提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができる半導体素子及びトランジスタを提供すること、を目的とする。

【解決手段】半導体基板上に形成されて第1半導体パターンを含む3次元直線状の第1構造物と、第一構造物の中心部を貫通するように配置され、第1半導体パターンと異なる結晶構造を有する第2半導体パターンを含む第2構造物と、第1構造物に対して直交する方向に延長して3面で第2構造物の一部を囲むゲートを含むトランジスタとする。

(もっと読む)

FINFETSおよびその形成方法

【課題】フィン電界効果トランジスタのソース/ドレイン構造を提供する。

【解決手段】基板上のフィンチャネル本体110a、110b、フィンチャネル本体110a、110b、上に配置されたゲート電極115、およびフィンチャネル本体110a、110b、に隣接して配置され、どのフィン構造も実質的に含まない、少なくとも1つのソース/ドレイン(S/D)領域120a,120b及び125a,125bを含むフィン電界効果トランジスタ(FinFET)。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

トランジスタの製造方法

【課題】ゲートとチャンネル部との接触面を増大させ電流の損失を減らし、チャンネルを形成する半導体層の格子特性を変化させ電子移動度を向上させることができるトランジスタの製造方法を提供すること、及び、ゲートと接触する面積が増大され、半導体層の格子特性も向上されてチャンネル部内の電子の流れを改善し、電力消耗も減らすことができるトランジスタの製造方法を提供すること、を目的とする。

【解決手段】半導体基板上に第1半導体層及び第1半導体層と異なる格子定数と結晶構造を有する第2半導体層を順次形成する段階と、第2半導体層及び第1半導体層をエッチングして格子定数の差によって第1半導体層の結晶構造が変形された変形結晶構造を有し、直線状の第1半導体パターンを形成する段階と、第1半導体パターン上に第1半導体層と同一な結晶構造を有する第3半導体層を形成する段階とを含む。

(もっと読む)

自己整合損傷層を有するデバイス構造体の形成方法

【解決課題】 自己整合損傷層を有するデバイス構造体の形成方法を提供すること。

【解決手段】デバイス構造体は、基板の半導体材料内部に画定された第1導電型の第1及び第2ドープ領域を有する。逆の導電型の第3ドープ領域が、横方向に第1ドープ領域を第2ドープ領域から分離する。ゲート構造部が基板の上表面に配置され、第3ドープ領域と垂直方向で重なる関係を有する。第1結晶損傷層は基板の半導体材料の内部に画定される。第1結晶損傷層は、基板の半導体材料によって取り囲まれた第1の複数のボイドを有する。第1ドープ領域は、第1結晶損傷層と基板の上表面との垂直方向の間に配置される。第1結晶損傷層は横方向に第3ドープ領域内には延びない。

(もっと読む)

半導体装置

【課題】温度が上昇するほど電子又はホールの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板中のPウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Pウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ負の膨張係数を有しチャネル領域に引っ張り応力を加える第1絶縁層20を備えたN型の絶縁ゲート型電界効果トランジスタN1と、半導体基板中のNウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Nウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ正の膨張係数を有しチャネル領域に圧縮応力を加える第2絶縁層30を備えたP型の絶縁ゲート型電界効果トランジスタP1とを具備する。

(もっと読む)

シリコン選択エッチ方法

基板上に設けられるシリコン層をエッチングする方法は、シリコン層に第1のトレンチを異方性エッチングすること;第1のトレンチ内のシリコン表面を選択的に異方性ウェットエッチングすることであって、該ウェットエッチングが、シリコン表面を、芳香族トリ(低級)アルキル第四級オニウム水酸化物と、非対称テトラアルキル第四級ホスホニウム塩とを含む水性組成物に曝すことを含み、該ウェットエッチングが、シリコン層の(110)面及び(100)面をおよそ等しい速度で(111)面よりも優先的にエッチングして、(111)面に側壁を有する拡大されたトレンチを形成する、選択的に異方性ウェットエッチングすることを含む。応力をシリコン層の少なくとも一部分に導入するプロセスの一環として、このようにして作製したトレンチ内にシリコン合金をエピタキシャル堆積させてもよい。 (もっと読む)

半導体ヘテロ電界効果トランジスタ

【課題】ピエゾ電界により発生するシートキャリアの利用とチャネル部におけるピエゾ電界により深いディプレッション形成の抑制とを提供できる半導体ヘテロ電界効果トランジスタを提供する。

【解決手段】第1及び第3の領域23a、23cの主面24a、24cの法線ベクトルNV1、NV3は、該III族窒化物半導体のc軸Cxに直交する面に対して有限な角度で傾斜する。第2の領域23bの主面24bの法線ベクトルNV2は、該III族窒化物半導体のc軸Cxに直交する面に沿って延在する。第2の領域23bにおけるチャネル層25の第2の領域25bのピエゾ分極PZC2は、III族窒化物半導体領域23からバリア層27への方向に向いている。第1及び第3の領域23a、23cにおけるチャネル層25の第1及び第3の領域25a、25cのピエゾ分極PZC1、PZC3は、バリア層27からIII族窒化物半導体領域23への方向に向いている。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

金属ゲートとストレッサーを有するゲルマニウムフィンFET

【課題】金属ゲートとストレッサーを有するゲルマニウムフィンFETを提供する。

【解決手段】集積回路構造は、n型フィン電界効果トランジスタ(fin field effect transistor、FinFET)とp型FinFETからなる。n型FinFETは、基板上の第一ゲルマニウムフィン、第一ゲルマニウムフィンの上面と側壁上の第一ゲート誘電体、及び、第一ゲート誘電体上の第一ゲート電極からなる。p型FinFETは、基板上の第二ゲルマニウムフィン、第二ゲルマニウムフィンの上面と側壁上の第二ゲート誘電体、及び、第二ゲート誘電体上の第二ゲート電極からなる。第一ゲート電極と第二ゲート電極は、ゲルマニウムの固有エネルギーレベルに近い仕事関数を有する同一材料で形成される。

(もっと読む)

半導体装置とその製造方法

【課題】SiGe層を用いてPチャネル型トランジスタのチャネル形成領域に圧縮応力を印加すると共に、リーク電流を低減する。

【解決手段】半導体装置120は、半導体基板100の表面部に形成されたソース領域及びドレイン領域122と、これらに挟まれたチャネル形成領域上にゲート絶縁膜101を介して形成されたゲート電極102とを含むPチャネル型トランジスタを備える。ゲート電極102の両側それぞれにおいて半導体基板100にリセスが形成され、リセスに、SiGeからなる第1エピタキシャル層111と、その上に形成され且つSiからなる第2エピタキシャル層112と、その上に形成され且つSiGeからなり、チャネル形成領域を挟む第3エピタキシャル層113とを備える。ソース領域及びドレイン領域122は、第3エピタキシャル層113中に形成され、且つ、それぞれの接合深さがいずれも第3エピタキシャル層133の深さよりも浅い。

(もっと読む)

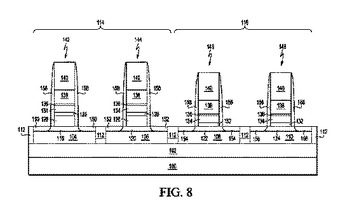

酸素拡散バリア層を有する半導体デバイスおよびそれを製造するための方法

方法および装置はトランジスタを製造するために提供される。トランジスタが、半導体材料104、106、108、110上に配置されたゲートスタック142、144、146を備える。ゲートスタックが、半導体材料上に堆積される酸化物層126、堆積された酸化物層上に配置された酸素拡散バリア層128、酸素拡散バリア層上に配置された高誘電率の誘電体層134、および高誘電率の誘電体層上に配置された酸素ゲッター導電性層138を備える。酸素拡散バリア層が、堆積された酸化物層から酸素ゲッター導電性層への酸素の拡散を防止する。  (もっと読む)

(もっと読む)

埋め込みストレッサを有する高性能FETを形成するための方法および構造

【課題】 高性能の半導体構造およびかかる構造を製造する方法を提供する。

【解決手段】 半導体構造は、半導体基板12の上面14上に位置する、例えばFETのような少なくとも1つのゲート・スタック18を含む。構造は更に、少なくとも1つのゲート・スタックのチャネル40上にひずみを誘発する第1のエピタキシ半導体材料34を含む。第1のエピタキシ半導体材料は、少なくとも1つのゲート・スタックの対向側に存在する基板内の1対のくぼみ領域28の実質的に内部で少なくとも1つのゲート・スタックの設置場所に位置する。くぼみ領域の各々において第1のエピタキシ半導体材料の上面内に拡散拡張領域38が位置する。構造は更に、拡散拡張領域の上面上に位置する第2のエピタキシ半導体材料36を含む。第2のエピタキシ半導体材料は、第1のエピタキシ半導体材料よりも高いドーパント濃度を有する。

(もっと読む)

蓄積型FINFET、回路、及びその製造方法

【課題】FinFET、集積回路、およびFinFETの形成方法を提供する。

【解決手段】基板120、前記基板上にあり、ソース106とドレイン110との間のチャネル108を含み、前記ソース106、前記ドレイン110、および前記チャネル108は、第1型ドーパントを有し、前記チャネル108は、ゲルマニウム、シリコンゲルマニウム、またはIII−V族半導体の少なくとも1つを含むフィン構造、前記チャネル108上のゲート誘電体層114、および前記ゲート誘電体層114上のゲート116を含むFinFET。

(もっと読む)

集積回路構造及びその製造方法

【課題】 非対称的なソース及びドレイン領域を有する構造を提供する。

【解決手段】 本発明の方法は、少なくとも1つの半導体チャネル領域を有する基板と、半導体チャネル領域を覆うように基板の上面に設けられたゲート誘電体層と、ゲート誘電体層上のゲート導電体とを有する構造を形成する。非対称的な側壁スペーサがゲート導電体の側壁に配置され、そして非対称的なソース及びドレイン領域が半導体チャネル領域に隣接して基板内に配置される。ソース及びドレイン領域の一方は、他方よりもゲート導電体の中心に近づけられる。ソース及びドレイン領域は、半導体チャネル領域に物理的な応力を与える材料で構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSFETの性能をより向上する。

【解決手段】半導体装置の製造方法は、半導体基板11上に、ゲート絶縁膜材料とメタルゲート電極材料とを含む積層膜を堆積する工程と、マスク層19を用いて積層膜を加工し、半導体基板11上にゲート絶縁膜15及びメタルゲート電極16を含むゲート構造を形成する工程と、ゲート構造の側面に、絶縁物からなる側壁20を形成する工程と、側壁20をマスクとして半導体基板11に不純物を導入し、エクステンション領域21及びハロー領域22を形成する工程と、側壁20をマスクとして半導体基板11を掘り下げ、半導体基板11にリセス領域26を形成する工程と、リセス領域26にSiGe層27を形成する工程と、側壁20の側面に、絶縁物からなる側壁28を形成する工程と、マスク層19をドライエッチングする工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

101 - 120 / 848

[ Back to top ]