Fターム[5F140BE01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜の製造 (6,009) | ゲート絶縁膜を形成前の処理 (668)

Fターム[5F140BE01]の下位に属するFターム

Fターム[5F140BE01]に分類される特許

21 - 40 / 117

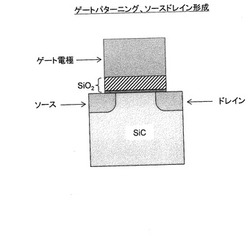

絶縁膜形成方法、及び該方法により得られた酸化膜をゲート絶縁膜として用いる半導体装置

【課題】チャネル部分へのC原子の偏積と酸化膜内へのC原子の蓄積を独立に制御かつ低減する。

【解決手段】半導体基板の表面を熱酸化して、薄い熱酸化膜を成長させ、所望の二酸化ケイ素SiO2絶縁膜厚=前記熱酸化膜の膜厚+堆積したシリコン膜厚の100/44倍、の関係になるようにして求めた膜厚のシリコンを、熱酸化膜の上に堆積する。この堆積したシリコンを熱酸化することにより、所望の膜厚の二酸化ケイ素SiO2絶縁膜を得る。この二酸化ケイ素SiO2絶縁膜の上に、ゲート電極をデポジションしてパターニングし、かつ、ソースドレイン形成をする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の侵食を抑制し、FETの故障や不良の発生を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】基板10上にGaN系半導体層15を形成する工程と、GaN系半導体層15上に酸化アルミニウムからなるゲート絶縁膜18を450℃以下の成膜温度で形成する工程と、ゲート絶縁膜18の上面に保護膜19を形成する工程、ゲート絶縁膜18を熱処理する工程、及びゲート絶縁膜18をプラズマ処理する工程のいずれか一つと、前記いずれか一つの工程の後に、ゲート絶縁膜18を形成する工程の後のアルカリ溶液を用いた処理を実行する工程と、前記ゲート絶縁膜18上にゲート電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】低閾値電圧動作が可能な電界効果トランジスタを提供する。

【解決手段】n型半導体基板2と、半導体基板に離間して形成されたソースおよびドレイン領域12a、12bと、ソース領域とドレイン領域との間の半導体基板上に形成され、Hf、Zr、Tiから選ばれた少なくとも1つの物質と酸素を含む第1絶縁膜4と、第1絶縁膜上に形成され、シリコンと酸素を含む第2絶縁膜8と、第2絶縁膜上に形成されたゲート電極10と、を備え、V、Cr、Te、P、As、S、Seの群から選ばれた少なくとも一つの第1物質と、窒素とが第1絶縁膜と第2絶縁膜との界面を含む界面領域7に含まれ、第1物質の面密度が界面領域内の第2絶縁膜側において第1ピークを有し、窒素の面密度が界面領域内に第2ピークを有し、第2ピークの位置が、第1ピークの位置よりも半導体基板側にある。

(もっと読む)

半導体ゲート絶縁膜の形成方法

【課題】 低温の酸素ラジカルで酸化した膜は、初期特性こそ従来の熱酸化膜同等以上の特性を得られるが、各種のストレスを印加した場合、その特性が大きく劣化するという問題を有しており、その対策が望まれていた。

【解決手段】 500℃以下の温度で保持されたシリコン基板に対し、酸素ラジカルを用いてシリコン表面を酸化し、シリコン酸化膜を形成する半導体ゲート絶縁膜の形成方法において、ラジカル酸化を行う前に、シリコン基板表面を終端している水素原子を1x1014原子/cm2以下の面密度にまで除去することを特徴とする。

(もっと読む)

酸化ゲルマニウムの製造方法およびそれを用いた半導体デバイスの製造方法

【課題】熱的および化学的に安定な酸化ゲルマニウムの製造方法を提供する。

【解決手段】p型Geからなる基板1は、純水および0.1%HFによって洗浄され、その後、超純水によってリンスされる(工程(a)参照)。その後、基板1は、33%の過酸化水素水3に、60秒間、浸漬される(工程(b)参照)。これによって、酸化ゲルマニウム膜4が基板1の一主面に形成される。

(もっと読む)

半導体装置の製造方法

【課題】安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上にGaN系半導体層を形成する工程と、ALD装置内で、ゲート絶縁膜の成長温度に比べ高い温度で熱処理を実施し、前記GaN系半導体層の表面のフッ素を除去する工程S20と、前記フッ素を除去する工程S20の後、前記ALD装置内で、前記GaN系半導体層の表面に前記ゲート絶縁膜を形成する工程S16と、前記ゲート絶縁膜上にゲート電極を形成する工程と、を含む。

(もっと読む)

非シリコンチャネルMOSデバイス中のフェルミレベルピンニングの低減方法

【課題】金属酸化物半導体(MOS)デバイス中の、GeやIII−V化合物(例えばGaAsまたはInGaAs)のような高移動度半導体化合物チャネル中の、フェルミレベルピンニング(FLP)を低減(回避)する方法の提供。

【解決手段】半導体化合物11上のゲート誘電体19上にゲート電極20を形成し、水素アニール21を実施する。水素はゲート電極のPtやPdのような貴金属による触媒作用により原子状水素を形成しアニールを行い半導体化合物11とゲート誘電体19との界面を界面をパッシベートし、更には欠陥を回復する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】SiO2/SiC構造を備える、たとえばMOSFETなどの半導体装置は、界面準位密度の低減が不十分である。

【解決手段】SiC基板1の一方の主表面上に形成させたSiCエピタキシャル層2の一方の主表面上に、あらかじめSi薄膜3を形成させて、このSi薄膜3の内部に窒素原子を注入させる。この状態で、SiCエピタキシャル層2の一方の主表面上を酸窒化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、良好な移動度を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 第一の発明の半導体装置は、基板と、基板表面に形成され、Geを主成分とする半導体領域と、半導体領域上に形成された非金属Ge化合物層と、非金属Ge化合物層上に形成された絶縁膜と、絶縁膜上に形成された電極と、前記電極を挟む前記基板表面に形成されたソース・ドレイン領域とを備えることを特徴とする。非金属Ge化合物層は、例えばSrとGeの化合物、BaとGeの化合物もしくはBaとSiとGeの化合物を有する。

(もっと読む)

半導体装置の製造方法

【課題】活性領域表面に凹凸を生じることなく活性領域上端の角部を丸めることができる半導体装置の製造方法を提供する。

【解決手段】活性領域を画定する素子分離絶縁膜を形成する工程と、活性領域上に、0.1nm以上、0.7nm未満の膜厚の自然酸化膜を形成する工程と、水素を含む雰囲気中で、850℃よりも高く950℃未満の温度で熱処理を行い、活性領域の角部を丸めるとともに、自然酸化膜を還元除去する工程と、自然酸化膜を除去した活性領域上に、ゲート絶縁膜を形成する工程とを有する。

(もっと読む)

半導体素子およびその製造方法

【課題】本発明はトレンチの上部縁部位でゲート絶縁膜が薄くなる現象を防止し、均一な厚さを有するゲート絶縁膜を形成することができる半導体素子、およびその製造方法を提供する。

【解決手段】本発明の半導体素子は、活性領域を画定するトレンチが形成された基板と、該トレンチに埋め込まれた素子分離膜と、前記活性領域上にゲート絶縁膜の成長時に前記トレンチの上部縁部位での酸化を促進するために前記トレンチの上部縁部位に形成された酸化促進領域と、ゲート絶縁膜上に形成されたゲート導電膜と、を備える。

(もっと読む)

半導体基板、半導体装置およびその製造方法

【課題】 (111)表面のシリコン(Si)基板に、原子レベルで超平坦な表面を実現する。

【解決手段】 シリコン基板(111)表面を、予め、フッ化アンモニウム(NH4F)溶液で表面処理した後、濃度68%,沸点120.7℃の共沸硝酸溶液内に浸漬して、前記シリコン基板表面に二酸化シリコン(SiO2)主体の被膜を形成し、ついで、濃度40重量%のフッ化アンモニウム(NH4F)溶液で上記二酸化シリコン(SiO2)主体の被膜をエッチング除去する。AFM像では、バイレイヤー ステップが観測され、表面粗さの指標(RMSラフネス値)が0.07nmと判定され、原子レベルでの超平坦な表面が形成できた。

(もっと読む)

半導体装置の製造方法

【課題】Geを含有する半導体基板に効果的な洗浄方法が適用された半導体装置の製造方法を提供する。

【解決手段】Geを含有する半導体基板を、HClガス、HBrガスまたはHIガスの少なくとも一種を含むハロゲン化ガスで洗浄処理を行うことを特徴とする半導体装置の製造方法。Geを含有する半導体基板を、75℃以上110℃以下のHCl溶液で洗浄処理を行うことを特徴とする半導体装置の製造方法。例えば、MISFETのゲート絶縁膜の前処理、ソース・ドレイン電極形成の前処理、コンタクトの金属プラグ形成の前処理に適用される。

(もっと読む)

絶縁膜の形成方法および半導体装置の製造方法

【課題】炭素の混入と、組成のばらつきを低減した絶縁膜を形成する。

【解決手段】絶縁膜の形成方法において、基板上にシリコン層と金属層を順次形成してシリコンと金属の2層構造を形成し、前記シリコンと前記金属とが目標とする組成で金属珪化物を生成する反応温度を選択し、前記2層構造を加熱して金属珪化物層を形成する。前記金属のうち、未反応で残る部分を除去する。前記金属珪化物層を酸化又は窒化して、絶縁膜を形成する。

(もっと読む)

絶縁膜の形成方法及び絶縁膜

【課題】本発明の課題は、絶縁性が良好で、かつ酸化膜換算膜厚のきわめて薄い絶縁膜を提供することである。

【解決手段】水素終端による撥水性を持つシリコン表面から水素原子を脱離させ、親水化したのち、絶縁膜を堆積する工程を含む絶縁膜の形成方法である。

(もっと読む)

半導体装置の製造方法

【課題】 熱処理を行う際に、半導体基板の裏面側からの半導体構成原子の昇華を防止し得る半導体装置の製造方法及び半導体製造工程の管理方法を提供する。

【解決手段】 半導体基板10にゲート絶縁膜を形成する工程を有する半導体装置の製造方法であって、ゲート絶縁膜を形成する工程の前に、半導体基板の表面側及び裏面側を覆うように絶縁膜12を形成する工程と、半導体基板の表面側の絶縁膜をエッチング除去する工程と、半導体基板の裏面側に絶縁膜が存在している状態で、半導体基板を熱処理する工程とを有している。

(もっと読む)

基板、エピタキシャル層付基板および半導体装置

【課題】特性の向上を図ることが可能な基板、エピタキシャル層付基板および半導体装置を提供する。

【解決手段】半導体装置1は、{0001}面の<1−100>方向におけるオフ角度θが0°超え8°以下の六方晶系SiC基板としての基板2と、基板2の表面に形成されたSiCエピタキシャル成長層としての耐圧保持層22およびp領域23と、耐圧保持層22およびp領域23の表面に形成された絶縁膜としての酸化膜26と、酸化膜26の下の領域(p領域23の上層)と酸化膜26との界面(MOS界面)に流れる電子を供給するため、上記領域と隣接する位置に形成された導電領域としてのn+領域24とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域として用いるエピタキシャル成長結晶からゲート絶縁膜への不純物拡散による信頼性の低下を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、第1の面と、前記第1の面に対して傾斜した第2の面とを有するSiGe結晶層を形成する工程と、前記SiGe結晶層上に非晶質Si膜を形成する工程と、加熱処理を施すことにより、前記SiGe結晶層の前記第1および第2の面をシードとして、前記非晶質Si膜の前記第1および第2の面の近傍に位置する部分を結晶化させてSi結晶層を形成する工程と、前記非晶質Si膜の加熱処理により結晶化しなかった部分を選択的に除去、または薄くする工程と、前記Si結晶層の表面に酸化処理を施すことにより、前記Si結晶層の表面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、を含む。

(もっと読む)

半導体デバイスの製造方法

【課題】基板とhigh−k誘電体との界面の品質を最適化する技術を提供する。

【解決手段】high−kゲート誘電体を形成する方法であって、半導体基板を準備する工程と、基板を洗浄する工程と、熱処理を行う工程と、high−k誘電体材料を堆積する工程とを含み、熱処理工程は非酸化雰囲気中で行われて、半導体基板とhigh−k誘電体材料との間に薄い界面層を形成し、薄い界面層の膜厚は10Åより小さい方法。

(もっと読む)

半導体装置の製造方法

【課題】 自然酸化膜を還元除去できる低温化可能な工程を有する半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、(a)少なくともシリコン表面層を有する基板を準備する工程と、(b)前記シリコン層の表面に厚さ0.1nm〜0.5nmの自然酸化膜を形成する工程と、(c)前記厚さ0.1nm〜0.5nmの自然酸化膜を水素アニール処理により、還元除去する工程と、(d)前記工程(c)に続いて、前記シリコン表面層の表面にゲート絶縁膜を形成する工程と、を有する。

(もっと読む)

21 - 40 / 117

[ Back to top ]