Fターム[5F140BE01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜の製造 (6,009) | ゲート絶縁膜を形成前の処理 (668)

Fターム[5F140BE01]の下位に属するFターム

Fターム[5F140BE01]に分類される特許

101 - 117 / 117

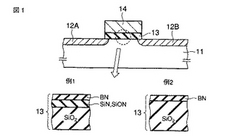

半導体装置及びその製造方法

【課題】不純物の突き抜けや拡散を防止できる高性能な絶縁膜を提案する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板11と、半導体基板11上に形成されるPチャネルMOSトランジスタのゲート絶縁膜13とを備える。ゲート絶縁膜13は、酸化膜(SiO2)と、少なくともボロン原子と窒素原子を含む拡散防止膜(BN)とから構成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】熱酸化膜と半導体基板の界面で生じる応力を抑制することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板1に溝1aを形成する工程と、溝1aの内面に位置する半導体基板1に、フッ素を導入してフッ素含有層1bを形成する工程と、溝1aの側壁及び底面に、熱酸化膜2aを形成する工程と、溝1aに絶縁膜2を埋め込む工程とを具備する。熱酸化膜2aは、フッ素を含んでいるため、イオン結合性が高くなり、従来と比べて柔軟性が増す。このため、熱酸化膜と半導体基板の界面において、応力の発生が抑制される。

(もっと読む)

半導体装置の製造方法

【課題】 トレンチ内の底部およびその近傍の側壁面に簡易に厚い酸化膜を形成できる半導体装置の製造方法を提供する。

【解決手段】 トレンチ11内に均一に厚いシリコン酸化膜3を形成させた後、Arなどのイオンを斜めイオン注入によるシャドーイングを利用してトレンチ側壁のシリコン酸化膜に選択的に注入ダメージ領域31を導入する。シリコン酸化膜3の湿式エッチング時において、イオン注入時にシャドーイングされたダメージ未導入部分よりもダメージ導入部分でエッチングレートが増大する現象を利用して、トレンチ11内の注入ダメージ領域31のシリコン酸化膜を選択的に除去し、トレンチ底部およびトレンチ底部に近いトレンチ側壁の部分的領域に残留酸化膜33を形成する。これにより、バーズビークが発生することなしに、トレンチ側壁下部と底部に相対的に厚い酸化膜を形成した半導体装置が作成できる。

(もっと読む)

半導体装置およびその製造方法

【課題】高い誘電率を有し、かつシリコン基板との界面が安定なゲート絶縁膜を備えた半導体装置およびその製造方法を提供することを目的としている。

【解決手段】半導体装置は、シリコン基板11の主表面上に設けられたアモルファスマトリックス層22と前記アモルファスマトリックス層中に散在された高誘電率の結晶体21とを備えたパイロセラミクスにより形成されたゲート絶縁膜13と、前記ゲート絶縁膜上に設けられたゲート電極14とを具備している。

(もっと読む)

半導体装置およびその製造方法

【課題】 p型チャネルを有する半導体装置において、前記p型チャネル領域に一軸性圧縮応力をSiGe混晶層より印加して、前記チャネル領域におけるホール移動度を向上させる。

【解決手段】 シリコン基板中、ソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層によりエピタキシャルに充填する際に、前記トレンチの側壁面を複数のファセットにより画成し、さらにSiGe混晶層中のGe原子濃度を20%を超えて増大させる。

(もっと読む)

CMOS半導体装置

【課題】 N型MOSFETおよびP型MOSFETを備える半導体装置において、N型MOSFETのリーク電流を抑制しつつ、P型MOSFETの性能を最大限に発揮させる。

【解決手段】 同一の電源電圧で動作する領域内にN型MOSFET118とP型MOSFET120とを形成する際に、N型MOSFET118のゲート絶縁膜106aの厚さをP型MOSFET120のゲート絶縁膜106bの厚さよりも厚くする。

(もっと読む)

半導体装置とその製造方法

【課題】 酸素イオン注入工程とアニール工程を半導体装置の製造方法に応用し

、半導体装置のコストパフォーマンスを著しく向上させた半導体装置とその製造

方法の提供。

【解決手段】 ゲート酸化膜厚の異なる複数のMOSFETおよび素子分離領域を酸素

インプラを用いた新しい製造方法で構築し、パフォーマンスに優れた半導体集積

回路装置を構成する。

(もっと読む)

半導体装置の製造方法

【課題】 特性の良好なトレンチゲート型トランジスタを有する半導体装置の製造方法を提供する。

【解決手段】 P型シリコン基板101上にシリコン窒化膜103を形成し、シリコン窒化膜103に所定のパターンの開口を形成し、シリコン窒化膜108をマスクとして用いて半導体基板101にゲートトレンチ104を形成した後、ゲートトレンチ104の内部および開口内にポリシリコン膜106を埋め込むことにより、ゲート電極を自己整合的に形成する。さらに、シリコン窒化膜103の全面にコバルトなどの高融点金属107をスパッタ法により堆積させた後、アニール処理を行い、さらに余剰金属を除去することにより、ポリシリコン膜106の表面にこれらの金属のシリサイド108を形成する。

(もっと読む)

サドル型MOS素子

本発明はサドル(Saddle)構造を持つナノ大きさのMOS素子に関し、特にチャネルとゲート構造がサドル形に形成され、MOS素子の縮小化特性と性能を改善することができる新しい構造の高集積/高性能MOS素子に関する。

本発明によるMOS素子の主要特徴はチャネル領域がリセスされ、かつリセスされたチャネルの表面及び側面にゲート絶縁膜とゲート電極が形成され、上記ゲート電極はリセスされたチャネルと自己整合するように形成されていることである。すなわち、開示されたMOS素子では、リセスされたチャネル周辺の絶縁膜の一部を選択的に除去してリセスされたチャネルの表面及び側面を露出する。

本発明によれば、素子の縮小化特性がすぐれており、リセスされたチャネルの表面及び側面に電流が流れるチャネルが形成されるから、電流駆動能力が大幅に増大する。ゲート電極のチャネルに対する制御能力も向上し、従って、素子の特性を改善することができる。  (もっと読む)

(もっと読む)

絶縁膜の形成方法および炭化珪素半導体装置

【課題】 SiC結晶中における結晶欠陥の増加を抑制しつつ、SiC結晶上への絶縁膜形成速度を改善した絶縁膜形成方法と、この方法を用いて形成された絶縁膜を含むSiC半導体装置を提供する。

【解決手段】 SiC結晶1上への絶縁膜の形成方法であって、SiC結晶1上にSi膜2を形成する工程と、Si膜2を酸化または窒化することによりSiを含む絶縁膜を形成する工程と、を含む絶縁膜の形成方法である。また、この絶縁膜形成方法を用いた炭化珪素半導体装置の製造方法である。

(もっと読む)

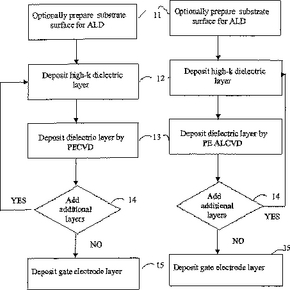

誘電体スタックの形成方法

本発明は、集積回路の中に誘電体スタックを形成する方法を提供し、(i)半導体基板上に高−k誘電体層を形成するステップと、(ii)高−k誘電体層を有する半導体基板を、プラズマ化学気相成長方法(PECVD)またはプラズマ原子層化学気相成長法(PEALCVD)において、窒素含有気相反応物およびケイ素含有気相反応物で処理するステップとを含む。さらに、本発明は、(i)少なくとも高―k材料を含む高―k誘電体層と、(ii)少なくともケイ素および窒素を含む誘電体層と、(iii)前記高―k誘電体層と前記誘電体層の間に配設された中間層とを含む集積回路中の誘電体スタックを提供し、前記中間層は前記高―k材料、ケイ素および窒素を含む。  (もっと読む)

(もっと読む)

半導体素子の製造方法

【課題】エピタキシャル成長法により半導体層を形成する際の加工寸法誤差を少なくすることができる半導体素子の製造方法を提供する。

【解決手段】有機金属化合物を含有する感光性ペーストを塗布した後ベークして、基板1上に感光性マスク層を形成する。この感光性マスク層をフォトリソグラフィによりパターニングし、更に酸化処理又は還元処理して、基板1上に金属酸化物を主成分とするエピタキシャルマスク4を形成する。そして、基板1表面のエピタキシャルマスク4が形成されていない領域上にダイヤモンドをエピタキシャル成長させて、半導体ダイヤモンド層5a及び5bを形成する。エピタキシャルマスク4を除去した後、半導体ダイヤモンド層5a及び5b上に夫々ソース電極7及びドレイン電極8を形成すると共に、基板1表面におけるチャネル領域上にゲート絶縁膜6を介してゲート電極9を形成する。

(もっと読む)

平滑基板上への高K誘電体層の形成

平坦シリコン基板上に、バッファ層と高K金属酸化物誘電体が形成される。基板の平坦度は、高K金属酸化物ゲート誘電体が柱状成長することにより低下する。基板表面は、成膜の前に、水酸基終端で飽和化される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 微細化が進められてもトランジスタのオン電流を十分に確保することができる半導体装置及びその製造方法を提供する。

【解決手段】 全面に高電圧トランジスタ用のゲート絶縁膜4を形成した後、低電圧領域内に存在するゲート絶縁膜4を除去する際に、活性領域3が露出した時点でエッチングを終了するのではなく、低電圧領域内において、活性領域3の表面よりも素子分離絶縁膜2の表面が、例えば15nm程度低くなるまでオーバーエッチングを行う。次に、低電圧領域内の活性領域3に対して高温急速水素加熱処理を行う。この結果、低電圧領域内の活性領域3の表面から自然酸化膜が除去され、平坦度が増すと共に、角部が丸まる。

(もっと読む)

高誘電率誘電体材料の安定化

本発明の実施形態は、基板を、一連の堆積プロセス、窒化プロセス及びアニールプロセスに曝して誘電体スタックを形成する方法を提供する。一実施形態において、方法は、基板を堆積プロセスに曝して前記基板上に誘電体層を形成し、前記基板を窒化プロセスに曝してその上に窒化物層を形成し、前記基板をアニールプロセスに曝し、中間に周期的に前記基板をアニールプロセスに曝しながら前記基板を連続して堆積プロセス及び窒化プロセスに曝して所定の厚さを有する誘電体材料を形成することを含む。一般的に、窒化プロセス中に窒素プラズマが使用され、約5at%〜約25at%の範囲内の窒素濃度を形成する。誘電体層は、通常、酸素及びハフニウム、タンタル、チタニウム、アルミニウム、ジルコニウム、ランタン、シリコン又はその組み合わせなどの少なくとも一種の付加元素を含有する。 (もっと読む)

ドープされたゲート誘電体を有するトランジスタ

トランジスタおよびその製造方法。ゲート誘電体材料を堆積する前に半導体基材をドープする。別個のアニール工程、または、トランジスタを製造するために使用される後続のアニール工程の間を用いて、ドーパント種を、基材のドープされた領域から、ゲート誘電体内に出力拡散して、ドープされたゲート誘電体を生成する。ドーパント種は、ゲート誘電体の原子構造における各空孔を埋め、その結果、トランジスタの動作速度が上昇し、電力消費が低減され、電圧安定性が改善される。  (もっと読む)

(もっと読む)

電気試験データに基づいてゲート絶縁層の特性および特徴を制御するための方法、これを実施するためのシステム

本発明は、一般に、電気試験データ(46)に基づいてゲート絶縁層(16)の特性および特徴を制御する各種方法、ならびにこれを実施するためのシステムを対象としている。例示的な一実施形態では、上記方法は、少なくとも1つの半導体デバイスに少なくとも1つの電気試験を実施するステップと、以降形成する半導体デバイスに少なくとも1つのゲート絶縁層(16)を形成するために実施する少なくとも1つのプロセス操作の少なくとも1つのパラメータを、電気試験から得られた電気データに基づいて決定するステップと、決定されたパラメータを含む少なくとも1つのプロセス操作を実施して、ゲート絶縁層(16)を形成するステップとを有する。  (もっと読む)

(もっと読む)

101 - 117 / 117

[ Back to top ]