Fターム[5F140BF03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467)

Fターム[5F140BF03]の下位に属するFターム

Fターム[5F140BF03]に分類される特許

181 - 192 / 192

半導体装置及びその製造方法

【課題】短チャネル効果を抑制できる構造であり、しきい値電圧を制御でき、電流駆動力に優れ、高速動作が可能なマルチフィンFETを有する半導体装置及びその製造方法を提供することである。

【解決手段】上記の課題を解決した半導体装置の1態様は、半導体基板上に設けられたソース領域及びドレイン領域と、前記ソース領域及びドレイン領域を接続する複数のフィンと、前記半導体基板の上方に設けられ、前記各フィンの一方の側面側に設けられた第1のゲート電極と、前記半導体基板の上方に設けられ、前記フィンに対して前記第1のゲート電極と対向して前記各フィンの他方の側面側に設けられ、前記第1のゲート電極と分離された第2のゲート電極と、前記各々の第1のゲート電極に接続する複数の第1のパッド電極と、前記複数の第1のパッド電極を接続する第1の配線と、前記各々の第2のゲート電極に接続する複数の第2のパッド電極と、前記複数の第2のパッド電極を接続する第2の配線とを具備する。

(もっと読む)

High−k層内に形態を形成する方法及びシステム

【課題】High−k層内に形態を形成する方法及びシステムを提供することである。

【解決手段】high−k層をプラズマ処理する方法は、high−k層が上に形成されている基板を、処理チャンバ内の基板ホルダ上に提供することと、この処理チャンバ内にプラズマを生成し、それによって、このhigh−k層をこのプラズマにさらすこととを含む。高周波電力がこの基板ホルダに印加され、この高周波電力は、この基板とこのhigh−k層との間に配設されている酸化物界面層の形成の割合を低減する特性を有する。デバイスは、high−k層内でエッチングされた形態を含む。このデバイスのエッチングプロファイルは、低減されたバーズビークを含むことができ、また、エッチングされた領域内におけるこの基板の表面は、エッチングされていない領域の下の基板と実質的に同一平面にすることができる。

(もっと読む)

半導体装置の製造方法、電極膜、MOSトランジスタ、及び半導体装置

【課題】

容易に膜厚が制御され、かつ結晶性が良好であり、低抵抗率や良好なエッチング選択性等といった、良好な特性を示すシリサイド膜およびその作製手段を提供する。

【解決手段】

本発明では、半導体基板上に電極膜を成膜する時、基板温度を400℃から900℃まで加熱しながら、成膜速度を極めて遅くして(1〜1000Å/min)堆積させる。また、電極膜を成膜する前に、ArイオンやGeイオンやXeイオンによって表面を非晶質化するためのイオン注入をおこなってもよい。また、電極膜を成膜中にSiが電極膜中に拡散するための時間およびシリサイド化反応が進む時間が、成膜時間だけでは足らない場合は、数原子層成膜した後、Siが拡散してシリサイド化反応が進むまで成膜を止めて、適切な時間が経過した後、再び電極膜を成膜する、多段階成膜法をおこなっても良い。

(もっと読む)

半導体装置の製造方法

【課題】 従来技術による金属ゲート電極形成ではシリコン基板が大口径化した場合、ウェハ面内、及び疎密間での寸法及び形状のばらつきが大きくなるという課題があった。

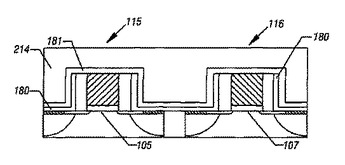

【解決手段】 本発明は、タングステンゲートエッチングにおいて、寸法のウェハ面内均一性に優れた電極形成可能とした半導体装置の製法であって、具体的には、シリコン基板101にゲート絶縁膜としてシリコン酸化膜102、高誘電体膜(High−k膜)103、ゲート電極材料としてタングステン膜104、マスク膜としてシリコン窒化膜105を順に成膜する。反射防止膜106を塗布し公知のリソグラフィ技術によりパターンを形成し、この基板を反射防止膜106、シリコン窒化膜105を一般的な条件でエッチングした後、タングステン膜をシリコン基板の中央と外周のプラズマ密度の比を3〜4:1の条件で残膜が3〜5nmになるまでエッチングを行い、最後に残りのタングステン膜をプラズマ密度の比が中央:外周=1:1の条件でエッチングを行うこと方法である。

(もっと読む)

MIS型FETの製造方法

【課題】 ダマシン構造のゲート電極を備えたMIS型FETにおいて、高い電流駆動能力と低消費電力とを有するMIS型FETの製造方法を提供する。

【解決手段】 シリコン基板1の表面部にソース/ドレイン拡散層(14,15)を形成し、その表面にシリサイド層17を形成する。そして、ゲート側壁(12,13)で区画されたゲート開口溝20底部のシリコン基板1表面に、550℃以下の温度で界面層21を形成し、ゲート開口溝20内、界面層21および層間絶縁膜19を被覆するようにHigh−k膜22を堆積させ、酸化性雰囲気中550℃以下の温度での熱処理を施す。そして、全面を被覆する導電体膜23およびメタル膜24を形成した後、CMP法により層間絶縁膜19上の不要部分を研磨除去しダマシン構造のメタルゲート電極を備えたMIS型FETを形成する。

(もっと読む)

半導体装置及びかかる半導体装置の製造方法

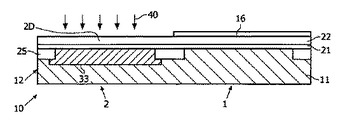

本発明は、金属及び更なる元素の両方を含有する化合物を含むゲート領域(1D、2D)を有するNMOST1及びPMOST2を備えるCMOSデバイス(10)に関する。本発明によれば、第1及び第2導電材料はいずれも、モリブデン及びタングステンを含むグループから選択される金属を前記金属として含む化合物を備えると共に、炭素、酸素、カルコゲナイドを含むグループから選択される元素を前記更なる元素として含んでいる。第1及び第2導電材料はいずれも、モリブデン及び炭素または酸素から成る化合物を含むことが好ましい。また本発明は、かかるデバイスを製造する魅力的な方法も提供する。  (もっと読む)

(もっと読む)

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

素子、集積回路及びそれらの製造方法

【課題】 従来の電子デバイスはデバイス構造を立体構造で形成、または、新規材料を導入した場合に於いても、微細化に限界があり、大規模集積回路の形成が困難になるという課題があった。

【解決手段】 ゲート電極4、ソース・ドレイン5を設けた単位素子9は、配線8の中心部に中空状態で支持されている。ここで注意したいことは、単位素子9と配線8、また、配線8と配線8は空隙10(真空状態の空隙が好ましい)で電気的に絶縁される。CNT用いたメリットの一つとして、電気的な伝導方向の異方性があり、円筒状形状に対して水平方向には高い導電性があるものの、円筒状形状の垂直方向には導電性がほとんどない。このような性質を利用して電気的絶縁を可能にし、3次元ネットワーク構造を構築している。

(もっと読む)

半導体装置およびその製造方法

【課題】 閾値の変動を回避するとともに、電気的ストレスに対する信頼性の高いMOSトランジスタを備えた半導体装置を提供する。

【解決手段】 素子領域を画定する素子分離領域(12)が設けられた半導体基板(11)と、前記半導体基板の前記素子領域に離間して設けられたソース/ドレイン領域(25)と、前記半導体基板の前記素子領域上に設けられたゲート絶縁膜(13,14)と、前記ゲート絶縁膜上に設けられ、半導体を含むゲート電極(15)とを具備する半導体装置である。前記ゲート絶縁膜は、金属および酸素を含有する第1の絶縁膜(13)と、この第1の絶縁膜上に形成され、シリコンおよび酸素を含有する第2の絶縁膜(14)とを含み、前記第2の絶縁膜は、前記ゲート電極との界面における前記金属の含有量が6.6atomic.%未満であることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能や信頼性を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aは、P、AsまたはSbをドープしたシリコン膜をNi膜と反応させることで形成されたニッケルシリサイド膜からなり、pチャネル型MISFET30bのゲート電極31bは、ノンドープのシリコンゲルマニウム膜をNi膜と反応させることで形成されたニッケルシリコンゲルマニウム膜からなる。ゲート電極31aの仕事関数はP、AsまたはSbをドープすることによって制御され、ゲート電極31bの仕事関数はGe濃度を調節することによって制御される。

(もっと読む)

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

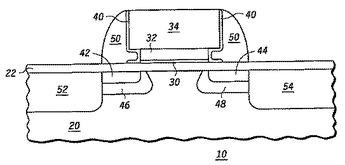

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

非対称の側壁スペーサの形成方法

集積回路半導体デバイスの製造プロセスに統合可能な非対称スペーサの形成方法が提供される。この方法は、基板上にゲート構造(15)を形成するステップと、ゲート構造および基板の上に側壁層(10)を形成するステップとを含み、側壁層は、ゲート構造の第1の側壁の上に第1の部分を含む。第1の部分に隣接して、フォトレジスト構造(11)が形成され、イオンビームにさらされる。フォトレジスト構造は、第1の部分の少なくとも一部をイオンビームから遮蔽するように働く。照射中、ウェハは、イオンビーム(13、17)の経路と、第1の側壁の表面との間に、非直交傾斜角が存在するように配向される。遮蔽されていない側壁部分への放射ダメージにより、その後に続くエッチングがより高速に進むため、非対称スペーサの形成が可能である。  (もっと読む)

(もっと読む)

181 - 192 / 192

[ Back to top ]