Fターム[5F140BF03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467)

Fターム[5F140BF03]の下位に属するFターム

Fターム[5F140BF03]に分類される特許

41 - 60 / 192

量子井戸型半導体装置

量子井戸型半導体装置、および量子井戸型半導体装置を形成する方法について示した。本方法は、基板の上部に配置され、量子井戸チャネル領域を有するヘテロ構造を提供するステップを有する。また、この方法は、ソースおよびドレイン材料領域を形成するステップを有する。また、この方法は、ソースおよびドレイン材料領域に溝を形成するステップを有し、ドレイン領域から分離されたソース領域が提供される。また、この方法は、溝内のソース領域とドレイン領域の間に、ゲート誘電体層を形成するステップと、溝内のゲート誘電体層の上部に、ゲート電極を形成するステップとを有する。  (もっと読む)

(もっと読む)

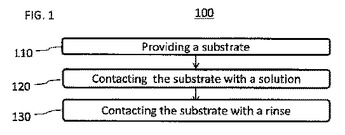

マスキング材料の除去

マスキング材料、例えば、フォトレジストを除去するための方法、およびマスキング材料を除去することによって形成される電子デバイスが示される。例えば、マスキング材料を除去するための方法は、マスキング材料を、セリウムおよび少なくとも1つの追加的な酸化剤を含む溶液と接触させる工程を含む。セリウムは塩に含まれてもよい。塩は硝酸セリウムアンモニウムであってもよい。少なくとも1つの追加的な酸化剤は、マンガン、ルテニウムおよび/またはオスミウム含有化合物であってもよい。  (もっと読む)

(もっと読む)

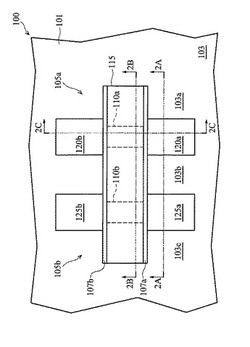

FINFETSおよびその形成方法

【課題】フィン電界効果トランジスタのソース/ドレイン構造を提供する。

【解決手段】基板上のフィンチャネル本体110a、110b、フィンチャネル本体110a、110b、上に配置されたゲート電極115、およびフィンチャネル本体110a、110b、に隣接して配置され、どのフィン構造も実質的に含まない、少なくとも1つのソース/ドレイン(S/D)領域120a,120b及び125a,125bを含むフィン電界効果トランジスタ(FinFET)。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電体ゲート絶縁膜およびシリコン基板との界面を高品質化して、MISFETの特性向上を図る。

【解決手段】 シリコン基板11上にhigh−k膜21とゲート電極24を形成する半導体装置の製造方法において、high−k膜形成後にフッ素雰囲気でアニール処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を有するMISFETを備えた半導体装置の信頼性向上を図る。

【解決手段】nチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとLaとOとを主成分として含有するHf含有絶縁膜4aを形成し、pチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとAlとOとを主成分として含有するHf含有絶縁膜4bを形成する。それから、金属膜7とシリコン膜8を形成し、これらをドライエッチングでパターニングしてゲート電極GE1,GE2を形成する。その後、ゲート電極GE1,GE2で覆われない部分のHf含有絶縁膜4a,4bをウェットエッチングで除去するが、この際、フッ酸を含有しない酸性溶液でのウェット処理とアルカリ性溶液でのウェット処理とを行ってから、フッ酸を含有する酸性溶液でのウェット処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】ナローチャネル特性の劣化を抑制する。

【解決手段】素子分離領域STIは、半導体基板100に形成されたトレンチ104内に設けられており、トレンチ104の側壁上に形成された下地絶縁膜105を有している。素子形成領域100a上にはゲート絶縁膜112が形成されており、ゲート絶縁膜112は高誘電率膜110を有している。高誘電率膜110の第1の部分110aは、素子形成領域100aにおける上面上に形成されており、高誘電率膜110の第2の部分110bは、素子形成領域における上部側面104a上に下地絶縁膜105を介して形成されている。第2の部分110bと下地絶縁膜105との間には、MISトランジスタの閾値電圧を変更する金属を含有する第1のキャップ膜106が設けられている。

(もっと読む)

金属ゲートとストレッサーを有するゲルマニウムフィンFET

【課題】金属ゲートとストレッサーを有するゲルマニウムフィンFETを提供する。

【解決手段】集積回路構造は、n型フィン電界効果トランジスタ(fin field effect transistor、FinFET)とp型FinFETからなる。n型FinFETは、基板上の第一ゲルマニウムフィン、第一ゲルマニウムフィンの上面と側壁上の第一ゲート誘電体、及び、第一ゲート誘電体上の第一ゲート電極からなる。p型FinFETは、基板上の第二ゲルマニウムフィン、第二ゲルマニウムフィンの上面と側壁上の第二ゲート誘電体、及び、第二ゲート誘電体上の第二ゲート電極からなる。第一ゲート電極と第二ゲート電極は、ゲルマニウムの固有エネルギーレベルに近い仕事関数を有する同一材料で形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート構造としてメタル電極/High−k膜構造を用いた半導体装置において、仕事関数の制御とEOTの薄膜化とを両立させる。

【解決手段】半導体基板101におけるnチャネルMISトランジスタ形成領域の上に、ゲート絶縁膜として、第1の高誘電率絶縁層202、アルミニウム含有層203、ランタン含有層204及び第2の高誘電率絶縁層205を順次形成する。その後、ゲート電極形成を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、pチャネルトランジスタのチャネル領域には圧縮歪を、nチャネルトランジスタのチャネル領域には引っ張り歪をそれぞれ効果的に印加できる新しい歪技術を提供する。

【解決手段】pチャネルトランジスタ105のゲート電極は、引っ張り内部応力を持つpチャネルメタル電極110を有する。nチャネルトランジスタ106のゲート電極は、圧縮内部応力を持つnチャネルメタル電極116を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】高誘電率ゲート絶縁膜として機能するHf含有絶縁膜4a,4b上にメタルゲート電極であるゲート電極GE1,GE2が形成され、ゲート電極GE1,GE2は、金属膜7a,7b,7cの積層膜からなる金属膜7とその上のシリコン膜8との積層構造を有している。金属膜7の最下層の金属膜7aは、窒化チタン膜、窒化タンタル膜、窒化タングステン膜、炭化チタン膜、炭化タンタル膜または窒化タングステン膜からなり、金属膜7bは、ハフニウム膜、ジルコニウム膜またはアルミニウム膜からなり、金属膜7cは、金属膜7aと同種の材料からなる膜である。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域にエピタキシャル結晶を含み、エピタキシャル結晶上の金属シリサイドに起因する接合リークの発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、ファセット面13fを有するエピタキシャル結晶層13を有するMISFET10と、MISFET10を他の素子から電気的に分離し、上層3aのゲート電極12側の端部の水平方向の位置が下層3bのそれよりもゲート電極12に近く、上層3aの一部がファセット面13fに接する素子分離絶縁膜3と、エピタキシャル結晶層13の上面、およびファセット面13fの上層3aとの接触部よりも上側の領域に形成されたシリサイド層18と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、最適な仕事関数を有するメタルゲート電極を持つ半導体装置及びその製造方法に関する。

【解決手段】n チャネルMIS トランジスタを含む半導体装置であり、n チャネルMIS トランジスタは、基板上に形成されたp 型半導体領域、p 型半導体領域に形成されたソース領域102及びドレイン領域104、ソース領域102及びドレイン領域104間のp 型半導体領域上に形成されたゲート絶縁膜106、ゲート絶縁膜106上に形成された金属層108及び化合物層110からなる積層構造を持つゲート電極を有する。金属層108は2 nm未満の厚さ及び4.3 eV以下の仕事関数を有し、化合物層110は4.4 eVを越える仕事関数を有しかつAl及び金属層108とは異なる金属を含んでいる。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体装置の製造方法

【課題】より高温の活性化FLAを行ってもウェハが割れることなく、SDエクステンション抵抗を下げることができる半導体装置の製造方法を提供する。

【解決手段】ウェハをウェハ表面温度1100℃以上に0.1〜10ミリ秒で加熱するための高強度のフラッシュランプアニールを照射する際、その直前のウェハ表面温度を800〜1000℃と高温にする。ウェハの予備加熱を、波形を調整したフラッシュで行うことにより不純物の拡散を抑制する。この手法により、アモルファス層を形成していないウェハ表面を効果的に活性化できるため、欠陥が少なく、かつ浅く低抵抗な接合が形成できる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜として高誘電体膜を使用すると、半導体装置の微細化を図ることができるが、半導体装置の性能低下を招来する場合があった。

【解決手段】半導体装置では、半導体基板101の上面上に、界面酸化層102、ゲート絶縁膜104及びゲート電極107が順に設けられている。ゲート絶縁膜104は、第1の高誘電体膜103と第2の高誘電体膜105とを有している。第1の高誘電体膜103は、界面酸化層102の上に設けられ、窒素を含有している。第2の高誘電体膜105は、第1の高誘電体膜103の上に設けられ、窒素を含有している。第1の高誘電体膜103における窒素濃度は、第2の高誘電体膜105における窒素濃度よりも低い。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置の製造方法

【課題】不純物を活性化するときにミリ秒アニールを用いても、電圧ストレスに起因した閾値電圧のシフト量が大きくなることを抑制する。

【解決手段】半導体基板100上に、酸化シリコンより誘電率が高い高誘電率膜134を含むゲート絶縁膜130を形成する。ゲート絶縁膜130上に、金属膜を含むゲート電極140を形成する。半導体基板100に不純物を導入することにより、エクステンション領域170を形成する。エクステンション領域170に光を照射することにより、エクステンション領域170が1000℃以上となる時間を100ミリ秒以下にした第1の熱処理を行う。ついで、半導体基板100に700℃以上900℃以下の第2の熱処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート誘電体層108と、ゲート誘電体層108上に形成された酸素を含む合金層110と、酸素を含む合金層110上に形成されたRe層112と、ゲート誘電体層108と酸素を含む合金層110との間に位置するRe酸化物層502を含むp 型電界効果トランジスタを具備する。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのしきい値電圧制御のために使用する金属酸化膜の膜減り等に起因するしきい値電圧ばらつきを抑制し、所望のしきい値電圧を有するトランジスタを形成することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上に、高融点金属酸化物を含む材料からなるゲート絶縁膜3が形成され、ゲート絶縁膜3上に金属酸化膜4が形成される。次いで、金属酸化膜4を構成する金属原子を、金属酸化膜4からゲート絶縁膜3の表面部へ拡散させる処理が実施される。当該金属原子の拡散工程後、上記金属酸化膜4がゲート絶縁膜3に対して選択的に除去される。そして、金属原子が拡散されたゲート絶縁膜3上に導電膜7、8が形成され、当該導電膜7、8を加工することでゲート電極30、31が形成される。

(もっと読む)

41 - 60 / 192

[ Back to top ]