Fターム[5F140BF03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467)

Fターム[5F140BF03]の下位に属するFターム

Fターム[5F140BF03]に分類される特許

121 - 140 / 192

トランジスタ、集積回路および集積回路形成方法

【課題】トランジスタ、集積回路、および、集積回路形成方法を提供する。

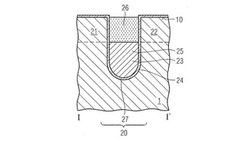

【解決手段】半導体基板1内に形成されたゲート溝27内にゲート誘電体24を介してゲート電極23が配置された構成を有する。該ゲート電極23は、導電性炭素材を有している。

(もっと読む)

半導体装置

【課題】ポリシリコン/メタル積層電極構造のポリシリコン/メタル界面における界面抵抗を低減し、動作速度の低下を防止する。

【解決手段】半導体基板100と、領域N1にチャネル領域102を挟むように形成された拡散層103と、ゲート絶縁膜104と、金属膜105a、105b及びn型ポリシリコン膜105cを含むゲート電極105と、を有するnチャネルMISFETと、領域P1にチャネル領域202を挟むように形成されボロンをドーパントして含む拡散層203と、ゲート絶縁膜204と、金属膜205a〜c及び窒素を含む金属膜205cとの界面部におけるボロン濃度が5E19cm−3以下であるn型ポリシリコン膜205dを含むゲート電極205と、を有するpチャネルMISFETと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化プロセスにおいても、また、Nchトランジスタ及びPchトランジスタの両方を持つデバイスにおいても、欠陥等を発生させることなく、トランジスタのチャネル領域に対する応力制御を行うことを可能にする。

【解決手段】Nchトランジスタの第1のゲート電極107及びPchトランジスタの第2のゲート電極108のそれぞれの構成材料として、互いに応力の大きさが異なる材料を用いている。

(もっと読む)

半導体装置

【課題】素子特性のばらつきが抑制されたMOS型素子を含む半導体装置を提供すること。

【解決手段】基板の半導体領域に埋め込まれた素子分離絶縁膜と、前記素子分離絶縁膜によって素子分離され、上部が前記素子分離絶縁膜の表面よりも上に突出し、前記半導体領域の半導体層と、この半導体層にソース・ドレイン領域、ゲート絶縁膜およびゲート電極が形成され、かつ、前記ゲート電極がチャネル幅方向に平行な面の断面において前記素子分離絶縁膜上に形成されてなるMOS型素子とを具備してなり、前記ゲート電極下の前記半導体層の上面位置が、前記ゲート電極下の前記素子分離絶縁膜の上面位置よりも、20nm以上高いことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】従来のCMISデバイスにおいては、価電子帯端近くの高い仕事関数を有する金属は、還元雰囲気アニール後に実効仕事関数が低下する。

【解決手段】半導体装置は、ソースとドレイン間のN型半導体層上に形成された金属元素を含むゲート絶縁膜と、ゲート絶縁膜上に形成され、膜厚が3nm以下であるカーボン層と、カーボン層上に形成されたゲート電極とを有し、ゲート電極/ゲート絶縁膜界面へのカーボン層による仕事関数の上昇効果により、還元雰囲気アニール耐性のない価電子帯端近くの高い仕事関数を有する金属を用いずとも、PMISFETに必要な実効仕事関数を得ることができ、低い閾値電圧を実現する。

(もっと読む)

二酸化窒素センサ

【課題】 固体電解質を用いたガスセンサは、検知電極と参照電極を必要とし、安定性に欠ける問題がある。また、補助相となるイオン導電体をゲート電極上に設けたFET型のガスセンサは、参照電極を用いないため小型化が可能であるが、NO2の選択性と応答速度に問題があった

【解決手段】 一導電型半導体層表面の一導電型の第1半導体領域の両側に、n型の第2半導体領域および第3半導体領域を設け、これらにそれぞれ接続する第2電極および第3電極を設ける。第1半導体領域とコンタクトする絶縁膜をp型半導体層上に設け、第1半導体領域に電圧を印加する第1電極を設ける。第1電極の一部を被覆し、第1半導体領域上の絶縁膜とコンタクトする補助相を設ける。補助相はイオン導電体(NaNO2)内に、貴金属(Ru)を担持した金属酸化物(WO3)を分散させてなり、これによりNO2の選択性、応答・回復特性が良好なNO2センサを得る。

(もっと読む)

自己整合エピタキシャルソース及びドレイン張り出し部を有する半導体デバイス

ゲート誘電層に近接する自己整合ソース及びドレイン張り出し部を有するトランジスタの作製方法は、基板上にゲート積層体を作製する工程、前記ゲート積層体に隣接する前記基板の領域へドーパントを注入する工程であって、前記ドーパントは前記基板のエッチング速度を増大させ、かつ前記ソース及びドレイン張り出し部の位置を画定する工程、前記基板のドーパントが注入された領域上に設けられた前記ゲート積層体の横方向で対向する面に一対のスペーサを形成する工程、前記基板のドーパントが注入された領域及び該領域の下に位置する前記基板の一部をエッチングする工程であって、前記ドーパントが注入された領域のエッチング速度は該領域の下に位置する前記基板の一部のエッチング速度よりも速い工程、並びに、前記の基板のエッチングされた部分中にシリコンベースの材料を堆積する工程、を有する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜に用いられるLa−Hf−O膜系は、成膜時にシリコン基板との間に低誘電率層が出現し、これ排除する公知な技術による半導体装置及びその製造方法は提案されていなかった。

【解決手段】本発明に従う実施形態は、非晶質状態でSiが添加されたLa−Hf−O膜をゲート絶縁膜として用いる半導体装置及びその製造方法である。

(もっと読む)

2つの仕事関数を備えたCMOSデバイスの製造方法

【課題】本発明は、2つの仕事関数の半導体デバイスの製造方法を提供する。

【解決手段】製造方法は、基板の第1領域及び第2領域上にデバイスを設けることを備える。これは、基板の第1領域及び第2領域上に誘電性層を設けること、及び第1及び第2領域の両方の誘電性層の上部にゲート電極を設けることによってなされる。第1領域上のゲート電極及び第2領域上のゲート電極の両方は仕事関数を有する。上記方法は、さらに、誘電性層とゲート電極との間で第1領域上にキャッピング層を設けることで第1領域上のゲート電極の仕事関数を変更し、及び第2領域における誘電性層とゲート電極との間の界面でスピーシーズを導入するようにスピーシーズを埋め込むことにより第2領域上のゲート電極の仕事関数を変更することを備える。

(もっと読む)

ディープサブミクロントランジスタ技術用のhigh−k/金属ゲートスタックをパッシベートするためのFベースのゲートエッチングの使用

【課題】プレーナ装置またはマルチゲート装置(MuGFET)のHfベースの誘電体ゲートスタックに、フッ素を導入し、負バイアス温度安定性および正バイアス温度安定性(NBTIおよびPBTI)を大幅に改良する、新規で、効果的で、費用対効果の高い方法を提供する。

【解決手段】新規な方法は、フッ素を導入するためにSF6ベースの金属エッチング化学反応を用い、これにより標準プロセスフローの熱量の後に、界面の優秀なHパッシベーションが得られる。この方法の優位点は、この方法がFを導入するための金属ゲートエッチングを用いて、追加の注入や処理が不要であることである。新たな方法を用いた大幅なBTIの改良に加えて、MuGFET装置において、より良いVthの制御性と増加した駆動電流を得ることができる。

(もっと読む)

電子デバイスおよびその製造プロセス

【課題】金属酸化物半導体電界効果トランジスタのような金属絶縁体デバイスおよび/または金属絶縁体金属キャパシタを提供する。

【解決手段】装置は、

炭化タンタル、炭窒化タンタル、炭化ハフニウム、および炭窒化ハフニウムからなる組から選択される金属化合物を含む電極と、

窒素とシリコンを含む酸化ハフニウムからなるhigh−k誘電体層であって、少なくとも4.0のk値を有するhigh−k誘電体層と、

電極とhigh−k誘電体層との間に配置された窒素および/またはシリコンおよび/または炭素のバリア層とを含み、

窒素および/またはシリコンおよび/または炭素のバリア層は、1またはそれ以上の金属酸化物を含み、金属酸化物の金属はランタニド、アルミニウム、およびハフニウムからなる組から選択される。

(もっと読む)

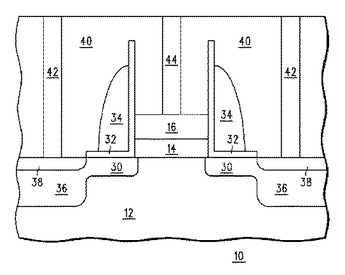

金属電極を有する半導体素子の形成、及び半導体素子の構造

半導体素子(10)を形成する方法は、ゲート誘電体(14)を基板(12)の上に形成する工程と、金属電極(16)をゲート誘電体(14)の上に形成する工程と、ポリシリコンまたは金属を含む第1犠牲層(18)を金属電極の上に形成する工程と、第1犠牲層(17)を除去する工程と、そしてゲート電極コンタクト(44)を金属電極(16)の上に位置し、かつ金属電極(16)に接続されるように形成する工程と、を含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜上にpMOS電極材料として金属電極を形成する際に金属膜中からゲート絶縁膜へ拡散する炭素成分を抑制し、固定電荷要因を下げることができる半導体装置及びその製造方法を提供することである。

【解決手段】半導体装置の製造方法は、半導体基板100上にゲート絶縁膜101を形成する工程と、ゲート絶縁膜上に薄いシリコン層102を形成する工程と、この薄いシリコン層上にゲート絶縁膜界面での仕事関数が所定範囲内の値となる金属膜103を形成する工程と、を備えたものである。

(もっと読む)

ナノチューブを利用した電界効果トランジスタ及びその製造方法

【課題】導電性ナノチューブをゲートとする製作が容易な高集積度のトランジスタ及びその製造方法を提供する。

【解決手段】本発明によるトランジスタは、ナノチューブをゲートとして利用し、製造方法は、ナノチューブをチャンネルパターン時にマスクとして利用する。これにより、50nm以下の線幅を有するトランジスタが得られる。

(もっと読む)

半導体素子への金属含有膜の集積方法

【課題】 本発明は、半導体プロセスに関する。より具体的には、本発明は、化学気相成長法によって形成される金属含有膜を半導体素子に集積する方法に関する。

【解決手段】 たとえばゲートスタックのような、半導体素子中の金属含有膜を集積する方法。一の実施例では、当該方法は、処理チャンバ内に基板を供する手順、その基板をタングステンカルボニル含有ガスに曝露することによって、その基板上に、第1基板温度でタングステン含有膜を成膜する手順、第1基板温度よりも高温である第2基板温度でタングステン含有膜を熱処理することで、そのタングステン含有膜から一酸化炭素を除去する手順、及びその熱処理されたタングステン含有膜上にバリヤ層を形成する手順、を有する。タングステン含有膜の例には、W、WN、WSi、及びWCが含まれる。他の実施例は、Ni、Mo、Co、Rh、Re、Cr又はRuを含む金属含有膜を、各金属元素に対応した金属カルボニル先駆体から堆積する手順を有する。

(もっと読む)

半導体装置、およびその製造方法

【課題】適切なトランジスタ閾値電圧を与えるメタルゲート電極を有し、比較的簡単な製造工程により製造することのできる半導体装置、およびこれを実現可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置は、シリコンを含む半導体基板と、前記半導体基板上に形成された比誘電率が8以上の高誘電材料からなる第1、および第2のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成されたジャーマナイドからなる第1のゲート電極と、前記第2のゲート絶縁膜上に形成されたシリサイドからなる第2のゲート電極と、を備える。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】金属ゲート電極のエッチング条件が、閾値電極を構成する材料が異なっても同一となる金属ゲート電極MOSFETを提供すること。

【解決手段】ゲート酸化膜に接して形成された第1の金属層と第1の金属層の上に形成された第1の低抵抗層とからなる第1のゲート電極を有するnチャネルMOSFETとゲート酸化膜に接して形成された第2の金属層と第2の金属層の上に形成された第2の低抵抗層とからなる第2のゲート電極を有するpチャネルMOSFETとを有する半導体集積回路において、第1の金属層と第2の金属層が異なった仕事関数を有する金属によって構成され、第1の低抵抗層と第2の低抵抗層とが同一の材料からなる多結晶で構成され、第1の金属層と第1の低抵抗層の間に第1の中間層を有し、且つ第2の金属層と第2の低抵抗層の間に第2の中間層を有し、第1の中間層および第2の中間層が組成、粒径、結晶構造、及び配向方向が同一の導電性多結晶膜からなる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】本発明は、PチャネルMOSFETのゲート電極に所定値以上の仕事関数を有するメタルを用いた場合であっても、適正なしきい値電圧を有する半導体装置及び当該半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、NチャネルMOSFET及びPチャネルMOSFETを含む半導体装置であって、前記PチャネルMOSFETのゲート電極は、第1の濃度の酸素を含有する第1の導電性膜110aと、前記第1の濃度より高い第2の濃度の酸素を含有する第2の導電性膜110bと、前記第2の濃度より低い第3の濃度の酸素を含有する第3の導電性膜110cと、を含む積層構造を有することを特徴とするものである。

(もっと読む)

誘電層に適合可能な活性領域

活性領域と、適合可能な誘電層を有する半導体構造を形成する方法を開示する。1つの実施形態においては、半導体構造は、第1の半導体材料の酸化物を含む誘電層を有しており、誘電層と第1の半導体材料との間に第2の(組成的に異なった)半導体材料が形成される。別の実施形態においては、第2の半導体材料の格子構造に一軸性ひずみを与える目的で、第2の半導体材料の一部は、第3の半導体材料に置き換えられる。 (もっと読む)

スピンMOSFET

【課題】低電流密度でスピン反転し、かつスピン反転による出力特性が大きなスピンMOSFETを提供することを可能にする。

【解決手段】半導体基板2と、半導体基板上に離間して設けられるソース・ドレインの一方となる磁化の向きが固着された第1強磁性層を含む第1磁性膜6と、ソース・ドレインの他方となる磁化の向きが可変の磁化自由層81およびこの磁化自由層上に設けられたトンネル絶縁層ならびにこのトンネル絶縁層上に設けられ磁化の向きが固着された磁化固着層を有する第2磁性膜8と、第1および第2磁性膜の間の半導体基板上に少なくとも設けられたゲート絶縁膜10と、ゲート絶縁膜上に形成されたゲート電極12と、備えている。

(もっと読む)

121 - 140 / 192

[ Back to top ]