Fターム[5F140BF03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467)

Fターム[5F140BF03]の下位に属するFターム

Fターム[5F140BF03]に分類される特許

101 - 120 / 192

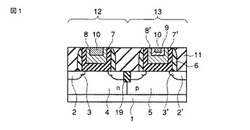

半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

(もっと読む)

選択的酸化プロセスの酸化物成長速度の改良方法

【課題】 半導体デバイスにおいてシリコン含有物質を選択的に酸化する方法の提供。

【解決手段】 一態様において、急速熱処理装置を用いて、水素を多く含む雰囲気中で高圧においてインサイチュで水蒸気を生成させることによって基板を選択的に酸化する。基板における金属やバリヤ層のような他の物質は酸化されない。

(もっと読む)

半導体装置の製造方法

【課題】ゲート長に依存する仕事関数の変動を抑えることができる半導体装置の製造方法を提供する。

【解決手段】ゲート絶縁膜14上の多結晶シリコン膜を露出した後、半導体基板11を400℃まで加熱し、その温度が安定した後に、その温度を保持したまま、例えばスパッタリング法によりニッケル膜21を全面に形成する。ニッケル膜21の厚さは、シリコン酸化膜20上で60nmとする。この結果、シリコン酸化膜20上にはニッケル膜21が形成されるが、多結晶シリコン膜の表面に到達してきたニッケルは、そこに堆積するのではなく、多結晶シリコン膜と反応し、多結晶シリコン膜の全体がニッケルシリサイド膜22に変化する。従って、pMOS領域1には、p型不純物を含有するニッケルシリサイド膜22からなるゲート電極が形成され、nMOS領域2には、n型不純物を含有するニッケルシリサイド膜22からなるゲート電極が形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 大幅なプロセスコスト増を伴うことなく、チャネルに歪を発生させることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板の一部の表面上に、半導体膜と、該半導体膜よりも密度の高いブロック膜とがこの順番に積層されたゲートパターンを形成する。(b)ゲートパターンをマスクとして、半導体基板の表層部に、ソース及びドレイン用の不純物を注入する。(c)ゲートパターンをマスクとして、半導体基板内に、ソース及びドレイン用の不純物とは異なる歪形成用の不純物を注入する。(d)半導体基板を熱処理し、歪形成用の不純物が注入された領域を再結晶化させる。

(もっと読む)

半導体装置及びその製造方法

【課題】それぞれが最適なゲート絶縁膜及びゲート電極を有するp型MISFET及びn型MISFETを備え且つ不良の原因となるポリシリコン膜残渣が発生することがない半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10の第1領域10Aの上に形成された第1のゲート絶縁膜13Aと、第1のゲート絶縁膜13Aの上に形成された第1のゲート電極14Aと、半導体基板10の第2領域10Bの上に形成された第2のゲート絶縁膜13Bと、第2のゲート絶縁膜13Bの上に形成された第2のゲート電極14Bとを備えている。第1のゲート絶縁膜13Aは、第1の金属を含む第1の材料からなる第1の絶縁膜を有し、第2のゲート絶縁膜13Bは、第1の材料と第2の金属を含む第2の材料とが混合された第2の絶縁膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動能力を低下させることなく、半導体装置内部の高電界が与える影響によって生じるGIDLを低減する。

【解決手段】ゲート電極108は、ゲート電極108のチャネル長方向の中央部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第1の導電部108Aと、ゲート電極108のチャネル長方向の両端部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第2の導電部108Bとを含む。第1の導電部108Aの第1の仕事関数と第2の導電部108Bの第2の仕事関数とが異なっている。

(もっと読む)

相補型半導体装置及びその製造方法

【課題】 メタルゲート電極及び高誘電率ゲート絶縁膜を用いたn型MISトランジスタとp型MISトランジスタの双方において適正なしきい値電圧を得る。

【解決手段】 半導体基板30の表面部に形成された第1及び第2の半導体領域10,20と、第1の半導体領域10上に形成された、La及びAlを含む第1のゲート絶縁膜11及び第1のゲート電極12を有するn型MISトランジスタと、第2の半導体領域20上に形成された、La及びAlを含む第2のゲート絶縁膜21及び第2のゲート電極22を有するp型MISトランジスタと、を備えた相補型半導体装置であって、第2のゲート絶縁膜22における原子濃度比Al/Laが、第1のゲート絶縁膜11における原子濃度比Al/Laよりも大きい。

(もっと読む)

MOSFETデバイスおよびその製造方法

【課題】フェルミレベルのピンニングの効果が、ポリシリコン(Poly−Si)/金属酸化物の界面で高い閾値電圧を招かないMOSFET(金属酸化物半導体電界効果トランジスタ)を含む半導体デバイスの製造方法を提供する。

【解決手段】半導体デバイスは、第1MOSFETトランジスタを含む。トランジスタは、基板、基板上の第1high−k誘電体層1、第1high−k誘電体層1上の第1誘電体キャップ層2、および第1誘電体キャップ層2上の、第1ドーピングレベルで第1導電型の半導体材料3からなる第1ゲート電極とを含む。第1誘電体キャップ層2は、スカンジウムを含む。

(もっと読む)

デュアル仕事関数半導体デバイスおよびその製造方法

【課題】CMOSを製造するにおいて、1つまたは2つの誘電体を有するデュアル金属ゲートを形成する場合の、本質的な製造プロセスの複雑さや費用が増加しない、製造が容易で信頼性のある、デュアル仕事関数を有する半導体デバイスの製造方法を提供する。

【解決手段】1つの金属電極から開始するデュアル仕事関数デバイスの簡単な製造方法およびそのデバイスを開示する。シングル金属シングル誘電体(SMSD)CMOS集積スキームが開示される。ゲート誘電体層1と誘電体キャップ層2および誘電体キャップ層2’’とを含む1つの誘電体スタックと、誘電体スタックを覆う1つの金属層とが、最初に形成され、金属−誘電体界面を形成する。誘電体スタックと金属層を形成した後、誘電体キャップ層2’’の、金属−誘電体界面に隣接する少なくとも一部が、仕事関数変調元素6を加えることにより選択的に変調される。

(もっと読む)

半導体デバイス、半導体デバイスを形成する方法、および集積回路

【課題】 相互に異なるしきい値電圧要件を有する複数のトランジスタを結合するための技法を提供する。

【解決手段】 一態様では、半導体デバイスは、第1および第2のnFET領域と第1および第2のpFET領域とを有する基板と、第1のnFET領域の上の基板上のロジックnFETと、第1のpFET領域の上の基板上のロジックpFETと、第2のnFET領域の上の基板上のSRAM nFETと、第2のpFET領域の上の基板上のSRAM pFETとを含み、そのそれぞれが、高K層の上の金属層を有するゲート・スタックを含む。ロジックnFETゲート・スタックは、高K層から金属層を分離するキャッピング層をさらに含み、キャッピング層は、ロジックpFET、SRAM nFET、およびSRAM pFETのうちの1つまたは複数のしきい値電圧に対してロジックnFETのしきい値電圧をシフトするようにさらに構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】移動度の低下を極力抑えつつゲートリーク電流が低い良好なゲート絶縁膜を有するMOSFETを含む半導体装置、及びその製造方法を提供する。

【解決手段】半導体層と、ゲート電極と、膜厚が1nm以上で少なくとも半導体層側からその厚み方向に1nmまでの領域は窒化酸化シリコン膜(SiON)から構成され、かつシリコンと酸素の原子数比(O/Si)が0.01〜0.30、シリコンと窒素の原子数比(N/Si)が0.05〜0.30であるゲート絶縁膜と、ソース/ドレイン領域と、を備えたMOSFETを有する半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、金属元素を有する絶縁膜の界面特性を向上させる半導体装置の製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、下層、Ge層、Ge酸化物層、上層の順に積層された構造を形成する工程と、熱処理を用いてGe酸化物層及びGe層を除去して、上層と下層とを直接接合させる工程とを有し、上層及び下層の何れかは金属元素を有する絶縁物で形成されることを特徴とする。

(もっと読む)

PチャネルMOSトランジスタ、NチャネルMOSトランジスタ及び不揮発性半導体記憶装置

【課題】高誘電率膜をゲート絶縁膜に用い、消費電力を低減したPMOSトランジスタを提供する。

【解決手段】半導体基板1と、半導体基板1の表面部にチャネル領域2を挟むように形成されたP型不純物拡散層3と、チャネル領域2上に形成されハフニウム又はジルコニウムと希土類元素又は第2族元素とを含む絶縁膜4a、4b、及び絶縁膜4a、4b上に形成されたシリコン酸化膜4cを有するゲート絶縁膜4と、ゲート絶縁膜4上に形成されたゲート電極5と、を備えるPMOSトランジスタ。

(もっと読む)

種類および膜厚の異なるゲート絶縁層を有するCMOSデバイス、ならびにその形成方法

high−k金属ゲート構造(310N,310B,310P)によって従来のゲート電極構造(310)を置換するためのプロセスシーケンスにおいて、例えば、選択性の高いエッチングステップ(322,325,327,331)を使用することによって、追加のマスク形成ステップの数を少なく保つことができ、これにより、従来のCMOS技術との高い互換性を保つことができる。更に、ここに開示の技術は、前工程(front-end)のプロセス技術および後工程(back-end)のプロセス技術との互換性を実現し、これにより、トランジスタレベルのほか、コンタクトレベルでも実績のある歪み発生機構を組み込むことが可能となる。  (もっと読む)

(もっと読む)

半導体デバイスの製造方法。

【課題】高誘電体膜とシリコン基板とを分離する、極薄かつ緻密な界面層を形成する半導体デバイスの製造方法を提供する。

【解決手段】本発明の半導体デバイスの製造方法は、シリコン基板表面にシリコン酸化膜を形成する工程(酸化膜形成ステップ)と、シリコン酸化膜を所望膜厚だけ残してエッチングする工程(エッチングステップ)と、エッチング後のシリコン酸化膜上に高誘電体膜を形成する工程(高誘電体膜形成ステップ)とを有する。

(もっと読む)

半導体装置

【課題】 ゲート電極上のシリサイド膜の断線を抑制する。

【解決手段】 ソース・ドレイン領域をデュアルシリサイド構造とし、ゲート電極の仕事関数はn型MISトランジスタ、p型MISトランジスタそれぞれの有するメタルゲート電極により定める構造とし、且つ、メタルゲート電極上の多結晶シリコン層は共通のn+ドーピング層とし、ゲート上シリサイド膜はn型領域に対しショットキー障壁が低くなる材料で形成する。

(もっと読む)

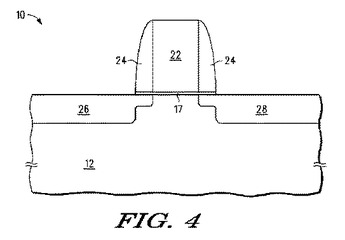

CETスケーリング用高k誘電体の処理方法

半導体装置(10)の作製方法は、上に重なるゲート電極(22)を有するゲート誘電体(17)を作製することを含む。半導体装置(10)は半導体層(12)上に作製される。ジルコン酸ハフニウムを含む高k誘電体(16)は半導体層上に蒸着される。高k誘電体は、水素と窒素を含む雰囲気中で650℃〜850℃の間の温度でアニーリングされる。ゲート電極(22)は高k誘電体上に形成される。高k誘電体機能は、ゲート誘電体(17)での使用のためである。一つの効果は、ゲート漏れのレベルを保持する、またはさらには改善させつつ、トランジスタの性能を向上させることである。  (もっと読む)

(もっと読む)

半導体装置

【課題】それぞれが適した閾値を有するフィン型MOSFETとプレーナ型MOSFETが混載され、且つ少ない工程で製造することができる半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、第1のゲート電極と、前記第1のゲート電極にフェルミレベルピニングを発生させない第1のゲート絶縁膜と、を有するプレーナ型MOSFETと、第2のゲート電極と、前記第2のゲート電極にフェルミレベルピニングを発生させる第2のゲート絶縁膜と、を有するフィン型MOSFETと、を有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】不純物を混ぜなくても立方晶(cubic)、正方晶(tetragonal)又は斜方晶(orthorhombic)のハフニウム酸化物を形成することができる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】シリコン基板1上にHfO2膜3を形成する工程と、HfO2膜3上にゲート電極膜5を形成する工程と、HfO2膜3及びゲート電極膜5が形成されたシリコン基板1に熱処理を施して、HfO2膜3を結晶化する工程と、を含む。熱処理温度は例えば800℃である。

(もっと読む)

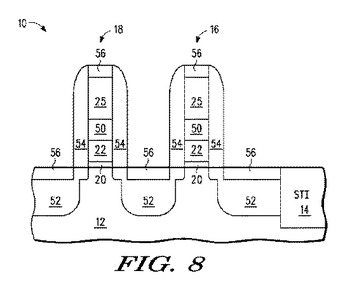

ゲート・ストレッサ及び半導体デバイスを特徴とする半導体デバイスの製造方法

半導体デバイス(10)は半導体層(12)に形成される。ゲート・スタック(16,18)は、半導体層の上にわたって形成され、第1の伝導層(22)及び、第1の層の上の第2層(24)を有する。第1の層は、より伝導性であり、第2の層よりインプラントに対して停止力を提供する。種(46)が、第2の層内にインプラントされる。ソース/ドレイン領域(52)は、ゲート・スタックの対抗する側の半導体層に形成される。ゲート・スタックの下の領域の半導体層にゲート・スタックが応力を働かせるインプラントのステップの後、ゲート・スタックは加熱される。  (もっと読む)

(もっと読む)

101 - 120 / 192

[ Back to top ]