Fターム[5F140BF03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467)

Fターム[5F140BF03]の下位に属するFターム

Fターム[5F140BF03]に分類される特許

21 - 40 / 192

半導体装置の製造方法

【課題】複雑な工程を回避すると共に、高い有効仕事関数値を得ることにより、高歩留まり及び高性能の半導体装置を実現できるようにする。

【解決手段】ダミー電極22をマスクとして、n型活性領域13にp型の不純物イオンを導入することにより、n型活性領域13におけるダミー電極22の両側方にp型のソースドレイン領域25pを形成し、形成されたソースドレイン領域25pに熱処理を施す。熱処理を施した後に、n型活性領域13の上に、ダミー電極22を覆うように層間絶縁膜26を形成し、形成された層間絶縁膜26からダミー電極22を露出し、露出したダミー電極22を除去する。続いて、層間絶縁膜26におけるダミー電極22が除去された凹部26aに、第2の金属電極27を選択的に形成する。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

半導体装置、及びその製造方法

【課題】高品質な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成される半導体領域、半導体領域内に形成され、互いに分離されているソース領域及びドレイン領域、半導体領域内に形成され、ソース領域及びドレイン領域を分離するチャネル領域、チャネル領域上に形成され、1×1019atoms/cm2よりも大きいピーク濃度で、Si、O、またはNとは異なる少なくとも一つの要素を有する界面酸化層、及び界面酸化層上に形成され、実質的に界面酸化層に隣接する深さでhigh―k/界面酸化層接合面を有するhigh―k絶縁層を有するMOS(metal-oxide-semiconductor)トランジスタを備え、少なくとも一つの要素のピーク濃度の少なくとも一つの深さは、実質的にhigh―k/界面酸化層接合面よりも下に位置する。

(もっと読む)

ゲート電極及びその製造方法

【課題】フラットバンド電圧を制御できるとともに、半導体デバイス製造プロセスで使用される高温に曝されても特性の劣化が少ない、nMOSFETのゲート電極を与える。

【解決手段】炭化タンタルにイットリウムを添加した材料でゲート電極を作成する。このゲート電極はイットリウムの添加量に従ってフラットバンド電圧を調節できるとともに、600℃程度の熱処理を受けても特性の劣化が少ない。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】チャネル移動度と閾値電圧とのトレードオフの関係を打破し、チャネル移動度を向上させ、かつ、閾値電圧の低下を抑えた炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】この発明に係る炭化珪素半導体装置1aの製造方法は、炭化珪素エピタキシャル層6を有する炭化珪素基板2の炭化珪素エピタキシャル層6上に、リンをドープした多結晶珪素膜18を形成する工程と、多結晶珪素膜18を熱酸化してゲート絶縁膜12を形成する工程と、を備えた。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

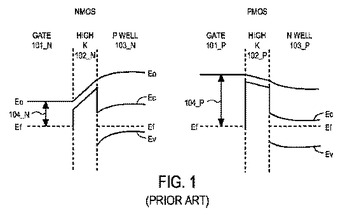

【課題】メタルゲートを用いたCMISまたはCMOS構造の集積回路デバイスにおいて、Nチャネル領域およびPチャネル領域におけるゲート絶縁膜、メタルゲート層等のつくり分けに関しては、種々の方法が提案されているが、プロセスが複雑になる等の問題があった。

【解決手段】本願発明は、CMOS集積回路デバイスの製造方法において、Nチャネル領域およびPチャネル領域において、ゲート電極膜形成前の高誘電率ゲート絶縁膜の電気的特性を調整するためのチタン系窒化物膜を下方のチタンを比較的多く含む膜と、上方の窒素を比較的多く含む膜を含む構成とするものである。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】窒化処理によって低下した閾値電圧を、向上させることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】ベース領域7およびソース領域8を含む炭化珪素ドリフト層6上に二酸化珪素を主成分とするゲート絶縁膜11が形成された炭化珪素基板2を窒化処理する窒化処理工程と、窒化処理工程後、炭化珪素基板2を、一酸化二窒素を含む雰囲気中で600℃以上1000℃以下の温度で熱処理する熱処理工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル形成領域に印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させる半導体装置を提供する。

【解決手段】チャネル形成領域を有する半導体基板10上にゲート絶縁膜20が形成され、ゲート絶縁膜20の上層にゲート電極21が形成され、ゲート電極21の上層にチャネル形成領域に応力を印加する第1応力導入層22が形成されており、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部にソースドレイン領域13が形成されており、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に、チャネル形成領域に第1応力導入層22と異なる応力を印加する第2応力導入層26が形成されている構成とする。

(もっと読む)

半導体装置およびこの半導体装置に用いられる半導体デバイス

【課題】オン抵抗を十分なレベルにまで低減させる。

【解決手段】半導体装置は、半導体デバイス1と、制御装置2とを備える。半導体デバイス1において、本体部3では、半導体層33と第2の半導体層34とが積層し、半導体層33と第2の半導体層34との間の界面の半導体層33側にチャネル領域36が形成される。ソース電極41およびドレイン電極42は、チャネル領域36に電気的に接続されるように本体部3の上に離隔して設けられている。ゲート電極43は、ソース電極41とドレイン電極42との間であって第2の半導体層34の上方に設けられている。制御装置2は、ゲート電極43へのゲート電圧を調節してチャネル領域36において電子91を移動させるとともに、チャネル領域36において電子91を移動させているときに、チャネル領域36のバンドギャップより大きいエネルギーの光を光源5が半導体層33に照射するように光源5を制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】素子分離領域13は、溝11に埋め込まれた酸化シリコン膜からなり、上部が半導体基板1から突出しており、半導体基板1から突出している部分の素子分離領域13の側壁上に、窒化シリコンまたは酸窒化シリコンからなる側壁絶縁膜SW1が形成されている。MISFETのゲート絶縁膜は、ハフニウムと酸素と低しきい値化用の元素とを主成分として含有するHf含有絶縁膜5からなり、メタルゲート電極であるゲート電極GEは、活性領域14、側壁絶縁膜SW1および素子分離領域13上に延在している。低しきい値化用の元素は、nチャネル型MISFETの場合は希土類またはMgであり、pチャネル型MISFETの場合は、Al、TiまたはTaである。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】キャップ材料を使用した半導体装置のウェハ面内における閾値電圧Vtのバラツキを抑制することを目的とする。

【解決手段】まず、半導体基板1001の上に、高誘電率ゲート絶縁膜1006及び第1のキャップ膜1008を順に形成する。次に、熱処理を行って、第1のキャップ膜1008中の第1の金属を高誘電体膜1006に拡散させる。その後、高誘電体膜1006に拡散せずに高誘電体膜1006の上に残存した第1のキャップ膜1008を除去して、第1の金属が拡散した高誘電率ゲート絶縁膜1006Aの上に金属電極1010を形成する。

(もっと読む)

積層膜の形成方法

【課題】 各膜の組成が異なる積層膜を、極めて効率よく、しかも酸化等の不都合が生じることなく形成することができる積層膜の形成方法を提供すること。

【解決手段】 処理室内に基板1を配置し、処理室に、少なくとも、金属カルボニルを含有する原料を含む成膜原料を導入し、CVDにより基板1上に金属カルボニル中の金属を含む複数の膜6a、6bを含む積層膜を形成する積層膜の形成方法であって、上記積層膜に含まれる膜は、同一処理室内で、原料種および/または成膜条件を異ならせて連続成膜され、上記膜の組成が異なる積層膜を形成する。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】CMPによるダミーゲート電極の頭出し工程およびCMPによるメタルゲート電極の形成工程を回避できる製造方法を提供する。

【解決手段】シリサイド膜24S,24D上に選択的に、シリコン膜25S,25Dを形成する工程と、側壁絶縁膜23WA,23WBの間にシリコン基板の表面を露出する凹部23Vを形成する工程と、側壁絶縁膜23WA,23WBの表面および露出されたシリコン基板表面を連続して覆うように、誘電体膜を形成する工程と、シリコン基板上に金属または導電性金属窒化物を含む導電膜を、凹部23Vに誘電体膜を介して充填するように形成する工程と、導電膜をエッチバックし、側壁絶縁膜23WA,23WBの間において凹部23Vを誘電体膜を介して充填するゲート電極を形成する工程と、を含む。

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

デュアル仕事関数ゲート構造

トランジスタを有する半導体チップが記載されている。前記トランジスタは、ゲート誘電体にわたって設けられたゲート電極を有する。前記ゲート電極は、前記ゲート誘電体上に設けられた第1ゲート材料、及び前記ゲート誘電体上に設けられた第2ゲート材料を有する。前記第1ゲート材料は前記第2ゲート材料とは異なる。前記第2ゲート材料はまた、前記ゲート電極のソース領域又はドレイン領域にも設けられている。  (もっと読む)

(もっと読む)

21 - 40 / 192

[ Back to top ]