Fターム[5F140BF03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467)

Fターム[5F140BF03]の下位に属するFターム

Fターム[5F140BF03]に分類される特許

161 - 180 / 192

MOS構造を有する半導体装置およびその製造方法

【課題】製造プロセスを煩雑にすることなく、閾値が異なるMOS構造のそれぞれのゲート電極に適した材料を採用して閾値を適切に制御でき、かつゲート電極からチャネル領域への拡散を顕著としない技術を提供する。

【解決手段】PMOSトランジスタQPはゲート電極GP及びこれとゲート絶縁膜5を介して対峙するN型ウェル31を、NMOSトランジスタQNはゲート電極GN及びこれとゲート絶縁膜5を介して対峙するP型ウェル32を、それぞれ有している。ゲート電極GNは多結晶シリコン層63で構成される一方、ゲート電極GPは金属層64/多結晶シリコン層63の積層構造を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 しきい値電圧のばらつきの少ないゲート電極を有するCMOSデバイスを備えた半導体装置を提供することを可能にする。

【解決手段】 半導体基板に設けられた第1導電型チャネルMISトランジスタと、半導体基板に設けられた第2導電型チャネルMISトランジスタと、を備え、第2導電型チャネルMISトランジスタのゲート電極中の、ゲート絶縁膜との界面から膜厚方向に少なくとも1nm以下の領域での酸素濃度は1020cm−3以上、1022cm−3以下である。

(もっと読む)

ナノ・スケール・チャネルトランジスタのためのブロックコンタクトアーキテクチャ

ナノスケールチャネルデバイスのコンタクトアーキテクチャは、複数の並列半導体本体を有するデバイスのソースまたはドレイン領域に結合されかつその間に延びるコンタクト構造を有する。コンタクト構造は、サブリソグラフィックピッチを有する並列半導体本体と接触することができる。 (もっと読む)

薄膜形成方法

【課題】 転写膜の汚染や分解・変質を生じないレーザ転写による薄膜形成方法を実現する。

【解決手段】 本発明のレーザ転写による薄膜形成方法では、レーザ光9を透過するガラス基板1上に、照射されるレーザ光9によりアブレーションされるアブレーション層(第1の有機膜)2、カーボンブラックを混入させてレーザ光9を遮蔽する効果を持たせた有機膜(第2の有機膜)3、及びグルコースオキシターゼを含む薄膜(酵素膜)からなる転写膜4が順次積層された転写基板5を用意する。この転写基板5の転写膜4と、被転写基板であるp型シリコン基板(回路基板)6を、回路基板6上に設けたスペーサ7を介して対向させる。その後、ガラス基板1側からアブレーション層2にレーザ光9を照射することで、転写膜4aを回路基板6側に転写する。

(もっと読む)

低融点材料で形成する拡張部を備える半導体デバイス

第1の半導体材料からなる基板(100)の表面(S)に沿って形成したゲート電極(1)とゲート絶縁層(2)とを備える半導体デバイスであり、ゲート電極(1)とゲート絶縁層(2)はいずれもスペーサ(3)に囲まれている。本デバイスはまた、それぞれ基板表面より下でゲート電極(1)の2つの対辺に沿って位置するソース領域(4)とドレイン領域(5)とを備える。ソース領域とドレイン領域は各々、基板(100)上に配置され、基板(100)とスペーサ(3)との間で延在する第2の半導体材料からなる部分(6,7)を備える。第2の材料の融点は、第1の材料の融点を下回る。第2の材料からなる部分(6,7)は、ソース(4)およびドレイン(5)領域の拡張部を成す。本半導体デバイスは、MOSトランジスタとすることができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 サリサイドプロセスにおけるシリサイド細線化を防ぎ、設計により近い理想的なシリサイド寸法が確保できるポリサイドゲート電極を有する半導体装置及びその製造方法を提供する。

【解決手段】 基板11上にシリコン酸化膜等のゲート絶縁膜13、ポリシリコン層14を順次形成する。このポリシリコン層14を選択的に除去してポリシリコンパターン141を形成し、側壁として絶縁膜16を形成する。その後、ポリシリコンパターン141の上部を所定厚さT1だけ除去する。これにより、絶縁膜16の上部をポリシリコンパターン141の上面よりも高くする。所定厚さT1は、破線に示すように、ポリシリコンパターン141上に形成しようとするシリサイド層19の側部が絶縁膜16の上部で保護されるような形態となるように設定される。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置において、熱処理によってもゲート電極が安定して所望の仕事関数を維持できるようにする。

【解決手段】 半導体装置は、半導体基板6と、この半導体基板6の上側に接して形成されたゲート絶縁膜1と、このゲート絶縁膜1の上側に金属窒化物または金属窒化珪化物で形成されたゲート電極2とを備え、ゲート絶縁膜1とゲート電極2との間には窒素および珪素の拡散を防止するためのバッファ層3が介在する。好ましくは、バッファ層3は厚みが5nm以下である。ゲート電極2がTi元素を含み、ゲート絶縁膜1がHf元素を含むとするとバッファ層3はチタン膜を含むことが好ましい。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】液体原料、特に有機液体原料を用いたCVD法やALD法によって形成された高誘電率のゲート絶縁膜の上に炭素を有しない界面をもってゲート電極を形成する。

【解決手段】液体原料を用いたCVD法やALD法によって形成されたゲート絶縁膜としての酸化ハフニウム膜の上にゲート電極としてのアモルファスシリコン膜を形成する電極形成工程において、酸化ハフニウム膜が形成されたウエハに対して大気圧未満の圧力下で酸素ガスを用いたパージを実施し、その後、ウエハの存在雰囲気を大気圧未満の圧力に維持したまま、酸化ハフニウム膜の上に電極としてのアモルファスシリコン膜を形成する。絶縁膜としての酸化ハフニウム膜の表面に付着した炭素等の不純物を除去でき、さらに、不純物除去後の絶縁膜表面への不純物の再付着を防止できるので、高誘電率の絶縁膜の上に炭素等の不純物を有しない電極を形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗で耐熱性を有し、閾値変動もないCMOSデバイスを提案する。

【解決手段】本発明の例に関わる半導体装置は、N型半導体層3と、N型半導体層3上に形成される第1ゲート絶縁層10と、第1ゲート絶縁層10上に形成され、金属の炭素化合物を含む第1ゲート電極12とを有するPチャネルMISトランジスタ、及び、P型半導体層2と、P型半導体層2上に形成される第2ゲート絶縁層10と、第2ゲート絶縁層10上に形成される第2ゲート電極11とを有するNチャネルMISトランジスタを備える。

(もっと読む)

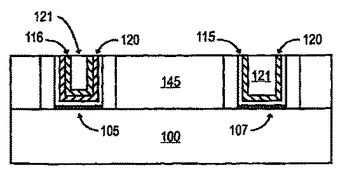

シャロートレンチアイソレーションプロセス

トランジスタとトレンチ構造とを含む構造に関し、トレンチ構造は、トランジスタのチャネル領域内に歪みの一部のみを導入する。  (もっと読む)

(もっと読む)

半導体装置

【課題】 ゲート電極に多結晶Si/金属積層構造を用いつつ、多結晶Si/金属界面の空乏化を抑制することを目的とする。

【解決手段】

ゲート電極が上層に多結晶Si層6、下層に金属層(TiN層7)の積層構造を成して、かつ上部配線とのコンタクト部分は、上部配線がゲート積層構造の下層金属層まで到達させることで、多結晶Siと下層金属(TiN)に電位差が生じないため、空乏層が伸びることなく、ゲートに印加した電圧と同じだけゲート絶縁膜に電圧が掛かり十分なキャリアがチャネル領域に形成され、駆動電流の向上が得られる。また、ゲート加工が基本的には既存技術をそのまま適用できるため、金属ゲート電極を有する半導体装置の製造及びその技術開発が簡略化される。

(もっと読む)

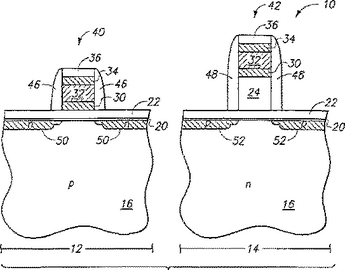

CMOSプロセス用金属ゲート・トランジスタ及びその製造方法

半導体装置(100)を形成する方法は、第一領域(104)を備える半導体基板と、第一領域上にゲート誘電体(108)を形成するステップと、ゲート誘電体上に導電性金属酸化物(110)を形成するステップと、導電性金属酸化物上に耐酸化バリア層(111)を形成するステップと、耐酸化バリア層上にキャッピング層(116)を形成するステップとを含む。一実施形態において、導電性金属酸化物はIrO2,MoO2及びRuO2であり、耐酸化バリア層はTiNを含む。  (もっと読む)

(もっと読む)

MISFETの寿命予測方法

【課題】高誘電率半導体デバイスの寿命を正確に予測することを目的とする。

【解決手段】本発明は、集積回路寿命におけるホットキャリア注入の効果を決定するためのMISFETの試験方法を提供する。本方法は、ドレイン電圧を前記負荷電圧に等しい値に維持する間中、高誘電率誘電体を有するゲートへ正の負荷電圧を印加する。通常の動作電圧よりも大きい負荷電圧の使用が、集積回路の故障及び劣化を加速させる。スレッショルド電圧,トランスコンダクタンス,リニアドレイン電流,飽和ドレイン電流などの電気的パラメータを観測する。観測された電気的パラメータにおけるシフトがデバイス故障を示す。ゲート負荷電圧に対する被加速デバイス寿命の対数をプロットすることによるデータ解析が行われる。動作条件下でのデバイス寿命は、所定のデバイス動作電圧に関するプロットを基に推定することにより予測される。

(もっと読む)

高い誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法

【課題】

高誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法を提供する。

【解決手段】

本発明の金属化合物は、TiCを含み、約4.75乃至約5.3eV、望ましくは、約5eVの仕事関数を有し且つ高誘電率の誘電体および界面層を含むゲート積層体上で熱的に安定する。更に、そのTiC金属化合物は、非常に意欲的な等価酸化膜厚(EOT)およびp型金属酸化物半導体(pMOS)装置における14Åよりも小さい反転層厚へのスケーリングを可能にする1000℃においても非常に効率的な酸素拡散バリアである。

(もっと読む)

高誘電率ゲート誘電体および金属ゲート電極をもつ半導体デバイスの作成方法

半導体デバイスを作成する方法に関する。該方法は、基板上で二酸化ケイ素層に窒素を加えて窒化二酸化ケイ素層を形成することを含む。窒化二酸化ケイ素層の上に犠牲層を形成したのち、犠牲層が除去されて溝が生成される。窒化二酸化ケイ素層の上で溝の中に高誘電率ゲート誘電体層が形成され、該高誘電率ゲート誘電体層の上に金属ゲート電極が形成される。

(もっと読む)

(もっと読む)

半導体構造およびそれを形成する方法(金属酸化物の付着を介して形成されたしきい電圧制御層を含む窒素含有電界効果トランジスタ・ゲート・スタック)

【課題】 ゲート誘電体とゲート電極との間にVt安定化層を含む半導体構造を提供することにある。

【解決手段】 Vt安定化層は、構造のしきい電圧およびフラットバンド電圧を目標値に安定化することができ、窒化金属酸化物または窒素なし金属酸化物を含み、Vt安定化層が窒素なし金属酸化物を含む条件で半導体基板またはゲート誘電体のうちの少なくとも一方が窒素を含む。また、本発明は、このような構造を形成する方法も提供する。

(もっと読む)

半導体MOS装置及びCMOS装置、コンデンサ、及び製造方法

回路装置の作製方法を提供する。導電性にドープされたシリコンと誘電材との間に厚さ20Å以下(または70以下のALDサイクルで生じた厚さ)の金属含有材を形成する。導電性にドープされたシリコンとしてn型を用いることができ、誘電材は高k誘電材を用いることができる。金属含有材は誘電層上へ直接形成でき、導電性にドープされたシリコンは金属含有材上へ直接形成できる。回路装置はコンデンサ構造体あるいはトランジスタ構造体とすることができる。回路装置がトランジスタ構造体である場合はCMOS装置中へ組み入れることができる。本発明による種々装置はメモリ構造体中へ組み入れられる他、電子システムへも組み入れることができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲートの空乏化問題の解消と共に、仕事関数の調整が容易な金属シリサイドのみからなるゲート電極を備え、既存プロセスとのインテグレーション性が高い、コスト的にも優位性がある電界効果トランジスタからなる半導体装置の製造方法を提供することを課題とする。

【解決手段】半導体基板1と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極19と、前記ゲート電極19を挟んでエレベーテッド構造を有するソース・ドレイン8とからなる半導体装置の製造方法であって、前記ゲート電極19を金属シリサイド化する工程を含むことを特徴とする。

(もっと読む)

高誘電率ゲート誘電体層及びシリサイドゲート電極を有する半導体デバイスの製造方法

本発明に係る半導体デバイスの製造方法は、基板上に高誘電率ゲート誘電体層を形成する工程、高誘電率ゲート誘電体層上に障壁層を形成する工程、及び障壁層上に完全にシリサイド化されたゲート電極を形成する工程を有する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 High−k膜を用いたMISFETの電子移動度および正孔移動度を共に増加させ高性能の相補型MISFETを形成する。

【解決手段】 シリコン基板1の表面部にpウェル層2およびnウェル層3が形成され、素子分離領域4により区画されたnチャネルMISFETには、窒素添加のないnチャネル界面層5、窒素添加のないnチャネル高誘電体ゲート絶縁膜6およびnチャネルゲート電極7が形成されている。そして、n型ソース・ドレイン拡散層8が設けられている。これに対して、pチャネルMISFETでは、窒素添加のpチャネル界面層9、窒素添加のpチャネル高誘電体ゲート絶縁膜10およびpチャネルゲート電極11が形成されている。そして、p型ソース・ドレイン拡散層12が設けられている。

(もっと読む)

161 - 180 / 192

[ Back to top ]