Fターム[5F140BF03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467)

Fターム[5F140BF03]の下位に属するFターム

Fターム[5F140BF03]に分類される特許

81 - 100 / 192

半導体装置及びその製造方法

【課題】チャネル幅が狭い場合においても、eWFが十分に低減された閾値電圧が低い半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11と、半導体基板11の上に形成され、第1の元素と第2の元素とを含むゲート絶縁膜26と、ゲート絶縁膜26の上に形成されたゲート電極27とを備えている。ゲート絶縁膜26は、半導体基板11側においてゲート電極27側と比べて第1の元素の含有量が多く、ゲート電極27側において半導体基板11側と比べて第2の元素の含有量が多い。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】NMOSFET及びPMOSFET等のNMOS及びPMOSを有する半導体装置において、ゲート電極の実効仕事関数を、Siバンドギャップのmid-gap付近の値に安定的に設定することが可能な半導体装置及びその製造方法を提供する。

【解決手段】素子分離膜によって分離されてなる、p型拡散層及びn型拡散層を有する半導体基板と、前記半導体基板の、前記p型拡散層及びn型拡散層それぞれの上に形成されてなるゲート絶縁膜と、前記ゲート絶縁膜上に形成された金属膜を含むゲート電極と、前記ゲート絶縁膜と前記金属膜との界面に形成されたGe介在物と、前記金属膜上に形成されたシリコン含有層と、を具えるようにして半導体装置を構成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高誘電率膜をゲート絶縁膜として用いたCISトランジスタの信頼性を向上する。

【解決手段】基板1の主面には、素子分離領域2によって互いに絶縁分離されたpMISトランジスタの活性領域およびnMISトランジスタの活性領域が設けられている。素子分離領域2に係るようにnMISトランジスタの活性領域上にnMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜5が設けられており、そのハフニウム系酸化膜5と素子分離領域2上で接触し、pMISトランジスタの活性領域上にハフニウム系酸化膜5と異なる材料から構成されるpMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜9が設けられている。

(もっと読む)

デュアル金属ゲートのコーナー部

【課題】 デュアル金属ゲートのコーナー部を有する改良された電界効果トランジスタを提供する。

【解決手段】 上記を鑑みて、改善された電界効果トランジスタ(FET)構造体、及び該構造体を形成する方法の実施形態が開示される。このFET構造体の実施形態の各々は、固有のゲート構造体を組み込む。具体的には、このゲート構造体は、FETチャネル領域の中央部分の上方の第1のセクションと、チャネル幅のエッジの上方(すなわち、チャネル領域と隣接する分離領域との間の界面の上方)の第2のセクションとを有する。第1のセクション及び第2のセクションは、これらが異なる有効仕事関数(すなわち、それぞれ第1の有効仕事関数及び第2の有効仕事関数)を有する点で異なる(すなわち、これらは、異なるゲート誘電体層及び/又は異なるゲート導体層を有する)。チャネル幅のエッジにおける閾値電圧が上昇することを確実にするように、異なる有効仕事関数が選択される。

(もっと読む)

半導体基板の製造方法および半導体装置の製造方法

【課題】性能劣化を招く金属元素の半導体基板への侵入及び拡散を防ぐことのできる半導体基板の製造方法および半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体基板の製造方法は、半導体基板1の両面および側面に窒化膜2を形成する工程と、前記窒化膜2上の全面に、シリコンを含む酸化膜3および所定の金属を含む前駆体膜4Aを積層する工程と、前記酸化膜3と前記前駆体膜4Aとを反応させることにより、前記シリコンおよび前記所定の金属を含む自己形成バリア膜4を自己整合的に形成する工程と、を含む。

(もっと読む)

半導体装置、及びその製造方法

【課題】 金属層と半導体層との接続抵抗の上昇を抑えた積層ゲート電極を有する半導体装置、及びその製造方法を提供する。

【解決手段】 半導体装置10は、半導体基板11に形成された第1導電型のソース領域及びドレイン領域14と、ソース領域とドレイン領域との間に形成されたチャネル領域16と、チャネル領域上に形成されたゲート絶縁膜21とを有する。半導体装置10は更に、ゲート絶縁膜上に形成された金属ゲート電極層22と、金属ゲート電極層上に形成された、第1導電型とは逆の導電型である第2導電型の半導体ゲート電極層23とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】SiGe膜をチャネル領域に用いるFETにおいて、このSiGe膜中のGe濃度及びSiGe膜の膜厚のばらつきを抑制する。

【解決手段】シリコンを主成分とする基板と、前記基板に形成され、素子領域を区画する溝と、前記基板上に形成されたSiGe膜と、前記溝の側壁の少なくとも上部において前記側壁の表面から内部に形成された、窒素および炭素のうち少なくともいずれかを含む、シリコン流動防止層と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高速動作が可能なMIPS構造を持つメタルゲートを含む半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜3と、該ゲート絶縁膜3の上に順次形成され、TiN膜4とポリシリコン膜5とにより構成されたゲート電極20の第2のゲート電極部20bと、半導体基板1の上にゲート電極20を覆うように形成された層間絶縁膜8とを有している。層間絶縁膜8及びポリシリコン膜5を貫通して形成されたコンタクト9は、TiN膜4と直接に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】短チャネル効果を抑制すると共に、MISトランジスタの駆動能力が劣化することを防止するMIS(Metal Inserted Semiconductor)トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10における活性領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第1の導電膜14、及び該第1の導電膜14上に形成された第2の導電膜15からなるゲート電極15Aと、活性領域10xにおける第2導電膜15の側方下に形成されたエクステンション領域16と、第1の導電膜14上に、第2の導電膜15の側面と接して形成された第1のサイドウォール17とを備え、第1の導電膜14のゲート長方向の長さは、第2の導電膜15のゲート長方向の長さよりも大きい。

(もっと読む)

半導体装置

【課題】ゲート金属起因の閾値変調効果が制御されたCMISFETを提供する。

【解決手段】半導体基板上に設けられたCMISFETにおいて、pMISFETのゲート電極は、第1のゲート絶縁膜上に形成された第1の金属層と、その上に形成されたIIA族及びIIIA族に属する少なくとも1つの金属元素を含む第1の上部金属層とを具備し、nMISFETのゲート電極は、第2のゲート絶縁膜上に形成された第2の金属層と、第2の金属層上に形成され、前記第1の上部金属層と実質的に同一組成の第2の上部金属層とを具備し、第1の金属層が第2の金属層よりも厚く、第1及び第2のゲート絶縁膜は前記金属元素を含み、第1のゲート絶縁膜に含まれる前記金属元素の原子密度が、第2のゲート絶縁膜に含まれる前記金属元素の原子密度よりも低い。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成する際に、ゲート絶縁膜に金属原子が注入されることを抑制し、ゲートリーク電流の増加や閾値電圧の不安定化等を防止する。

【解決手段】MOSトランジスタを備える半導体装置の製造方法である。半導体基板11上にゲート絶縁膜12を形成する。ゲート絶縁膜12上に金属原子を複数個含むクラスタのイオン13を堆積させ、ゲート電極14の少なくとも最下層を形成する。

(もっと読む)

CMISトランジスタの製造方法

【課題】本発明は、PMISトランジスタ側とNMISトランジスタ側とでシリサイド層の組成のバラツキを防止でき、またトランジスタのゲート形状の不安定化を防止できる、CMISトランジスタの製造方法を提供する。

【解決手段】ゲート絶縁膜103とN−metal104と多結晶シリコン106とが当該順に積層した第一のゲート構造G1を形成する。ゲート絶縁膜103と多結晶シリコン106とが当該順に積層した第二のゲート構造G2を形成する。第一、二のゲート構造G1,G2をマスクした状態で、各ゲート構造G1,G2の両脇における半導体基板101上を、シリサイド化させる。そして、第一、二のゲート構造G1,G2を構成する多結晶シリコン106を、シリサイド化させる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数の半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置およびその半導体装置を容易に製造することのできる半導体装置の製造方法を提供する。

【解決手段】ゲート絶縁膜6の上面上に、全面的に、3〜30nmの厚みのゲート電極用金属膜Mを形成する。次に、ゲート電極用金属膜Mの上面のうちでnFET領域Rn内に属する部分にのみ、全面的に、ゲート電極用金属膜Mとは異種材料の、10nm以下の厚みのn側キャップ層8Aを形成する。その上で、熱処理を行って、n側キャップ層8Aを、その直下のゲート電極用金属膜M内に拡散・反応させて、nFET領域Rn内にn側ゲート電極用金属膜MAを形成する。それ以降は、ポリSi層を堆積した上で、ゲート電極加工を施す。

(もっと読む)

半導体素子

【課題】ドナー元素を含む半導体層を備えた半導体素子を形成する場合に、このドナー元素が上層に拡散することを抑制することができる半導体素子を提供する。

【解決手段】ZnO基板上にGaドープMgZnO層、アンドープMgZnO層、窒素ドープMgZnO層、アンドープ活性層、窒素ドープMgZnO層と積層した積層体でGaの拡散を分析した。アンドープMgZnO層の次の窒素ドープMgZnO層で、拡散してきたGaの濃度が表面側になるにつれて、急激に減少しており、この窒素ドープMgZnO層の上層にGaは拡散していない。このように、ドナー元素を含む同一組成のドナー含有半導体層の一部に、アクセプタ元素を含み前記ドナー含有半導体層と同一組成のアクセプタ含有半導体層を形成することで、ドナー元素の拡散を防止できる。

(もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

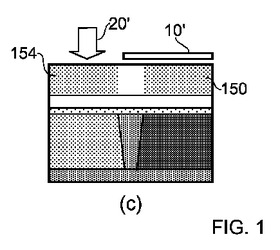

半導体デバイスの製造方法および半導体デバイス

適切な仕事関数の材料のゲート電極を有する半導体デバイスの製造方法を開示する。この方法は、所定数の活性領域(110,120)および該活性領域(110,120)を被覆する誘電体層(130)を含む基板(100)を提供する工程と、前記誘電体層上に積層体(140,150,160)を形成する工程を有する。積層体の形成は、前記誘電体層(130)上に、第1の厚さ、例えば10nm未満を有する第1の金属層(140)を析出させる工程と、該第1の金属層(140)上に、第2の厚さを有する第2の金属層(150)を析出させる工程であり、前記第2の厚さが前記第1の厚さより厚い工程と、前記第2の金属層(150)にドーパント(152,154)を導入する工程と、前記デバイスを温度上昇下にさらし、前記ドーパント(152,154)の少なくとも一部を、前記第2の金属層(150)から前記第1の金属層(140)と前記第2の金属層(150)との界面を越えて、移動させる工程と、前記積層体を所定数のゲート電極(170)にパターニングする工程と、を有する。この方法によれば、ゲート電極は、誘電体層(130)の近くにドーパントプロファイルを有するように形成されるため、ゲート誘電体がドーパントの侵入により劣化することなく、ゲート電極の仕事関数を最適化することができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】同一導電型のチャネル領域を有し、かつ閾値電圧の異なる複数の半導体素子を有する半導体装置を提供する。

【解決手段】閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置において、トランジスタのゲート電極は、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、更に、一方のトランジスタが、ゲート絶縁膜と金属層との間に、第2金属の酸化膜を含む。

(もっと読む)

半導体装置

【課題】ゲルマニウム層に浅いn型不純物拡散領域を形成可能とした半導体装置を提供する。

【解決手段】ゲルマニウムを主成分とするp型半導体と、前記p型半導体の表面に選択的に設けられた一対のn型不純物拡散領域と、前記一対のn型不純物拡散領域により挟まれた前記p型半導体の上に設けられたゲート絶縁層と、前記ゲート絶縁層の上に設けられたゲート電極と、を備え、前記n型不純物拡散領域の少なくとも一部は、シリコン及び炭素から選択された少なくともいずれかの添加元素を含有していることを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに導電型の同じMISトランジスタを備えた半導体装置において、互いに閾値電圧の異なるMISトランジスタを精度良く且つ高性能に実現する。

【解決手段】第1のMISトランジスタLTrは、第1の活性領域1aに形成された第1のチャネル領域3aと、第1のチャネル領域上に形成された高誘電率絶縁膜からなる第1のゲート絶縁膜4aと、第1のゲート絶縁膜上に接する第1の導電部12aと、第2の導電部13aとを有する第1のゲート電極20Aとを備え、第2のMISトランジスタHTrは、第2の活性領域1bに形成された第2のチャネル領域3bと、第2のチャネル領域上に形成された高誘電率絶縁膜からなる第2のゲート絶縁膜4bと、第2のゲート絶縁膜上に接する第3の導電部12bと、第4の導電部13bとを有する第2のゲート電極20Bとを備え、第3の導電部は、第1の導電部よりも薄い膜厚で且つ第1の導電部と同じ組成材料からなる。

(もっと読む)

81 - 100 / 192

[ Back to top ]