Fターム[5F140BF30]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 3層目より上層の材料 (915) | 金属 (751) | 金属化合物(窒化物、酸化物) (127)

Fターム[5F140BF30]に分類される特許

101 - 120 / 127

半導体装置及びその製造方法

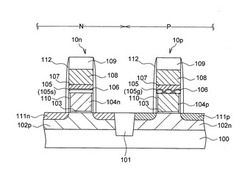

【課題】 ポリメタルゲート構造及びデュアルゲート構造のゲート電極を有する半導体装置において、ポリシリコン層中の不純物の相互拡散を防止すると共に、N型ポリメタルゲート電極とP型ポリメタルゲート電極の抵抗を共に低くすることが可能な半導体装置の製造方法を提供する。

【解決手段】 P型ポリメタルゲート電極10pが、P型ポリシリコン層104pと、P型ポリシリコン層104p上に不連続に配置された複数のタングステンシリサイド(WSi2)粒子105gからなるWSi2層105と、WSi2層105の不連続部分に露出したP型シリコン層104p上及びWSi2層105(WSi2粒子105g)表面に連続的に形成されたシリコン膜106と、窒化タングステン(WN)層107と、タングステン(W)層108とを備えて構成される。

(もっと読む)

イオン注入方法

イオン注入方法は、基板から外側に突出しており、一組で間隔のある近接したフィーチャーを形成することを含んでいる。前記フィーチャーを覆って付与され前記一組で間隔のあるフィーチャーの間のところに開孔を有しているパターンフォトレジスト層によって前記一組で間隔のあるフィーチャーの少なくとも最も外側の部分が、横方向に引っ張られお互いから離間させる。、そのような間隔のあるフィーチャーが横方向に引っ張られながら、前記一組で間隔のあるフィーチャーよりも低く付与される基板材料へスペシーズがイオン注入される。前記イオン注入の後に、前記パターンフォトレジスト層が前記基板から除去される。この発明の他の態様および実施が考えられる。 (もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体と電極の金属との間に働く応力を緩和することが可能な半導体装置の製造方法を提供する。

【解決手段】本発明のCMOS(半導体装置)の製造方法は、シリコン基板1上にゲート絶縁膜6を形成する工程と、ゲート絶縁膜6上にアモルファスシリコン層70を形成する工程と、アモルファスシリコン層70上にゲート電極10を構成するルテニウム(Ru)を含むRu層8を形成する工程と、アモルファスシリコン層70とルテニウムとを反応させることにより、ゲート絶縁膜6とRu層8との界面にシリコンよりもルテニウムの含有量の多いルテニウムシリサイド(Ru−Si)層7を形成する工程とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極とソース/ドレイン領域との間の耐圧不良がなく特性の良好なトレンチゲート型トランジスタを有する半導体装置を提供する。

【解決手段】 まず選択的エピタキシャル成長により、低濃度N型拡散層110が形成されている領域上に、サイドウォール絶縁膜110aに隣接したシリコンエピタキシャル層112を形成する。次いで、熱酸化によりシリコンエピタキシャル層112の表面に薄いシリコン酸化膜112aを形成した後、このシリコン酸化膜112aを介してシリコンエピタキシャル層112中にリン(P)又はヒ素(As)をイオン注入することにより、シリコンエピタキシャル層112全体を低濃度N型拡散層114とした後、さらにリン(P)又はヒ素(As)をイオン注入することにより、シリコンエピタキシャル層112の上層にセルトランジスタのソース/ドレイン領域となる高濃度N型拡散層113を形成する。

(もっと読む)

ポリメタルゲート電極を持つ半導体素子及びその製造方法

【課題】TiN膜及びバッファ層から形成されるバリアー膜を備えるポリメタルゲート電極を持つ半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備える半導体素子である。バリアー膜は、第1金属シリサイド膜上に形成されるTiN膜と、TiN膜と金属膜との間に介在されるバッファ層と、を備える。

(もっと読む)

自己整合され積極的にスケーリングされたCMOSデバイスにおけるゲート電極の金属/金属窒化物二重層のCMOS構造体及び半導体構造体

【課題】 低仕事関数金属の不適切な熱安定性のために、nFET仕事関数とpFET仕事関数との両方を適正にするために用いることができるゲート・スタックを有するCMOS構造体を提供すること。

【解決手段】 本発明は、半導体基板の1つの領域上に配置された少なくとも1つのnMOSデバイスと、半導体基板の別の領域上に配置された少なくとも1つのpMOSデバイスとを含む、CMOS構造体に向けられる。本発明によれば、少なくとも1つのnMOSデバイスは、ゲート誘電体と、4.2eV未満の仕事関数を有する低仕事関数の元素状金属と、その場金属キャッピング層と、ポリシリコン・カプセル化層とを含むゲート・スタックを含み、少なくとも1つのpMOSデバイスは、ゲート誘電体と、4.9eVより大きい仕事関数を有する高仕事関数の元素状金属と、金属キャッピング層と、ポリシリコン・カプセル化層とを含むゲート・スタックを有する。本発明はまた、こうしたCMOS構造体を製造する方法も提供する。

(もっと読む)

半導体素子を形成する方法

【課題】 ゲートリーク電流の低減。

【解決手段】 本発明による半導体の製造方法は、基板を設ける工程と、誘電体層を基板の上に形成する工程と、アモルファス半導体層を誘電体層の上に成長させる工程と、アモルファス半導体層に不純物をドープする工程と、そして高温処理工程をアモルファス層に施して前記アモルファス半導体から結晶化層を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の少なくともゲート絶縁膜側をハフニウムと窒素とを含む膜で形成し、そのハフニウムと窒素とを含む膜中の窒素を適性な組成比にすることで、従来から用いられているPoly−Si電極とほぼ同レベルの良好な移動度を得ることを実現する。

【解決手段】半導体基板11上にゲート絶縁膜14を介してゲート電極15を備えた電界効果トランジスタからなる半導体装置1であって、前記ゲート電極15は少なくとも前記ゲート絶縁膜14側がハフニウムと窒素とを含む膜からなり、前記ハフニウムと窒素とを含む膜は少なくとも窒素を含みかつハフニウムと窒素とに対する窒素の組成比が51%以下である。

(もっと読む)

ゲート電極積層およびゲート電極積層を用いる方法

【課題】エッチングの容易なポリシリコン−メタル積層で構成されるゲート電極構造を提供する。

【解決手段】少なくとも1層のポリシリコン3と少なくとも1層のポリSi1−xGex材料の層4とを有するゲートコンダクタを備える半導体デバイスの基板上のゲート電極積層構造であり、ポリシリコン3とポリSi1−xGex材料の層4のエッチングにより、終点検出が可能であるため、上記構造を効果的にエッチングすることができる。

(もっと読む)

多層ゲート構造を備える半導体素子及びそれの製造方法

【課題】半導体基板と半導体基板上に形成されたドープされた導電膜を含む半導体素子を提供する。

【解決手段】拡散バリヤ膜がドープされた導電膜上に形成される。拡散バリヤ膜は、非晶質半導体物質を含む。オーミックコンタクト膜が拡散バリヤ膜上に形成される。金属バリヤ膜がオーミックコンタクト膜上に形成される。金属膜が金属バリヤ膜上に形成される。これにより、界面抵抗を所望の範囲内に維持できながら、オーミックコンタクト膜下部の導電体にドープされた不純物が外部に拡散することを効果的に防止できて、多層構造を採用した半導体素子の反転キャパシタンス特性などを向上させることができる。

(もっと読む)

MOSトランジスタのためのゲート電極

一態様では、シリコン層(112')に第1の熱処理を施し、このシリコン層(112')上に金属積層体(110')を形成し、この金属積層体に第2の熱処理を施すことによって、トランジスタのゲートを形成する。第1の熱処理は、急速熱アニールステップを含み、第2の熱処理は、急速窒化ステップを含む。本発明により得られたるゲートは、シリコン層と金属積層体との間で比較的低い界面接触抵抗を示し、そのため、このゲートを高速デバイスで使用すると有利である。  (もっと読む)

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】 high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 緻密な膜厚制御を必要とすることなくジャンクション・リークを防ぐことができ、より実効的なMIS型電界効果トランジスタの低抵抗化に必要な厚さの金属シリサイド層が形成可能な半導体装置及びその製造方法を提供する。

【解決手段】 P型のSi基板11表面に、チャネル領域12を隔ててN型のソース/ドレイン拡散層15が形成されている。ソース/ドレイン拡散層15は低濃度エクステンション領域151を有する。ゲート電極14は、ポリシリコン層141上に第1シリサイド層142を有する。ゲート電極14及び絶縁膜スペーサ16を隔ててソース/ドレイン拡散層15上に第2シリサイド層152が設けられている。この第2シリサイド層152は、第1シリサイド層142とは異なる金属を用いて形成されている。

(もっと読む)

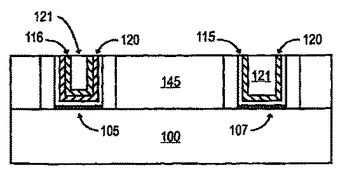

CMOSプロセス用金属ゲート・トランジスタ及びその製造方法

半導体装置(100)を形成する方法は、第一領域(104)を備える半導体基板と、第一領域上にゲート誘電体(108)を形成するステップと、ゲート誘電体上に導電性金属酸化物(110)を形成するステップと、導電性金属酸化物上に耐酸化バリア層(111)を形成するステップと、耐酸化バリア層上にキャッピング層(116)を形成するステップとを含む。一実施形態において、導電性金属酸化物はIrO2,MoO2及びRuO2であり、耐酸化バリア層はTiNを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 N型ポリメタルゲート電極とP型ポリメタルゲート電極の界面抵抗を共に低くすることが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板101上にシリコン膜を形成する工程と、シリコン膜の領域PにP型不純物を、領域NにN型不純物をこの順にイオン注入する工程と、シリコン膜上にシリサイド膜106及び金属膜をこの順で形成する工程と、シリコン膜、シリサイド膜106及び金属膜をパターニングして領域PにP型ポリメタルゲート電極を、領域NにN型ポリメタルゲート電極を形成する工程とを備え、P型不純物のイオン注入後、N型不純物のイオン注入前に第1の熱処理を行ってP型不純物を活性化させ領域Pのシリコン膜をポリシリコン膜103Pとし、N型不純物のイオン注入後、第2の熱処理を行い、N型不純物を活性化させ領域Nのシリコン膜をポリシリコン膜103nにすると共にシリサイド膜106に含まれたガスを除去する。

(もっと読む)

高い誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法

【課題】

高誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法を提供する。

【解決手段】

本発明の金属化合物は、TiCを含み、約4.75乃至約5.3eV、望ましくは、約5eVの仕事関数を有し且つ高誘電率の誘電体および界面層を含むゲート積層体上で熱的に安定する。更に、そのTiC金属化合物は、非常に意欲的な等価酸化膜厚(EOT)およびp型金属酸化物半導体(pMOS)装置における14Åよりも小さい反転層厚へのスケーリングを可能にする1000℃においても非常に効率的な酸素拡散バリアである。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたゲート電極をCo膜を用いてシリサイド化する場合であっても、ゲート電極の抵抗のばらつきを抑制しうる半導体装置及びその製造方法を提供する。

【解決手段】ゲート長Lgが50nm以下のゲート電極30上に、Co膜72を形成する工程と、熱処理を行うことにより、Co膜72とゲート電極30とを反応させ、ゲート電極30の上部にCoSi膜76aを形成する第1の熱処理工程と、Co膜72のうちの未反応の部分を選択的にエッチング除去する工程と、熱処理を行うことにより、CoSi膜76aとゲート電極30とを反応させ、ゲート電極30の上部にCoSi2膜42aを形成する第2の熱処理工程とを有し、第1の熱処理工程では、CoSi膜76aの幅wに対するCoSi膜76aの高さhの比h/wが0.7以下となるように、CoSi膜76aを形成する。

(もっと読む)

高誘電率ゲート誘電体および金属ゲート電極をもつ半導体デバイスの作成方法

半導体デバイスを作成する方法に関する。該方法は、基板上で二酸化ケイ素層に窒素を加えて窒化二酸化ケイ素層を形成することを含む。窒化二酸化ケイ素層の上に犠牲層を形成したのち、犠牲層が除去されて溝が生成される。窒化二酸化ケイ素層の上で溝の中に高誘電率ゲート誘電体層が形成され、該高誘電率ゲート誘電体層の上に金属ゲート電極が形成される。

(もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 サリサイド工程で形成されるシリサイド層のシート抵抗ばらつきを抑制する。

【解決手段】 サリサイド工程の際にCo膜上に堆積されるTiN保護膜の膜厚を、ナノグレイン構造あるいはアモルファス構造を有するように減少させる。前記TiN保護膜として、Tiに富む組成の膜を使う。

(もっと読む)

半導体装置及びその製造方法

【課題】

ポリメタル構造のゲート電極を有するMOSFET、特に、DRAMのメモリセルトランジスタの接合リークをよりいっそう低減する。

【解決手段】

半導体基板上に、ゲート絶縁膜、ポリシリコン膜、タングステンなどの高融点金属膜、ゲートキャップ絶縁膜を順次積層し、エッチングによりゲートキャップ絶縁膜および高融点金属膜を選択的に除去する。その後、ゲートキャップ絶縁膜、高融点金属膜及びポリシリコン膜の側面に、シリコン窒化膜及びシリコン酸化膜からなる2重の保護膜を形成し、これをマスクとして用いてポリシリコン膜をエッチングする。その後、ライト酸化処理を行って、ポリシリコン膜の側面にシリコン酸化膜を形成する。

(もっと読む)

101 - 120 / 127

[ Back to top ]