Fターム[5F140BF30]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 3層目より上層の材料 (915) | 金属 (751) | 金属化合物(窒化物、酸化物) (127)

Fターム[5F140BF30]に分類される特許

41 - 60 / 127

半導体装置

【課題】ゲート金属起因の閾値変調効果が制御されたCMISFETを提供する。

【解決手段】半導体基板上に設けられたCMISFETにおいて、pMISFETのゲート電極は、第1のゲート絶縁膜上に形成された第1の金属層と、その上に形成されたIIA族及びIIIA族に属する少なくとも1つの金属元素を含む第1の上部金属層とを具備し、nMISFETのゲート電極は、第2のゲート絶縁膜上に形成された第2の金属層と、第2の金属層上に形成され、前記第1の上部金属層と実質的に同一組成の第2の上部金属層とを具備し、第1の金属層が第2の金属層よりも厚く、第1及び第2のゲート絶縁膜は前記金属元素を含み、第1のゲート絶縁膜に含まれる前記金属元素の原子密度が、第2のゲート絶縁膜に含まれる前記金属元素の原子密度よりも低い。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13、チャネル形成領域12、ゲート電極423、ゲート絶縁膜430を備え、ゲート絶縁膜430はゲート絶縁膜本体部430A及びゲート絶縁膜延在部430Bから構成されており、ゲート電極を構成する第1層431はゲート電極の側面部の途中まで薄膜状に形成されており、第2層の外側層432Aは第1層431の上に薄膜状に形成されており、第2層の内側層432Bは第2層の外側層で囲まれた部分を埋め込んでおり、第3層の外側層433Aは第2層の内側層、外側層、ゲート絶縁膜延在部を覆い、ゲート電極の頂面まで薄膜状に形成されており、第3層の内側層433Bはゲート電極の残部を占めている。

(もっと読む)

二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

(もっと読む)

半導体装置

【課題】メタルをゲート電極材料に用いたCMIS素子の閾値を低減する。

【解決手段】p型MISトランジスタQpのゲート絶縁膜5上に設けられたp型ゲート電極7は、順に、カチオン比でAlが10%以上50%以下のTiAlNから構成される第1金属膜30と、TiNから構成され、膜厚が5nm以下の第2金属膜31と、Siを主成分として含有する導電体膜32とが積層された構造を有している。また、n型MISトランジスタQnのゲート絶縁膜5上に設けられたn型ゲート電極6は、順に、第2金属膜31と、導電体膜32とが積層された構造を有している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜の信頼性および半導体装置の性能を確保可能である半導体装置の製造方法および半導体装置を提供する。

【解決手段】本発明にかかる半導体装置の製造方法は、Si基板100上にゲート絶縁膜103を形成するゲート絶縁膜形成工程と、ゲート絶縁膜103上に第1の金属膜を形成する第1の金属膜形成工程と、第1の金属膜上に金属電極104を構成する第2の金属膜を形成する第2の金属膜形成工程と、熱処理を行なってゲート絶縁膜103と第1の金属膜との間にゲート絶縁膜103と第1の金属膜との反応膜118を形成する反応膜形成工程とを行なって、第1の金属膜形成工程時のゲート絶縁膜103の損傷を回復させている。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電率ゲート絶縁膜とメタルゲート電極を用いたメタルゲートCMOSの製造方法を簡略化する。

【解決手段】 高誘電率ゲート絶縁膜6上にシリコン膜7を形成し、PMOS領域のシリコン膜7のみを選択的に窒化してSiN膜9に置換する。そしてNMOS領域上のシリコン膜7及びPMOS領域上のSiN膜9上にキャップ膜としてのLa(O)膜11及びメタル電極のW膜12を形成した後、加熱処理して、La(O)膜11のLa元素をNMOS領域の高誘電率ゲート絶縁膜に拡散させる。この際、PMOS領域においては、SiN膜9によりLa元素の拡散をブロックする。これにより、NMOSFETとPMOSFETの作りわけを容易に行える。また、窒化されやすい高誘電率ゲート絶縁膜6であれば、シリコン膜7を省略して、窒化処理によりPMOS領域の高誘電率ゲート絶縁膜6だけを選択的に窒化してもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】改良された縦型のMOSトランジスタを備える半導体装置及びその製造方法を提供する。

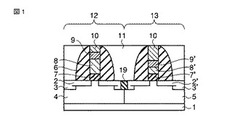

【解決手段】半導体装置は、半導体基板10の主面に対してほぼ垂直に延在するチャネル領域22と、チャネル領域22の下部に設けられた第1の拡散層領域22aと、チャネル領域の上部に設けられた第2の拡散層領域22bと、半導体基板10の主面に対してほぼ垂直に延在し、ゲート絶縁膜30を介してチャネル領域22の側面に設けられた第1のゲート電極34と、半導体基板10の主面とほぼ平行に延在し、第1のゲート電極34の上部に接続された第2のゲート電極35aと、第1の拡散層領域22aに接続され、第2のゲート電極と交差する埋め込み配線21を備えている。第2のゲート電極35aの平面的な位置は、第1のゲート電極34の平面的な位置に対してオフセットされている。

(もっと読む)

半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

(もっと読む)

半導体素子のリセスゲート及びその製造方法

【課題】リセスゲート及びこれを含む半導体素子の製造方法を提供する。

【解決手段】半導体素子のリセスゲートは、基板110と、金属層165と、ポリシリコン層と、ポリシリコン層に隣接し、金属層165から離隔され、形成されたソース領域及びドレーン領域と、を含む。半導体素子の形成方法は、基板110の上にソース/ドレーン120層を形成する段階と、リセス112を形成し、第1導電層パターン145を形成する段階と、第1導電層パターン145上に第2導電層を形成する段階、ソース/ドレーン層120と重畳されるように第2導電層パターン156を形成する段階と、前記第2導電層パターン156と、前記ソース/ドレーン層120上に絶縁層を蒸着する段階と、第2導電層パターン156上にキャップを形成するように絶縁層を平坦化する段階と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲートラストプロセスで形成されたゲート構造において、ソース・ドレイン領域に接続するコンタクトとゲート電極とのショートを防ぐ。

【解決手段】半導体装置100は、ゲートラストプロセスで形成された第1のゲート210を含む。第1のゲート210は、絶縁膜中に形成された第1の凹部内の底面に形成されたゲート絶縁膜、当該第1の凹部内のゲート絶縁膜上に形成されたゲート電極、および当該第1の凹部内のゲート電極上に形成された保護絶縁膜140を含む。また、半導体装置100は、第1のゲート210の両側方のN型不純物拡散領域116aに接続され、第1の凹部よりも径が大きい第2の凹部内に埋め込まれたコンタクト134を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル及びpチャネルのゲート構造が異なり且つメタルゲート電極を有する半導体装置において、ゲート電極パターン形成時のドライエッチングでゲート絶縁膜の突き抜けが発生しないようにする。

【解決手段】ゲート絶縁膜105と接する第2ゲート電極材料膜(TiN膜)111がゲート電極151の一部として形成されないnチャネル領域103上に、第2ゲート電極材料膜(TiN膜)111のエッチング時にオーバーエッチング吸収層として機能する第1ゲート電極材料膜(ポリシリコン膜)107を予め形成しておく。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】仕事関数が所望の値に制御されたメタルゲート電極を備える半導体装置を提供する。

【解決手段】半導体基板2上に、ゲート絶縁膜4を介して、N等を含有する仕事関数制御層5、SiまたはAlを含んだ中間層6、およびMoN層等の低抵抗層7が積層された構造を有するメタルゲート電極を形成する。その形成時には、ゲート絶縁膜4上に仕事関数制御層5、中間層6および低抵抗層7の各層の積層後、ゲート加工を行い、LDD領域9、サイドウォール8およびソース・ドレイン領域10を順に形成して、半導体基板2に導入した不純物の活性化アニールを行う。仕事関数制御層5と低抵抗層7との間に中間層6を設けたことにより、仕事関数制御層5へのあるいは仕事関数制御層5からのN等の拡散が抑制され、その仕事関数の変動が抑制されるようになる。

(もっと読む)

半導体装置及びその製造方法並びにデータ処理システム

【課題】トレンチゲート型トランジスタのサブスレショルド特性の向上を図りつつ、ゲートトレンチの幅が縮小された高性能な半導体装置を提供する。

【解決手段】ゲートトレンチ16の底部16bは、STI14から相対的に遠い第1の底部16b1と、STI14から相対的に近い第2の底部16b2を有している。そして、活性領域10aのうち、ゲートトレンチの第2の底部16b2を構成する部分は、側壁チャネル領域10dを構成し、ゲート電極18とSTI14との間に挟まれた薄膜SOI構造を有している。一方、ゲートトレンチの第1の底部16b1を構成する部分は、副チャネル領域10eとして機能する。第2の底部16b2の曲率半径は第1の底部16b1の曲率半径よりも大きい。ゲートトレンチ16の幅方向の略中央部分においては、トレンチの底面が略平坦であるのに対し、幅方向の端部においては、トレンチの底面がほぼ全体的に湾曲している。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜が大気やメタル電極のエッチング液等に曝されて劣化することなく、仕事関数の異なるnMOS、pMOSに適したメタルゲートMISFETを含む半導体装置の製造方法を提供する。

【解決手段】 メタル電極を有するn型MISトランジスタ及びp型MISトランジスタを備えた半導体装置の製造方法であって、単結晶シリコン基板100上に設けられたゲート絶縁膜102と、ゲート絶縁膜102上に設けられた第一の金属膜103、第二の金属膜104、第三の金属膜105、導電層106を備えたゲート電極108とを備えた構造であって、熱工程によって第二の金属膜104の構成元素を第一の金属膜103を通してゲート絶縁膜102中へ拡散させることによって、n型MISトランジスタ及びp型MISトランジスタそれぞれに適した仕事関数に変化させる。

(もっと読む)

nチャネルMOSトランジスタおよびその製造方法、半導体装置

【課題】ゲートファーストプロセスで形成できる、金属化合物をゲート電極パターンとして使うnチャネルMOSトランジスタにおいて、pチャネルMOSトランジスタのゲート電極パターンに使われる金属化合物に対し、前記nチャネルMOSトランジスタのゲート電極パターンに使われる金属化合物の仕事関数差を増大させる。

【解決手段】nチャネルMOSトランジスタは、p型シリコン活性領域上にゲート絶縁膜を介して形成された導電性金属窒化物よりなるゲート電極パターンと、前記p型シリコン活性領域中、前記ゲート電極パターンの一方および他方の側にそれぞれ形成されたn型のソースおよびドレイン領域と、を含み、前記導電性金属窒化物は、SiおよびV族元素を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ホウ素(B)のゲート絶縁膜の突き抜けや金属シリサイド膜による不純物の吸収によって生じるポリシリコン膜中の不純物の空乏化を防止する。

【解決手段】半導体装置100は、ゲート絶縁膜13と、ゲート絶縁膜13上に形成されたゲート電極14とを備える。ゲート電極14は、ドープドポリシリコン膜21a、21b、21cと、金属シリサイド膜22aとを備えている。ドープドポリシリコン膜21a、21cは、第1の不純物を含んでおり、ドープドポリシリコン膜21bは、反対の導電型を有する第2の不純物を含んでいる。これにより、ポリシリコン中の不純物の拡散工程やその後の熱負荷工程において、第2のドープドポリシリコン膜中の不純物の過度な拡散が抑制され、金属シリサイド膜が不純物を吸収することによるポリシリコン膜中の不純物の空乏化が防止される。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに隣接するシリコンエピタキシャル層同士のショートを防止する。

【解決手段】活性領域13の露出面をドライエッチング又はウェットエッチングで掘り下げることにより、活性領域13の露出面には凹部13aが形成される。これにより、素子分離領域12を構成するフィールド酸化膜12の側面部分12aが露出し、凹部13aの周囲がフィールド酸化膜の側面部分12aで囲まれた状態となる。その後、凹部13aが形成された活性領域13の露出面にシリコンエピタキシャル層19を形成する。ここで、活性領域の露出面は掘り下げられており、活性領域13の幅方向の両端はフィールド酸化膜による壁で囲われていることから、シリコンエピタキシャル層19の横方向への成長を抑制することができ、互いに隣接するシリコンエピタキシャル層19、19間のショートを防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲートトランジスタにおいて、溝に埋め込まれたゲート電極とゲート絶縁膜との界面にボイドが形成されることを防止する。

【解決手段】半導体基板1に埋め込まれた素子分離絶縁膜3により絶縁分離された活性領域4と、ゲート絶縁膜5を介して活性領域4上を跨ぐように形成されたゲート電極6と、ゲート電極6を挟んだ両側の活性領域4に形成されたソース領域7a及びドレイン領域7bとを有し、活性領域4に溝8が設けられて、この溝8の内側にゲート絶縁膜5を介してゲート電極6の一部が埋め込まれてなるトレンチゲートトランジスタ51を備える半導体装置であって、溝8が少なくとも上端開口部よりも下部側において幅広となる形状を有し、溝8に埋め込まれたゲート電極6内に外殻層13aで覆われた中空部(ボイド)14が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】フィン下部でのVthの上昇が得られると共に、サブチャネルによるソース領域とドレイン領域との間のリーク電流を抑えることを可能とした半導体装置及びその製造方法を提供する。

【解決手段】基板2に埋め込まれた素子分離絶縁膜3により絶縁分離された活性領域4と、活性領域4上に形成されたゲート絶縁膜5と、ゲート絶縁膜5を介して活性領域4上を跨ぐように形成されたゲート電極6とを備え、活性領域4の両側に溝15が設けられ、この溝15の内側にゲート絶縁膜5を介してゲート電極6の一部が埋め込まれることによって、溝15の間で立ち上がり形成されたフィン16をゲート電極6が跨ぐように形成されたフィン型のチャネル構造を有するフィン型FET1において、ゲート絶縁膜5の溝15の底面15aに接する部分の膜厚SBをフィン16の上面16bに接する部分の膜厚STよりも厚くする。

(もっと読む)

半導体装置及びその製造方法、並びに、データ処理システム

【課題】トランジスタを有する半導体装置において、チャネル長が短くなることを防止しつつ、ソース/ドレイン拡散層を深さ方向に拡大する。

【解決手段】半導体装置は、素子分離領域11に囲まれた活性領域12cと、活性領域12cを横切るゲート電極13a,13bと、ゲート電極13a,13bの両側に位置し活性領域12c内に形成されるソース/ドレイン拡散層20,21とを備える。ソース/ドレイン拡散層20,21が、活性領域12c内に埋め込まれた、不純物を含有する埋め込みプラグ20b,21bから拡散した不純物によって形成された不純物拡散層から成る。

(もっと読む)

41 - 60 / 127

[ Back to top ]