Fターム[5F140BG30]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 堆積 (2,821) | PVD (888)

Fターム[5F140BG30]に分類される特許

161 - 180 / 888

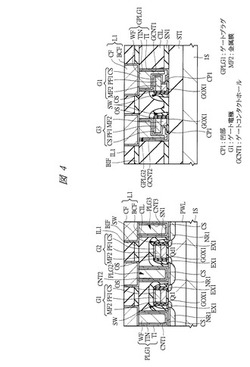

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層上に第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、ソース電極およびドレイン電極の間の窒化物半導体積層体における、第1窒化物半導体層の一部および第2窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域上に形成された窒化物半導体膜と、リセス領域の内壁面、および第2窒化物半導体層の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを有し、第2窒化物半導体層は、第1窒化物半導体層に比べて広い禁制帯幅を有し、窒化物半導体膜の上面は、第1窒化物半導体層の上面よりも低いことを特徴とする。

(もっと読む)

電界効果トランジスタ、半導体基板及び電界効果トランジスタの製造方法

【課題】高いチャネル移動度を有する電界効果トランジスタを提供する。

【解決手段】ゲート絶縁層と、前記ゲート絶縁層に接する第1半導体結晶層と、第1半導体結晶層に格子整合または擬格子整合する第2半導体結晶層とを有し、前記ゲート絶縁層、前記第1半導体結晶層および前記第2半導体結晶層が、ゲート絶縁層、第1半導体結晶層、第2半導体結晶層の順に配置されており、前記第1半導体結晶層がInx1Ga1−x1Asy1P1−y1(0<x1≦1、0≦y1≦1)であり、前記第2半導体結晶層がInx2Ga1−x2Asy2P1−y2(0≦x2≦1、0≦y2≦1、y2≠y1)であり、前記第1半導体結晶層の電子親和力Ea1が前記第2半導体結晶層の電子親和力Ea2より小さい電界効果トランジスタを提供する。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を有するMISFETを備えた半導体装置の信頼性向上を図る。

【解決手段】nチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとLaとOとを主成分として含有するHf含有絶縁膜4aを形成し、pチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとAlとOとを主成分として含有するHf含有絶縁膜4bを形成する。それから、金属膜7とシリコン膜8を形成し、これらをドライエッチングでパターニングしてゲート電極GE1,GE2を形成する。その後、ゲート電極GE1,GE2で覆われない部分のHf含有絶縁膜4a,4bをウェットエッチングで除去するが、この際、フッ酸を含有しない酸性溶液でのウェット処理とアルカリ性溶液でのウェット処理とを行ってから、フッ酸を含有する酸性溶液でのウェット処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。一部の構造及び方法は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。一部の構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得る。  (もっと読む)

(もっと読む)

III族窒化物半導体からなる半導体装置およびその製造方法、電力変換装置

【課題】ノーマリオフでオン抵抗の低いHFETを実現すること。

【解決手段】HFET100は、第1キャリア走行層103上の互いに離間した2つの領域上に、2つに分離して形成されたノンドープのGaNからなる第2キャリア走行層104と、2つの分離した第2キャリア走行層104上にそれぞれ位置するAlGaNからなるキャリア供給層105を有している。第2キャリア走行層104とキャリア供給層105は、第1キャリア走行層103上に選択的に再成長させて形成した層である。第2キャリア走行層104とキャリア供給層105のヘテロ接合界面110は平坦性が高く、そのヘテロ接合界面110近傍は再成長に伴って混入した不純物はほとんど見られないため、2DEGの移動度を低下させることがなく、オン抵抗が低減されている。

(もっと読む)

埋め込みストレッサを有する高性能FETを形成するための方法および構造

【課題】 高性能の半導体構造およびかかる構造を製造する方法を提供する。

【解決手段】 半導体構造は、半導体基板12の上面14上に位置する、例えばFETのような少なくとも1つのゲート・スタック18を含む。構造は更に、少なくとも1つのゲート・スタックのチャネル40上にひずみを誘発する第1のエピタキシ半導体材料34を含む。第1のエピタキシ半導体材料は、少なくとも1つのゲート・スタックの対向側に存在する基板内の1対のくぼみ領域28の実質的に内部で少なくとも1つのゲート・スタックの設置場所に位置する。くぼみ領域の各々において第1のエピタキシ半導体材料の上面内に拡散拡張領域38が位置する。構造は更に、拡散拡張領域の上面上に位置する第2のエピタキシ半導体材料36を含む。第2のエピタキシ半導体材料は、第1のエピタキシ半導体材料よりも高いドーパント濃度を有する。

(もっと読む)

多結晶シリコン・ゲート上のサリサイドの抵抗を改善するための方法およびデバイス

【課題】幅の狭いポリサイドゲートにおけるシリサイドの抵抗が改善されたゲート電極構造の製造方法を提供する。

【解決手段】リセスが形成されたシリコン酸化膜からなる厚い内部スペーサ、およびシリコン窒化膜からなる厚い外部スペーサを有する多結晶シリコンゲートを形成する。多結晶シリコン上にチタンをデポジションし、アニールによりチタンシリサイド層260を形成する。チタンシリサイド層は多結晶シリコンより幅広く形成され、シリコン酸化膜からなる厚い内部スペーサによって制約を受けず、応力を受けない。

(もっと読む)

半導体装置及びその製造方法

【課題】 高誘電率ゲート絶縁膜を用い、PMOS、NMOSそれぞれに適した仕事関数を有するCMOSFETを有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板の主面に素子分離領域によって、絶縁分離されたP型及びN型領域を形成する工程と、前記第P型及びN型領域上にシリコン酸化膜或いはシリコン酸窒化膜からなる第一の絶縁膜を形成する工程と、前記P型領域上の前記第一の絶縁膜上にランタン酸化膜を形成する工程と、前記P型領域上の前記ランタン酸化膜及び前記N型領域上の前記第一の絶縁膜上にハフニウム或いはジルコニウムを含む第二の絶縁膜を形成する工程と、前記第二の絶縁膜上にTixNyとするとx/y<1を満たすチタンナイトライド膜を形成する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体ゲート絶縁膜/メタルゲート電極のMOSトランジスタ構造において、メタルゲート電極側壁の酸化層を抑制し、トランジスタ駆動能力を改善する。

【解決手段】基板101上に、金属含有膜110を形成する工程(a)と、反応室内において金属含有膜にアンモニアラジカルを曝露する工程(b)と、反応室内に不活性ガスを供給し、工程(b)において生じたガスを排気する工程(c)と、工程(b)及び工程(c)を所定の回数繰り返した後に、大気曝露することなく、反応室内において金属含有膜110を覆うシリコン窒化膜100aを形成する工程(d)とを備える。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極として窒化チタン膜とシリコン膜の積層膜を用いたときに、窒化チタン膜が消失することを抑制する。

【解決手段】まず基板にゲート絶縁膜を形成する(ステップS10)。次いで、第1の基板温度で成膜処理を行うことにより、ゲート絶縁膜上に結晶化した窒化チタン膜を形成する(ステップS20)。次いで、第1の基板温度より低い第2の基板温度で成膜処理を行うことにより、窒化チタン膜上にシリコン膜を形成する(ステップS30)。次いで、窒化チタン膜及びシリコン膜を選択的に除去することにより、ゲート絶縁膜上に位置するゲート電極を形成する(ステップS40)。

(もっと読む)

集積回路構造及びその製造方法

【課題】 非対称的なソース及びドレイン領域を有する構造を提供する。

【解決手段】 本発明の方法は、少なくとも1つの半導体チャネル領域を有する基板と、半導体チャネル領域を覆うように基板の上面に設けられたゲート誘電体層と、ゲート誘電体層上のゲート導電体とを有する構造を形成する。非対称的な側壁スペーサがゲート導電体の側壁に配置され、そして非対称的なソース及びドレイン領域が半導体チャネル領域に隣接して基板内に配置される。ソース及びドレイン領域の一方は、他方よりもゲート導電体の中心に近づけられる。ソース及びドレイン領域は、半導体チャネル領域に物理的な応力を与える材料で構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTを小さく保ちつつ、より高い実効仕事関数を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101のn型活性領域103の上に形成された第1のゲート絶縁膜107と、第1のゲート絶縁膜107の上に形成された第1のゲート電極111とを有している。第1のゲート絶縁膜107は、ハフニウム及びアルミニウムを含み、且つ中央部において上部及び下部よりもアルミニウムの濃度が高い。第1のゲート電極111はチタンを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リークを抑制しながら、キャリアの移動度向上とチャネル中でのキャリア速度の増加を実現することができるトランジスタを提供する。

【解決手段】半導体基板10のチャネル形成領域にチャネル方向に第1の幅を有するSiGe層15が埋め込まれ、チャネル形成領域上にゲート絶縁膜28が形成され、ゲート絶縁膜上に、第1の幅より大きい第2の幅を有してSiGe層の形成領域からはみ出す領域を有するゲート電極29が形成され、チャネル形成領域を挟む半導体基板においてエクステンション領域12を有するソースドレイン領域13が形成されて、電界効果トランジスタが構成されており、エクステンション領域と半導体基板の接合面から伸びる空乏層がSiGe層に達しないようにエクステンション領域とSiGe層が離間されている。

(もっと読む)

半導体装置及びその製造方法

【課題】p型MISトランジスタのゲート絶縁膜の酸化膜換算膜厚の厚膜化を抑制しつつ、p型MISトランジスタの実効仕事関数を増加させて、低閾値電圧を有するn型,p型MISトランジスタを実現する。

【解決手段】半導体装置は、第1,第2のMISトランジスタnTr,pTrを備えている。第1のMISトランジスタnTrは、第1の活性領域10a上に形成され、第1の高誘電率膜14Xaを有する第1のゲート絶縁膜14Aと、第1のゲート電極18Aとを備えている。第2のMISトランジスタpTrは、第2の活性領域10b上に形成され、第2の高誘電率膜14xを有する第2のゲート絶縁膜14Bと、第2のゲート電極18Bとを備えている。第2の高誘電率膜14xは、第1の調整用金属を含む。第1の高誘電率膜14Xaは、第2の高誘電率膜14xよりも窒素濃度が高く、且つ、第1の調整用金属を含まない。

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層と、下地半導体層上に第1窒化物半導体層、第2窒化物半導体層、および第3窒化物半導体層が順次積層された窒化物半導体積層体と、ソース電極およびドレイン電極と、第2窒化物半導体層および第3窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域の内面および窒化物半導体積層体の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを含み、絶縁膜に接する第1窒化物半導体層の上面と、第2窒化物半導体層に接する第1窒化物半導体層の上面とに段差がないことを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】拡散層とゲート電極との少なくとも1つの上に耐熱性が向上したNiSi膜が形成された半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Si基板200と、Si基板200内に形成された拡散層10と、Si基板200上にSiを用いて形成されたゲート電極20との少なくとも1つと、前記拡散層10と前記ゲート電極20との少なくとも1つ上に接触して形成されたP元素を含有したNiSi膜40,42と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、高誘電率膜を用いた相補型トランジスタの実効仕事関数を調整して適切なしきい値電圧を実現する際に、エッチング工程数を低減するとともに、エッチングダメージの発生を回避する。

【解決手段】 nチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第1のゲート絶縁膜と第1金属ゲート電極との間にアルミニウム膜を設けるとともに、pチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第2ゲート絶縁膜と第2金属ゲート電極との間に酸化アルミニウム膜を設ける。

(もっと読む)

半導体装置の製造方法

【課題】金属ゲート電極/高誘電体ゲート絶縁膜構造のMISトランジスタを有する半導体装置を高性能化する。

【解決手段】シリコン基板1上に、順に、ハフニウムおよび酸素を主体とする高誘電体膜hk1と、第1金属および酸素を主体とし、化学量論的組成よりも多くの第1金属を含むpMIS用キャップ膜Cp1を形成する。その後、シリコン基板1に、第1熱処理と第2熱処理とを順に施す。続いて、pMIS用キャップ膜Cp1上にゲート電極用金属膜EM1を形成し、これらを加工することでpMIS用金属ゲート電極pG1とpMIS用高誘電率ゲート絶縁膜pI1とを形成する。特に、第1熱処理では高誘電体膜hk1中の余剰酸素を除去し、第2熱処理では高誘電体膜hk1中にpMIS用キャップ膜Cp1中の第1金属を拡散させる。第1熱処理は、第2熱処理よりも低い温度で施す。

(もっと読む)

161 - 180 / 888

[ Back to top ]