Fターム[5F140BH15]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054) | LDD(Lightly doped dorain−source) (1,105)

Fターム[5F140BH15]に分類される特許

961 - 980 / 1,105

半導体基板の製造方法及び半導体装置の製造方法

【課題】 ヘテロエピタキシャル成長膜の、応力の緩和と、緩和に伴って発生し表面へ貫通する結晶欠陥の密度の抑制を両立させるために要求される、膜厚に対する制限を低減し、プロセス設計の自由度を向上させる。

【解決手段】 単結晶半導体基板10の上に単結晶半導体基板10とは格子定数及び/又は熱膨張率が異なる第1単結晶半導体層12を成長させた後に、水素を含む還元性雰囲気中で熱処理することにより、第1単結晶半導体層12の表面は平坦化され、結晶欠陥は単結晶半導体基板10との界面近傍の領域14に局在化され、表面近傍の領域16に加わる応力は緩和される。この熱処理工程の後に実施される第2成長工程において、下地となる第1単結晶半導体層12はその応力が緩和されているので、第1単結晶半導体層12とは格子定数及び/又は熱膨張率が異なる第2単結晶半導体層18に応力が加わり、良質な歪み半導体基板を得ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体措置で発生した熱を放熱しやすくすることによってESD耐圧に優れた半導体装置およびその製造方法を提供する。

【解決手段】 拡散層領域3に形成されたチャネル11の上には、ゲート絶縁膜7を介してゲート電極8が設けられている。また、ゲート電極8の側壁部には、サイドウォール9が形成されている。そして、ゲート電極8上とソース・ドレイン領域5上の一部とに、ゲート電極8およびサイドウォール9を被覆するようにしてシリサイドプロテクション膜10が形成されている。シリサイドプロテクション膜10が設けられていないソース・ドレイン領域の上には、シリサイドプロテクション膜10に隣接して金属シリサイド膜6が形成されている。ここで、シリサイドプロテクション膜10は、SiC膜およびSiOC膜の少なくとも一方からなるものとする。

(もっと読む)

Fermi−FETのひずみシリコンとゲート技術

基板に形成されたひずみシリコンチャネルと、ひずみシリコンチャネルの両端に形成された、基板内のソース/ドレイン領域と、ひずみシリコンチャネルの上に形成されたゲート絶縁層と、ゲート絶縁層の上に形成されたゲートで構成される、電界効果トランジスタ。ひずみシリコンチャネルのドーピング量、基板のドーピング量、およびひずみシリコンチャネルの深さは、電界効果トランジスタのしきい値電圧において、ゲート絶縁層およびひずみシリコンチャネルの表面で、垂直電界がほぼゼロに等しくなるように設計されている。さらに、ゲートは、仕事関数がシリコンのバンドギャップの半分に近い値になるように設計されている。上記のように、本発明は、ひずみシリコンチャネルと、バンドギャップの半分の仕事関数を持つゲート層を有するフェルミFETを提供するものである。エピタキシャル成長法を利用した関連する形成方法についても説明している。  (もっと読む)

(もっと読む)

半導体装置

【課題】 LD構造の電解効果トランジスタを有する半導体装置において、ドレイン電流特性に優れた半導体装置を実現する。

【解決手段】 半導体基板の主面に形成された電界効果トランジスタと、膜応力によって前記電界効果トランジスタのチャネル形成領域に応力を発生させる絶縁膜とを有する半導体装置であって、

前記電界効果トランジスタのドレイン領域は、前記電界効果トランジスタのゲート電極から離間して前記半導体基板の主面に設けられた第1の半導体領域と、前記ゲート電極と前記第1の半導体領域との間の前記半導体基板の主面に前記第1の半導体領域と接して設けられ、前記第1の半導体領域よりも低不純物濃度で形成された第2の半導体領域とを有し、

前記絶縁膜は、前記ゲート電極を内包し、前記第2の半導体領域の一部を覆うようにして形成されている。

(もっと読む)

半導体装置

【課題】オン抵抗を増大させず、寄生NPNトランジスタをオンさせることなく、ホットキャリアに対する信頼性も向上させて半導体装置の安定動作を確保する。

【解決手段】半導体装置は、半導体基板1上に不純物濃度を変えて選択的に形成された第2導電型層2,11,16と、この第2導電型層の上に形成された第1導電型ソース領域3と、第2導電型層の上にソース領域3と離間して形成された第1導電型ドレイン領域4と、第1導電型ソース領域3とドレイン領域4の間に絶縁膜5を介して形成されたゲート電極6と、ソース領域3に隣接して形成された第2導電型コンタクト層7と、を備えると共に、ドレイン領域4側の前記第2導電型層の領域14よりもソース領域側の前記第2導電型層の領域13の方が高濃度であることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 接合リーク電流の増加を防止し、ゲート電極の層抵抗を低減可能な半導体装置の製造方法を提供する。

【解決手段】 高融点金属を材料に含むゲート電極を有する半導体装置の製造方法であって、ゲート電極を形成した後、露出したゲート電極の側面を覆うための酸化膜を形成するために所定の温度で酸化する初期酸化を行うステップと、初期酸化の後、初期酸化よりも高温で酸化する追加酸化を行うステップとを有するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】 高い密着性と拡散防止性とを備えたバリアメタルを有する半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 基体の上に、シリコンを含有する材料からなる第1の層を形成する工程と、前記第1の層の上に、金属と窒素とを含有する第2の層を形成する工程と、前記第2の層を、還元性ガスを含有する雰囲気のプラズマから得られる活性種に晒す工程と、を備えたことを特徴とする半導体装置の製造方法を提供する。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】 後続するコンタクト・ホール工程で使用される層間絶縁(ILD)エッチング停止層を有する高電圧用トランジスタ・デバイスを提供する。

【解決手段】 エッチング停止層は、10Ω−cmより大きい抵抗を有する高抵抗膜である。この結果、ゲート部において5Vより大きい高電圧を駆動する場合のリークを防止し、破壊電圧は向上する。高電圧用デバイスの製造方法は、現在の低電圧デバイスの製造工程と中電圧デバイスの製造工程と混載可能である。

(もっと読む)

半導体装置

【課題】半導体装置の放熱性を向上させ、素子で生じた熱が特定の回路に伝達され難くする。

【解決手段】半導体装置は、第1素子分離絶縁膜41と、それにより熱伝導率の低い第2素子分離絶縁膜42とを備えている。熱の伝達を抑制したいMOSトランジスタT1とMOSトランジスタT2との間には、熱伝導率の低い第2素子分離絶縁膜42を配設し、それ以外の素子間には第1素子分離絶縁膜41を配設する。

(もっと読む)

半導体装置およびその製造方法

【課題】 斜めイオン注入工程でイオン注入できない影領域を安定して低減させ、微細化に好適な構造を有する半導体装置およびその製造方法を提供する。

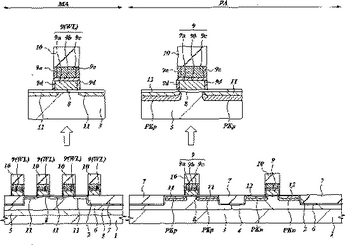

【解決手段】 p型ウェル領域12を第1および第2領域に区画するように絶縁分離層13を形成する工程と、絶縁分離層13と離間して第1領域12aに設けられた第1ゲート電極16と、絶縁分離層13と第2領域12bとに跨がり、且つ第1ゲート電極16と相対向する第2ゲート電極17とを同時に形成する工程と、第2ゲート電極17の一端をマスクとして垂直方向より所定角度傾けた方向からp型不純物イオンを第1領域12aに注入し、更に垂直方向よりn型不純物イオンを注入してソース/ドレイン領域19、20を形成する工程と、第2ゲート電極17の他端をマスクとして第2領域12bにウェルコンタクト層21を形成する工程を有している。

(もっと読む)

パワーMOSFET

集積半導体デバイスまたは個別部品上の領域を相互接続するシステムである。第1接続層は、複数の第1および第2の領域を相互接続する第1および第2ランナを有する。第2接続層は、第1ランナを相互接続する第3ランナと第2ランナを相互接続する第4ランナとを有する。第3接続層は、第3ランナに接続される第1パッドと第4ランナに接続される第2パッドとを有する。第1および第2パッドにおいてはんだバンプを使用することにより、パッドを他の回路と接続する。 (もっと読む)

延伸スペーサを利用した半導体デバイスおよびその形成方法

【課題】延伸スペーサを利用した半導体デバイスおよびその形成方法を提供する。

【解決手段】半導体デバイスは、半導体基板110を覆うゲートと、ゲートの側壁上にある誘電体ライナー150とを含む。この半導体デバイスは、誘電体ライナー150に隣接して誘電体ライナー150を越えるように半導体基板110に沿って横向きに延伸された延伸スペーサ170を含む。半導体デバイスは、半導体基板110の上面の下方に位置し、ゲート下のチャネル領域145に隣接するソース/ドレインをさらに含む。ソース/ドレインは、誘電体ライナー150および延伸スペーサ170下で延伸される。半導体デバイスは、ソース/ドレインの一部上を覆い、半導体基板110に沿って横向きに延伸するシリサイド領域190をさらに含む。従って、延伸スペーサ170はソース/ドレインの一部上において誘電体ライナー150とシリサイド領域190との間に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 キャリアトラップの少ない、かつ信頼性の高い高誘電率ゲート絶縁膜を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置は、半導体基板上に核形成のための絶縁膜を介して高誘電体膜によるゲート絶縁膜が形成され、絶縁膜又は/及び高誘電体膜が超臨界二酸化炭素中で処理された膜で形成されて成る。

高誘電体材料を用いて形成されたゲート絶縁膜を有する半導体装置の製造方法であって、半導体基板上に核形成のための絶縁膜を形成を形成し、この絶縁膜上に高誘電体膜を形成し、絶縁膜又は/及び高誘電体膜を超臨界二酸化炭素中で処理する工程を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 高誘電率膜を含むゲート絶縁膜を有するMISトランジスタを有する半導体装置及びその製造方法に関し、ポリシリコンの異常成長やゲートリーク電流を抑制しうる半導体装置の構造及びその製造方法を提供する。

【解決手段】 半導体基板10に形成され、ハフニウム組成xが0.7<x<1であるHfxAl1−xOyよりなる誘電体膜16と、誘電体膜16上に形成され、誘電体膜16とは異なる誘電体膜18とを有するゲート絶縁膜20と、ゲート絶縁膜20上に形成され、ポリシリコン膜を有するゲート電極24とを有する。これにより、ポリシリコン膜の形成過程における局所的な異常成長が防止される。また、ゲートリーク電流を大幅に低減することができる。

(もっと読む)

半導体集積回路の製造方法および半導体集積回路

【課題】高ゲート電圧時においても低ゲート電圧時においても高い動作時耐圧を有する高耐圧MOSトランジスタを備えた半導体集積回路を低コストで製造する方法を提供する。

【解決手段】

ディープグレード領域内にゲート端から離れて高濃度ドレイン領域が形成された高耐圧MOSトランジスタを製造するにおいて、ゲート絶縁膜を、ゲート電極形成予定領域の外部の少なくとも一部において除去することによって形成された開口部に、ゲート絶縁膜を透過しないエネルギーで不純物を注入して、シャローグレード領域を形成する。

(もっと読む)

水素化ホウ素クラスターイオンの注入によるイオン注入装置及び半導体製造方法

【課題】 イオン化水素化ホウ素分子から形成されたイオンビームの注入によってP型ドーピングが達成される半導体製造法を提供する。

【解決手段】 イオン化された水素化ホウ素分子クラスターがP型トランジスタ構造を形成するために注入される、イオン注入装置及び半導体素子を製造する方法。例えば、相補型金属酸化膜半導体(CMOS)素子の製造において、このクラスターは、ソース及びドレーン構造及びポリゲートに対してP型ドーピングを提供するために注入され、これらのドーピング段階は、PMOSトランジスタの形成に極めて重要である。分子クラスターイオンは、化学形態BnHx+及びBnHx-を有し、ここで、10<n<100及び0≦x≦n+4である。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 MOSトランジスタのLDD(Lightly−Doped Drain)形成工程において、サイドウォールスペーサを半導体基板の削れなく形成する。

【解決手段】 半導体基板100上にゲート絶縁膜101を介してゲート電極102を形成する工程と、ゲート電極102を被覆するようにSiCwHxOyNz(w>0、x≧0、y>0、z≧0)で表される有機無機ハイブリッド膜106を堆積する工程と、有機無機ハイブリッド膜106の所定部分を酸化層108に変換する工程と、酸化層108を選択的に除去して、ゲート電極102の側壁に有機無機ハイブリッド膜からなるサイドウォールスペーサ109を形成する工程を含む。

(もっと読む)

半導体集積回路装置およびその製造方法

ポリメタルゲートを構成する高融点金属膜の洗浄工程における欠けを防止し、装置の特性を向上させ、また、洗浄効率を向上させるため、基板1上の低抵抗多結晶シリコン膜9a、WN膜9bおよびW膜9cを、窒化シリコン膜10をマスクにドライエッチングし、これらの膜よりなるゲート電極9を形成し、ウエットハイドロゲン酸化により薄い酸化膜9dを形成した後、RPN法を用いて窒化処理を行い、ゲート電極の側壁から露出したW膜9cをWN膜9eとする。その結果、その後の洗浄工程、例えば、n−型半導体領域11やp−型半導体領域12の形成時に行われる、1)レジスト膜のホトリソグラフィー工程、2)不純物の注入工程、3)レジスト膜の除去工程および4)基板表面の洗浄工程が繰り返し行われても、W膜9cの欠けを防止でき、また、洗浄液としてU洗浄液やフッ酸系の洗浄液のような強い洗浄液を用いることができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】高周波電力増幅用電界効果型半導体装置において、耐圧を確保しながらの小型化と高効率化の両立が困難になる。

【解決手段】高周波電力増幅用出力段LDMOSに、歪Siチャネルを用いることで更なる効率向上を実現する。更に、チャネル領域を有する歪Si層の膜厚、欠陥の不活性化、或いはフィールドプレート構造の最適化などによってリーク電流を低減しつつ最大限に効率を高める。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、シリサイドプロセスを適用したMOSFETにおいて、シリサイド膜をより大きく形成できるようにする。

【解決手段】たとえば、シリコン基板11の表面上に設けられたゲート電極16の側面には、それぞれ、内側ゲート側壁膜18および外側ゲート側壁膜21が形成されている。一方、ゲート電極16の形成位置を除く、シリコン基板11の表面部には、浅い低濃度拡散層17、および、二段構造の浅い高濃度拡散層19と深い高濃度拡散層22とが形成されている。そして、浅い高濃度拡散層19および深い高濃度拡散層22に対応するシリコン基板11の表面部には、それぞれの高濃度拡散層19,22の深さに応じて厚さの異なる二段構造のシリサイド膜23が形成されている。

(もっと読む)

961 - 980 / 1,105

[ Back to top ]