Fターム[5F140BH15]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054) | LDD(Lightly doped dorain−source) (1,105)

Fターム[5F140BH15]に分類される特許

1,021 - 1,040 / 1,105

半導体デバイス及び同デバイスを形成する方法

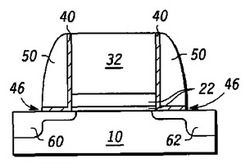

MOSFETの製造において、MOSFETに関する幾つかの構造的目的を果たす再酸化段階を提供することが知られている。しかしながら、より小型の集積回路用のドライブを収容するMOSFETのゲート絶縁層用の高誘電率材料を提供する必要性によって、ゲート絶縁層と基板との間のSiO2界面層の過剰な成長をもたらした。SiO2層の過剰成長は、MOSFET内の漏れ電流の増大につながる酸化膜換算膜厚(EOT)を生じる。更に電極としてポリシリコンを金属と置き換えることは、処理中の酸素曝露を妨げる。結果として、本発明は、MOSFETのゲート電極(32)の少なくとも側壁(34)を覆う酸素障壁層(40)の堆積段階と再酸化段階とを置き換え又は先行して行うことで、誘電界面及び金属ゲート電極への酸素拡散のための障壁を形成し、EOTの増大を防ぎ金属ゲート電極の完全性を保持する。 (もっと読む)

電界効果トランジスタ

【課題】 基板バイアス電圧を印加することなく、正確且つ確実な低温動作を実現する構成を有する電界効果トランジスタを提供する。

【解決手段】 本発明の実施の一形態に係る電界効果トランジスタは、300K以下の温度条件で動作することが想定された電界効果トランジスタであって、4.05未満の仕事関数WFnを有するゲート電極材により形成されたゲート電極を備えているnチャネル電界効果トランジスタを含むものである。また、本発明の実施の一形態に係る電界効果トランジスタは、5.17を超える仕事関数WFpを有するゲート電極材により形成されたゲート電極を備えているpチャネル電界効果トランジスタを含み得るものである。

(もっと読む)

半導体装置の製造方法並びにそのような方法で得られる半導体装置

この発明は、半導体材料の半導体本体(1)が設けられ、該半導体本体表面にソース領域(2)及びドレイン領域(3)を有し、ソース領域(2)とドレイン領域(3)との間にゲート領域(4)を有し、ゲート領域(4)は、ゲート誘電体(5)によって半導体本体(1)の表面から分離されているさらなる半導体材料の半導体領域(4A)を備え、ゲート領域(4)近傍にソース領域(2)とドレイン領域(3)とを形成する複数のスペーサ(6)を有し、ソース領域(2)とドレイン領域(3)とに金属と半導体材料との化合物(8)を形成するための金属層(7)が設けられ、そして、ドレイン領域(3)に金属と上記さらなる半導体材料との化合物(8)を形成するためのさらなる金属層(7)が設けられる電界効果型トランジスタを有する半導体装置の製造方法に関する。ソース、ドレイン、ゲート領域(2,3,4)をシリサイド化するのに異なる金属層が用いられる既知の方法は様々な欠点がある。本発明の方法は、複数のスペーサ(8)が形成される前に、半導体領域(4A)に対して選択的にエッチングされうる材料の犠牲領域(4B)が半導体領域(4A)の上部に堆積され、複数のスペーサ(6)が形成された後に、エッチングにより犠牲領域(4B)が除去され、犠牲領域(4B)が除去された後に、ソース、ドレイン、ゲート領域(2,3,4)を含む単一の金属層(7)が堆積されることを特徴する。この方法では、一方で、単一の金属層のみと小数の容易な工程とが必要で、そして、現存する(シリコン)技術と適合し、他方で、完全にシリサイド化されたゲート(4)において空乏層の影響を受けない(MOS)FETが得られる。  (もっと読む)

(もっと読む)

MIS型FETの製造方法

【課題】 ダマシン構造のゲート電極を備えたMIS型FETにおいて、高い電流駆動能力と低消費電力とを有するMIS型FETの製造方法を提供する。

【解決手段】 シリコン基板1の表面部にソース/ドレイン拡散層(14,15)を形成し、その表面にシリサイド層17を形成する。そして、ゲート側壁(12,13)で区画されたゲート開口溝20底部のシリコン基板1表面に、550℃以下の温度で界面層21を形成し、ゲート開口溝20内、界面層21および層間絶縁膜19を被覆するようにHigh−k膜22を堆積させ、酸化性雰囲気中550℃以下の温度での熱処理を施す。そして、全面を被覆する導電体膜23およびメタル膜24を形成した後、CMP法により層間絶縁膜19上の不要部分を研磨除去しダマシン構造のメタルゲート電極を備えたMIS型FETを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイド技術を用いた半導体装置では、低コストかつ短工程でMIS型トランジスタのゲート電極と拡散領域との短絡を防ぐことが困難であった。

【解決手段】ゲート部とソース・ドレイン部とを有する半導体素子であって、ゲート部は、ゲート電極の側部にサイドウォールを備える。サイドウォールの上端部がゲート電極の上端部よりも高く形成しており、サイドウォールのゲート電極に接する面は、ゲート電極上面に対してほぼ直角である。サリサイド技術を用いても、ゲート電極上に形成されたチタンと、サイドウォールおよびソース・ドレイン部上に形成されたチタンとは離間した状態となっており、シリサイドによるゲート電極とその他の部分との短絡を防止する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 パンチスルー現象を抑えた半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法が、シリコン基板を準備する工程と、シリコン基板に、ゲート電極と、ゲート電極の両側に配置されるソース領域およびドレイン領域を形成し、ソース領域とドレイン領域で挟まれた領域をチャネル領域とするチャネル領域形成工程と、ソース領域とドレイン領域を覆う金属膜を形成する金属膜形成工程と、金属膜と、ソース領域およびドレイン領域とを反応させ、ソース領域およびドレイン領域の表面に金属シリサイド層を形成するシリサイド工程と、金属シリサイド層をイオン注入マスクに用いてチャネル領域にイオンを注入し、ソース領域およびドレイン領域とは導電型の異なるパンチスルーストッパ領域を、ソース領域およびドレイン領域に隣接するように形成する注入工程とを含む。

(もっと読む)

半導体装置

【課題】エンハンスメント型のMOS構造を有する半導体装置において、大きなリーク電流を発生させないようにする。

【解決手段】エンハンスメント型トランジスタにおいて、ゲート電極13下のチャネル領域に形成される高濃度P領域17を、ソース領域15bに接し、ドレイン領域15aに接しないようにする。このことによって、ドレイン領域15aと高濃度P領域17間のPN接合がなくなり、リーク電流を低減することができる。また、ドレイン領域15aと高濃度P領域17との距離は、ドレイン領域15aに動作電圧が印可されたときに拡がる空乏層が、高濃度P領域17の内部に拡がったとしても、空乏層内部の電界がアバランシェ降伏あるいはツェナー降伏を発生させる臨界電界に達しないような距離とする。これによりアバランシェ降伏あるいはツェナー降伏によるリーク電流の増大を抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能を向上させる。

【解決手段】 LDMOSFETのゲート電極30およびn+型ソース領域53上にサリサイド工程により金属シリサイド膜64を形成し、n-型オフセットドレイン領域33、n型オフセットドレイン領域51およびn+型ドレイン領域52上にはこの金属シリサイド膜を形成しない。ゲート電極30のドレイン側の側壁上には、絶縁膜を介して、シリコン膜からなるサイドウォールスペーサが形成され、このサイドウォールスペーサによりフィールドプレート電極44が形成される。フィールドプレート電極44はゲート電極30上に延在しておらず、サリサイド工程ではゲート電極30の上面の全面に金属シリサイド膜64が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】従来の2層構造のサイドウォールスペーサとLDD構造のソース・ドレイン領域とサリサイド構造とを有するMIS型半導体装置は、ソース・ドレイン領域にてリーク電流が発生するという課題があった。

【解決手段】第1サイドウォールスペーサと第2サイドウォールスペーサとを備えるサイドウォール構造のゲート電極と、第1拡散領域と第2拡散領域とを備えるLDD構造のソース・ドレイン領域と、サリサイド構造とを有するMIS型半導体装置であって、MIS型半導体装置は半導体基板に形成する素子領域を設け、素子領域の周囲を囲むようにフィールド酸化膜を有し、素子領域とフィールド酸化膜との境界領域に、第1拡散領域もしくは第2拡散領域と接続する第3拡散領域を有する。

(もっと読む)

半導体装置の製造方法

【課題】 短波長光の照射による活性化により、浅接合の拡散層を形成する際の、ゲート絶縁膜中のトラップの発生を抑える。

【解決手段】 半導体装置の製造において、まず、基板に、ゲート絶縁膜を介して、ゲート電極を形成する。少なくともゲート電極をマスクとして、不純物を注入し、拡散層を形成する。また、この拡散層形成のための不純物注入の前又は後に、少なくともゲート電極をマスクとして、フッ素イオンを注入する。更に、波長約1000nm以下の光を、約1ミリ秒以内の時間照射する。

(もっと読む)

絶縁ゲート型電界効果トランジスタの製法

【課題】微細なゲート電極を有するLDD(Lightly Doped Drain)構造の絶縁ゲート型電界効果トランジスタを製造する方法において、製造歩留りを向上させる。

【解決手段】P型ウェル領域14の表面に素子孔を有するフィールド絶縁膜16を形成した後、素子孔内の半導体表面にゲート絶縁膜20を形成する。絶縁膜20の上に破線で示すようにポリシリコン等のゲート電極層24を形成した後、電極層24及び絶縁膜20の積層と絶縁膜16とをマスクとするイオン注入処理によりN+型ソース領域28及びN+型ドレイン領域30を形成する。等方性エッチング処理により電極層24を実線で示すように細く且つ薄くした後、電極層24及び絶縁膜20の積層と絶縁膜16とをマスクとするイオン注入処理によりN−型ソース領域32及びN−型ドレイン領域34を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 プラズマ処理によりシリコン表面に形成される、SiCを含む変質層を、シリコン表面の侵食を最小限に抑止しながら除去する。

【解決手段】 前記変質層を、酸素ラジカルに、前記半導体表面のSi原子に結合してSi原子と酸素原子との間の二重結合の形成を阻害するような元素の活性種を添加して改質し、形成された改質層をウェットエッチングにより除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜における絶縁耐圧を改善して、信頼性の高い半導体装置を提供する。

【解決手段】第1半導体層42の上に形成された第2半導体層44と、第1半導体層42から電気的に絶縁されたゲート電極53と、ソース電極51およびドレイン電極55と、ゲート絶縁膜49と、少なくとも一部が第1導電型のウェル領域45の内部に形成され、ソース電極51に電気的に接触する第2導電型のソース領域47と、ドリフト領域43とを備え、第2半導体層44における所定の領域は、第2導電型層を含む蓄積チャネル領域であり、ウェル領域45の内部に形成され、かつ、ソース領域47と接する補助ソース領域48をさらに有し、ソース領域47はゲート電極53によってオーバーラップされておらず、補助ソース領域48の一部はゲート電極53によってオーバーラップされており、補助ソース領域48の総ドーズ量は、ソース領域47の総ドーズ量よりも少ない。

(もっと読む)

ボイドのないゲート電極を具備したトランジスタの製造方法

【課題】 ボイドのないゲート電極を具備したトランジスタの製造方法を提供する。

【解決手段】 半導体基板上にゲート酸化膜を形成した後、前記ゲート酸化膜の上部にゲート電極用ポリシリコン膜を蒸着する。次いで、前記ポリシリコン膜にp型不純物をイオン注入し、前記ポリシリコン膜の所定厚さほどを化学機械的研磨方法で除去する。

(もっと読む)

分離ウェルを用いるMOSバラクタ

【課題】 向上した調節能力と高い品質係数Qとを有するバラクタ及びその製造方法を提供すること。

【解決手段】 本発明は、向上した調節能力と高い品質係数Qとを有するバラクタ22、及び、バラクタ22を製造する方法を提供する。本発明の方法は、従来のCMOS処理スキーム又はBiCMOS処理スキームに組み込むことができる。この方法は、第1の導電型の半導体基板12と、該基板12の上部領域11の下方に配置された、第2の導電型のサブコレクタ14又は分離ウェル(すなわち、ドープ領域)とを含む構造体であって、該第1の導電型は、第2の導電型とは異なる構造体を準備するステップを含む。次に、複数の分離領域16が、基板12の上部領域11内に形成され、次いで、ウェル領域が、基板12の上部領域11内に形成される。場合によっては、本発明のプロセスのこの時点で、ドープ領域14が形成される。ウェル領域は、第2の導電型の外側ウェル領域20A及び20Cと、第1の導電型の内側ウェル領域20Bとを含む。ウェル領域の各々のウェルは、分離領域16によって上面で分離される。次に、内側ウェル領域20Bの上方に、少なくとも第1の導電型のゲート導体26を有する電界効果トランジスタが形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリサイド膜を有する半導体装置において配線抵抗を低減し、また配線抵抗のばらつきを低減する。

【解決手段】 コバルトシリサイドあるいはニッケルシリサイドを使う超高速半導体装置において、シリサイド膜形成のためシリコン表面に金属膜を堆積する前に、シリコン表面から自然酸化膜をウェットエッチングプロセスで除去した後、化学酸化膜を形成する。

(もっと読む)

半導体装置

【課題】直接トンネル電流が流れる程度に薄膜化されたゲート絶縁膜におけるゲート電極からのドーパント原子の基板への拡散を防止すると共に、ゲートリーク電流を低減できるようにする。

【解決手段】第1の素子形成領域51及び第2の素子形成領域52に区画された半導体基板11上に、酸化膜からなる第1のゲート絶縁膜13Aを形成する。次に、第1のゲート絶縁膜13Aの第2の素子形成領域52に含まれる部分を除去し、半導体基板11に対して酸窒化性雰囲気で熱処理を行なうことにより、第2の素子形成領域52上に膜厚が第1のゲート絶縁膜13Aよりも小さい酸窒化膜からなる第2のゲート絶縁膜15Bを形成する。次に、第1のゲート絶縁膜13B及び第2のゲート絶縁膜15Bを窒素プラズマに暴露することにより、窒素原子をさらに導入された第1のゲート絶縁膜13C及び第2のゲート絶縁膜15Cを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】サイドウォールの応力によってキャリア移動度を高めることにより、CMOSトランジスタの高速化を図る半導体装置及びその製造方法を提供する。

【解決手段】NMISトランジスタのゲート電極14a及びPMISトランジスタのゲート電極14bの側面上に、引張応力を有する第1のサイドウォール16a、16bを形成する。その後、基板上の全面に、圧縮応力を有する圧縮応力含有絶縁膜17を形成する。その後、レジスト18をマスクにして、圧縮応力含有絶縁膜17を選択的にエッチングして、ゲート電極14bの側面上に、第2のサイドウォール17aを形成する。その後、第2のサイドウォール17aを覆うレジスト19をマスクにして、圧縮応力含有絶縁膜17を除去する。その後、半導体基板11上の全面に、実質的に応力が生じない層間絶縁膜21を形成する。

(もっと読む)

極浅接合の形成方法

【課題】 極浅接合を形成する方法を提供する。

【解決手段】 p型素子に極浅接合を形成する方法は、アルミニウムイオンをn型にドープされたシリコンに打ち込み、続いてアルミニウムを活性化させ、かつ拡散させるために低温アニーリングを行う。アルミニウムを使用することによりホウ素を使用した場合に比べ、より浅い接合を形成することができる、抵抗が低くなる、より低温でのアニーリングが可能となるといった様々な利点が生まれる。

(もっと読む)

相補型金属−酸化膜−半導体電界効果トランジスタ構造

相補型金属−酸化膜−半導体電界効果トランジスタ構造(100)はイオン注入領域(126,128)を2つの相補型素子の内の一方のみに含む。トランジスタ構造(100)は通常、化合物半導体基板(102)と、そしてエピタキシャル層構造(104)と、を含み、エピタキシャル層構造は、エピタキシャル層構造の導電型を決定する一つ以上のドナー層を含む。イオン注入領域は、これらの相補型素子の内の一方に位置するエピタキシャル層構造(104)の導電型を「反転する」または「逆にする」ように作用する。例示として実施形態では、p型アクセプターをドープしたイオン注入領域がpチャネル素子(122)において使用され、nチャネル素子(120)はイオン注入されない状態のままである。  (もっと読む)

(もっと読む)

1,021 - 1,040 / 1,105

[ Back to top ]