Fターム[5F140BH15]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054) | LDD(Lightly doped dorain−source) (1,105)

Fターム[5F140BH15]に分類される特許

1,001 - 1,020 / 1,105

半導体装置および半導体装置の製造方法

【課題】 トランジスタの信頼性の劣化を抑制しつつ、高電圧駆動を可能とするとともに高速化を図る。

【解決手段】 酸化防止膜4をマスクとしてエピタキシャル成長を行うことにより、第1単結晶半導体層3上に第2単結晶半導体層5を形成し、酸化防止膜4をマスクとして第2単結晶半導体層5の熱処理を行うことにより、第2単結晶半導体層5の構成成分を第1単結晶半導体層3内に拡散させ、第1単結晶半導体層3の一部を第3単結晶半導体層7に変換した後、第1単結晶半導体層3上および第3単結晶半導体層7上に第4単結晶半導体層8を形成し、第3単結晶半導体層7上に配置された第4単結晶半導体層8上にゲート絶縁膜11を形成するとともに、オフセットゲート層15bおよびドレイン層15cを第1単結晶半導体層3および第4単結晶半導体層8に形成する。

(もっと読む)

半導体装置及びその製造方法

【目的】 STI構造の素子分離領域3の近傍のアクティブ領域2に発生する応力発生領域4の転位等の結晶欠陥の発生を抑制し、さらにアニール処理がなくてもソース/ドレインを形成することができる半導体装置及びその製造方法を提供する。

【解決手段】 マスク形成工程で少なくとも素子分離領域3とアクティブ領域2との境界の応力発生領域4上にマスクを形成し、第1イオン注入工程で第1のイオン11をイオン注入し、応力発生領域4以外のアクティブ領域2にソース部8及びドレイン部9となる第1の不純物領域12を形成する。次に、第2イオン注入工程で応力発生領域4を含むアクティブ領域2に第1の不純物イオン11よりも質量が小さく、かつ、極性が同じである第2のイオン14をイオン注入して第2の不純物領域15を形成する。

(もっと読む)

エンハンスメントモード金属酸化膜半導体電界効果トランジスタ及びその形成方法

注入フリーエンハンスメントモード金属酸化膜半導体電界効果トランジスタ(EMOSFET)を提供する。EMOSFETは、III−V化合物半導体基板と、III−V化合物半導体基板上のエピタキシャル層構造とを有する。エピタキシャル材料層は、チャネル層と、少なくとも1つのドープ層とを有する。ゲート酸化膜層は、エピタキシャル層構造の上にある。EMOSFETは、更に、ゲート酸化膜層上の金属ゲート電極と、エピタキシャル層構造上のソース及びドレイン・オーミックコンタクトと、を含む。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】正孔または電子の移動度を高めるとともに、NMOS領域とPMOS領域との表面の段差を抑制することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明は、NMOS領域AとPMOS領域Bとを同一の基板11に備えた半導体装置であって、NMOS領域Aの基板11上に設けられるとともに、基板11の表面と異なる面方位を有する歪みSi層21と、PMOS領域Bの基板11上に設けられるとともに、基板11の表面と同じ面方位を有する歪み層からなる歪みSiGe層31とを備えたことを特徴とする半導体装置およびその製造方法である。

(もっと読む)

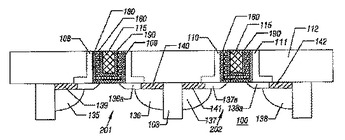

LDMOSトランジスタを含む半導体装置

【課題】 LDMOSトランジスタを高耐圧にするとともに、オン抵抗を低減させる。

【解決手段】 半導体装置100は、P型シリコン基板102と、P型シリコン基板102上に形成されたゲート電極120と、ゲート電極120の横方向に形成されたドレイン(第二N型拡散領域109)と、ドレイン(第二N型拡散領域109)上に形成されたドレイン電極130と、ゲート電極120とドレイン電極130との間に設けられ、ゲート絶縁膜112よりも膜厚の厚い絶縁膜(フィールド酸化膜106)と、前記絶縁膜上において、ドレイン電極130に沿って形成された電界制御電極118と、により構成されたLDMOSトランジスタを含む。

(もっと読む)

半導体素子及びその製造方法

【課題】 チャネル領域内のキャリア制御性が優れると共にリーク電流が少ない半導体素子及びその製造方法を提供する。

【解決手段】 基板1上に、エピタキシャル成長により、基板1の表面に対して垂直な方向を含む断面が下底よりも上底が短い台形形状である低濃度ドープダイヤモンド層4を形成する。次に、低濃度ドープダイヤモンド層4の両側に、エピタキシャル成長により低濃度ドープダイヤモンド層4よりも不純物濃度が高い高濃度ドープダイヤモンド層7a及び7bを形成する。そして、高濃度ドープダイヤモンド層7a及び7b上に、金属電極8a及び8bを形成した後、酸化シリコン絶縁層9a及び9bを形成し、更に、低濃度ドープダイヤモンド層4の上に酸化アルミニウム絶縁層10を介してゲート電極11を形成して、高濃度ドープダイヤモンド層7a及び7b間の距離が基板1から遠ざかるに従い短くなる半導体素子とする。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたCMOS半導体装置に適したpMOSとnMOSにおいてそれぞれ適切に制御されたGe濃度分布及び形状を有するSi/SiGeゲート電極構造を備えた半導体装置を提供することである。

【解決手段】上記の課題を解決した半導体装置は、半導体基板上に形成された絶縁膜と、前記絶縁膜上に形成され、前記絶縁膜との界面近くで高いゲルマニウム濃度を有し、その反対側表面で低いゲルマニウム濃度を有する第1のゲート電極と、前記絶縁膜上に形成され、電極中でほぼ一様なゲルマニウム濃度を有し、6×1020atoms/cm3以上の濃度のn型不純物を有する第2のゲート電極とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】

5〜10V程度のスナップバック耐圧をもつデバイスをセルフアライン法で実現することができる半導体装置及びその製造方法を提供すること。

【解決手段】

主ゲート6aの隣に所定の間隔をおいて配された2個以上の副ゲート6b、6cと、副ゲート6b、6cの下であってソース/ドレイン層9a、9bの端部から主ゲート6aの端部近傍まで連続的に配されるとともに、ソース/ドレイン層9a、9bと同電位型であり、不純物の濃度がソース/ドレイン層9a、9bよりも低濃度である低濃度層7a、7bと、を備える。

(もっと読む)

ゲート構造及び該構造を作る方法

【課題】完全なシリサイドゲートを伴うMOSトランジスタの新規構造を得ることである。

【解決手段】本発明は、MOSトランジスタに関し、そのゲートは絶縁層(31)、金属シリサイド層(50)、導電性封入材料層(53)、及びポリシリコン層(55)を連続的に含む。

(もっと読む)

トレンチ拡散領域を有する金属酸化物半導体デバイスおよびその形成方法

【課題】改善された高周波性能およびオン状態特性を可能にするMOSデバイスを提供すること。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

(もっと読む)

半導体装置及びその製造方法

【課題】表面濃度が濃く且つ急峻な不純物濃度分布を有するチャネル拡散層を備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜11とゲート電極12が形成され、ゲート電極12の側面上にサイドウォール13が形成されている。そして、ゲート電極12の側方下にはP型エクステンション拡散層14が形成され、サイドウォール13の側方下にはP型ソース・ドレイン拡散層15が形成されている。ゲート絶縁膜11の下側の領域には、インジウムイオンが主な不純物である第1のP型チャネル拡散層16と、ボロンが主な不純物である第2のP型チャネル拡散層17が形成されている。そして、第1のP型チャネル拡散層16の底面側を覆うように、N型拡散層18が形成されている。

(もっと読む)

MOSトランジスタのシミュレーション方法

【課題】トランスコンダクタンスgm及びソースドレインコンダクタンスgdsの減衰を再現し、片側LDD構造を有する高耐圧MOSトランジスタのシミュレーション精度を向上する。

【解決手段】このMOSトランジスタモデルは、ドレイン側に、不変抵抗値を有する抵抗10がMOSトランジスタモデルMTに接続されたBISM3モデルに、さらにゲート電位VG及びドレイン電位VDに依存して抵抗値が変化する可変抵抗20を抵抗10に直列に接続したものである。即ち、可変抵抗20の抵抗値R20は、ゲート電位VG及びドレイン電位VDの関数であり、例えばそれらのパラメータの多項式(例えば、2次式や3次式)で表現される。そして、それらの多項式の各項の係数を実際のMOSトランジスタの電気的特性から抽出する。

(もっと読む)

半導体センシング用電界効果型トランジスタ及びこれを用いた半導体センシングデバイス

【解決手段】 シリコン上にゲート絶縁層が形成された半導体センシング用電界効果型トランジスタであり、該ゲート絶縁層上に、直接的な検出部として有機単分子膜を形成して用いる半導体センシングデバイス用の電界効果型トランジスタであって、上記ゲート絶縁層が、第1のシリコン酸化物層上にシリコン窒化物層を介して第2のシリコン酸化物層が積層されてなる積層構造を具備する半導体センシング用電界効果型トランジスタ及びこれを用いた半導体センシングデバイス。

【効果】 ゲート絶縁層からのトランジスタ部分への水分やイオンの侵入を遮断することが可能であり、液中測定用として特に好適な、高い検出感度を示す半導体センシングデバイス及びこれを与える電界効果型トランジスタを提供することができる。

(もっと読む)

半導体装置

【課題】金属原子を含んだ絶縁破壊耐性の高いゲート絶縁膜構造を持つ半導体装置とその製造方法を提供する。

【解決手段】p型シリコン基板1に、チャネル領域4を挟んで対向するドレイン、ソース拡散層3が形成され、ゲート絶縁膜5を介してゲート電極6が形成される。ゲート絶縁膜5は、チャネル領域4の直上の部分が誘電率の高い金属酸化物からなる第1のゲート絶縁膜5aにより形成され、それ以外の部分は金属原子濃度が低い第2のゲート絶縁膜5bにより形成される。

(もっと読む)

基板傾斜を用いた半導体ドーピング

【課題】半導体基板をドープする方法、特に、注入源に対する基板の傾斜角を変えることによってドーパントを注入する方法を提供する。

【解決手段】基板にドーパントを注入する方法、及びそのような注入を利用して半導体素子を製造する方法。ドーパントを注入する方法は、他の段階の中でもとりわけ、注入プラテン(305)上又はその上に位置する基板(310)を注入源(320)に対して第1の方向の軸線に関して傾斜させる段階と、第1の方向に傾斜した基板(310)を使用して注入線量の一部分を注入する段階と、次に、基板(310)を第1の方向と反対の第2の方向に傾斜させる段階と、第2の方向に傾斜した基板(310)を使用して注入線量の別の部分を注入する段階とを含む。

(もっと読む)

適応型負性微分抵抗デバイス

【課題】 単一のシリコンウェーハ中に形成した互いに異なる回路に多様な負性微分抵抗(NDR)特性を付与できるように製造工程中または出荷後のフィールドでの通常動作中に最大電流対最小電流比(PVR)値などの特性値を調整できるようにしたNDRデバイスを提供する。

【解決手段】 互いに異なるNDRモードを発現するように動作中に多様にNDR特性を変える過程を含むNDR素子の制御の方法を開示している。NDR素子(シリコン利用のNDR FETなど)に印加するバイアスの条件を変えることによって、最大電流対最小電流比(PVR)値(またはそれ以外の特性)をNDR素子利用回路の所望の動作変化の実現のために動的に変えることができる。例えば、メモリ用または論理回路用では、動作電力の削減のために最小電流値を休止期間中に小さくすることができる。すなわち、適応型NDR素子を慣用の半導体回路の中で有利に活用することができる。

(もっと読む)

イオン注入方法、並びに、これを用いた電界効果トランジスタの製造方法及び固体撮像素子の製造方法

【課題】 斜めイオン注入を行うにも拘わらず、電極等の導電膜下に注入されるイオンの量や注入位置のばらつきを低減する。

【解決手段】 p型のシリコン基板1上の全面にゲート酸化膜2を形成する。ゲート酸化膜2上にポリシリコン層を形成し、これをパターニングしてゲート電極3とする。イオン注入調整膜として、シリコン窒化膜114を、ゲート電極3を含むシリコン基板1の全面に形成する。シリコン窒化膜114は、ゲート電極3に側壁3aにも形成される。ゲート電極3をマスクとして、n型のイオンをシリコン基板1に対して斜め方向から注入して、第1のドレイン領域5を形成する。このとき、ゲート電極3の側壁3aに形成されたシリコン窒化膜4がイオンを抑制するため、ゲート電極3の側壁3aにはイオンが到達しない。よって、イオンがゲート電極3を突き抜けてシリコン基板1内に注入されることはない。

(もっと読む)

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

半導体デバイス及び同デバイスを形成する方法

MOSFETの製造において、MOSFETに関する幾つかの構造的目的を果たす再酸化段階を提供することが知られている。しかしながら、より小型の集積回路用のドライブを収容するMOSFETのゲート絶縁層用の高誘電率材料を提供する必要性によって、ゲート絶縁層と基板との間のSiO2界面層の過剰な成長をもたらした。SiO2層の過剰成長は、MOSFET内の漏れ電流の増大につながる酸化膜換算膜厚(EOT)を生じる。更に電極としてポリシリコンを金属と置き換えることは、処理中の酸素曝露を妨げる。結果として、本発明は、MOSFETのゲート電極(32)の少なくとも側壁(34)を覆う酸素障壁層(40)の堆積段階と再酸化段階とを置き換え又は先行して行うことで、誘電界面及び金属ゲート電極への酸素拡散のための障壁を形成し、EOTの増大を防ぎ金属ゲート電極の完全性を保持する。 (もっと読む)

電界効果トランジスタ

【課題】 基板バイアス電圧を印加することなく、正確且つ確実な低温動作を実現する構成を有する電界効果トランジスタを提供する。

【解決手段】 本発明の実施の一形態に係る電界効果トランジスタは、300K以下の温度条件で動作することが想定された電界効果トランジスタであって、4.05未満の仕事関数WFnを有するゲート電極材により形成されたゲート電極を備えているnチャネル電界効果トランジスタを含むものである。また、本発明の実施の一形態に係る電界効果トランジスタは、5.17を超える仕事関数WFpを有するゲート電極材により形成されたゲート電極を備えているpチャネル電界効果トランジスタを含み得るものである。

(もっと読む)

1,001 - 1,020 / 1,105

[ Back to top ]