Fターム[5F140BH15]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054) | LDD(Lightly doped dorain−source) (1,105)

Fターム[5F140BH15]に分類される特許

1,041 - 1,060 / 1,105

トランジスタ及びこれの製造方法

【課題】 超高集積度で、改善された構造の不純物領域を有する半導体装置のトランジスタを製造する方法を提供することである。

【解決手段】 本発明のトランジスタは、{100}面である第1表面、第1表面より低い高さを有する{100}面である第2表面、及び第1表面と第2表面との間を連結する{111}面である第3表面を有する半導体基板を含む。第1不純物領域が半導体基板の第2表面の下部に形成される。ゲート構造物が半導体基板の第1表面上に形成される。エピタキシャル層が半導体基板の第2表面及び第3表面上に形成される。第2不純物領域がゲート構造物の両側に形成される。

(もっと読む)

トランジスタ及びこれの製造方法

【課題】 超高集積を有して形成することができ、改善された構造の不純物領域を有する半導体装置のトランジスタ及びトランジスタを製造する方法が開示されている。

【解決手段】 超高集積を有して形成することができながら改善された構造の不純物領域を有する半導体装置のトランジスタにおいて、前記トランジスタは表面、表面より低い高さを有する{100}面である底面、及び表面と底面とを連結する{111}面である側面を有する半導体基板を含む。ゲート構造物が表面上に形成される。エピタキシャル層が底面と側面上に形成される。不純物領域がゲート構造物の両側に形成される。急なPN接合を形成することができるので、不純物領域の間で短チャンネル効果の発生を抑制することができる。

(もっと読む)

強化された遮蔽構造を備えた金属酸化膜半導体デバイス

【課題】強化された遮蔽構造を備えた金属酸化膜半導体(MOS)デバイスを提供すること。

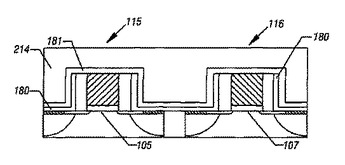

【解決手段】MOSデバイスは、基板上に形成された半導体層を含み、その基板は水平面とその水平面に垂直な方向の法線とを画定する。第1のソース/ドレイン領域および第2のソース/ドレイン領域が、半導体層内で、その上面近傍に形成され、第1のソース/ドレイン領域と第2のソース/ドレイン領域は互いに離隔されている。ゲートが、半導体層の上面近傍に形成され、少なくとも部分的には第1のソース/ドレイン領域と第2のソース/ドレイン領域との間に配置される。第1の誘電領域が、MOSデバイス内に形成され、半導体層の上面から下方に第1の距離まで半導体層の中へ延在するトレンチの境界を画定し、第1のソース/ドレイン領域と第2のソース/ドレイン領域との間に形成されている。

(もっと読む)

セルフバイアストランジスタ構造およびSRAMセル

自己バイアス半導体スイッチを供給することで、個々のアクティブコンポーネント数を減らしたSRAMセル(450)を実現することができる。特定の実施形態では、自己バイアス半導体デバイスを、ダブルチャネル電界効果トランジスタ(400)の形式で与えることができる。このトランジスタは、トランジスタ数が6つ未満の、また、好ましい実施形態では、わずか2つの個々のトランジスタ素子を備えたSRAMセル(450)の形成を可能にする。  (もっと読む)

(もっと読む)

高性能なサブ0.1マイクロメートルトランジスタ用のソース/ドレイン構造

【課題】チャネルパンチスルーおよび短チャネル効果が低減された、高性能な短チャネル長のトランジスタ構造を提供すること。

【解決手段】本発明によるトランジスタ構造(10)は、基板内に形成されたp型ウェル12を備える。ゲート構造(14)は、ソース領域(18)とドレイン領域(20)との間に挿入されたチャネル領域(16)上に形成される。ゲート構造(14)は、ゲート誘電体24上にゲート電極(22)と、ゲート(22)の面に沿った側壁26を有する。ソース領域(18)は、n型の低濃度ドープ領域(32)と、n+領域34とを有するが、ソースhalo領域は有しない。ドレイン領域(20)は、n型の低濃度ドープ領域42と、n+領域44と、p型ドレインhalo領域(50)とを有する。ドレインhalo領域(50)は、ドレイン領域にイオンを斜めに注入することにより形成された、ドープ領域である。

(もっと読む)

非対称なヘテロドープされた高電圧のMOSFET(AH2MOS)

非対称なヘテロドープされた金属酸化物(AH2MOS)半導体デバイスは基板と、前記基板の頂部にあってソース領域とドレイン領域との間に配置された絶縁ゲートと、からなる。ゲートの一方の側面には、ヘテロドープされたタブ及びソース領域が形成されている。タブ領域は第2極性のドーパントを有している。ソース領域が各タブ領域内に配置されており、第2極性と反対の第1極性のドーパントを有している。ゲートの他方の側面には、ヘテロドープされたバッファ及びドリフト領域が形成されている。バッファ領域は第2極性のドーパントからなる。ドリフト領域がバッファ領域内に配置され、第1極性のドーパントによってドーピングされている。ドレインn+タップ領域がドリフト領域内に配置されている。  (もっと読む)

(もっと読む)

トランジスタ、メモリセルアレイ、および、トランジスタ製造方法

【課題】トレンチ型DRAMメモリセルの形成において、垂直型トラジスタとトレンチ型キャパシタの接続を容易化し、高集積化する。

【解決手段】第1および第2ソース/ドレイン領域と、該第1および第2ソース/ドレイン領域を接続する、半導体基板の中に配置されたチャネル領域と、ゲート電極とを含み、該ゲート電極は、上記第1および第2ソース/ドレイン領域間に流れる電流を制御するために、上記チャネル領域に沿って配置され、該チャネル領域から電気的に絶縁されている。また、上記チャネル領域では、該チャネルがリッジ状の形をなしたフィン領域を有している。この「リッジ状」とは、1つの上面と、第1ソース/ドレイン領域と第2ソース/ドレイン領域とを接続する線に対して(断面図では)垂直である2つの側面とからなる。この上面は、半導体基板の表面よりも下に配置されており、ゲート電極は、この上面および2つの側面に沿って設けられる。

(もっと読む)

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

サリサイド工程及びこれを利用した半導体素子の製造方法

【課題】サリサイド工程及びこれを利用した半導体素子の製造方法を提供する。

【解決手段】 本発明による金属シリサイド膜の形成方法は、シリコン領域を備える基板を準備する段階と、前記基板上にシリコン層を形成する段階と、前記シリコン層と接触する金属膜を形成する段階と、前記金属膜を有する基板を熱伝達気体を採択した対流または伝導方式を使用して等温熱処理して前記少なくとも前記金属膜の一部を金属シリサイド膜に転換する段階と、を含む。

(もっと読む)

半導体素子及びその製造方法

【課題】素子の電流駆動力を向上させ、ショットチャンネル効果を改善させることができる半導体素子及びその製造方法を提供する。

【解決手段】本発明は、Si−エピ層20,120を食刻して下部の埋込絶縁膜50,200を露出させ、一側のLDD40,180領域から他側のLDD領域40,180まで互いに平行して延長される開口部140を1つ以上形成し、ゲート電極がSi−エピ層20,120の表面を取り囲むようにした。

(もっと読む)

PMOSを具備する半導体素子の形成方法

【課題】本発明はPMOSを具備する半導体素子を形成する方法を提供する。

【解決手段】前記方法によると、半導体基板の全面上にポリシリコン膜を形成する。前記ポリシリコン膜にP型不純物をドーピングする。熱処理工程を進行する。そして、前記P型不純物がドーピングされたポリシリコン膜の上部を第1厚さだけ除去する。これによって、漏洩電流を防止して、素子の速度を向上させることができるPMOSを具備する半導体素子を形成することができる。

(もっと読む)

トレンチ構造を利用した横型半導体装置及びその製造方法

【課題】 長さ方向がゲート長方向と平行なトレンチに形成されたゲート電極を有し、単位平面積当たり大きなゲート幅を有する高駆動能力横型のMOSトランジスタの駆動能力を、平面的な素子面積を増加させずに向上させる半導体装置を提供する。

【解決手段】 半導体基板の表面に長さ方向がゲート長方向と平行なトレンチが形成された第1トレンチ領域013と、前記第1トレンチ領域の凹部底面と同一平面に設けられた第2トレンチ領域014および第3トレンチ領域015と、前記第1,第2,第3トレンチ領域の少なくとも1領域に形成された第2導電型のウェル領域と、前記第1トレンチ領域に設けられたゲート絶縁膜とゲート電極と、前記第1,第2と3トレンチ領域に前記ウェル領域より浅く設けられた第1導電型のソース領域とドレイン領域を有する半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁ゲート型電界効果トランジスタのチャネル長変調効果を低減するための半導体装置及び半導体装置の製造方法を提供する。

【解決手段】第1導電型の半導体基板1中に第2導電型のソース層及びドレイン層8を有する絶縁ゲート型電界効果トランジスタからなる半導体装置であって、ゲート電極3端部の半導体基板1表面付近に、ソース層及びドレイン層8よりも深さが浅い第2導電型の低濃度拡散層4と、少なくとも2つの濃度ピークを有する第1導電型の高濃度拡散層5,6とを備え、ゲート電極端部直下の半導体基板中の第1導電型の不純物濃度分布において、第1の濃度ピーク位置PK1が低濃度拡散層4中にあり、第2の濃度ピーク位置PK2が第1の濃度ピーク位置PK1よりも深くなっている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】素子分離膜が埋め込まれる溝の側壁に形成される熱酸化膜を厚くすることなく、半導体素子のハンプを抑制する。

【解決手段】 基板1上にシリコン層3を形成し、その上に下地膜4及び窒化シリコン膜5を形成する。窒化シリコン膜5及び下地膜4に開口部5aを形成し、開口部5a内に位置するシリコン層3の表面に第1の熱酸化膜6を形成する。第1の熱酸化膜6を、例えばウェットエッチングにより除去する。窒化シリコン膜5をマスクとしてシリコン層3をエッチングすることにより、開口部5a内に位置するシリコン層3に、溝を形成する。溝の表面に第2の熱酸化膜を形成し、その後、溝に、素子分離膜を埋め込む。

(もっと読む)

高融点金属シリサイド膜の製造方法、半導体装置の製造方法

【課題】高融点金属シリサイド膜を適切に形成することができる高融点金属シリサイド膜の製造方法を提供すること。

【解決手段】本発明の高融点金属シリサイド膜の製造方法は、シリコンを含む半導体基板1上に高融点金属膜9を形成する工程と、形成された高融点金属膜9の表面を非晶質化する工程と、非晶質化された高融点金属膜10上に窒化チタン膜11を形成する工程と、得られた基板を熱処理することにより高融点金属シリサイド膜12を形成する工程を備える。

(もっと読む)

半導体装置

【課題】 ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】 ソース/ドレイン領域の一方になり、かつビット線にもなる第1の不純物拡散層24の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

窒化珪素膜の製造方法及び半導体装置の製造方法

【課題】 窒化珪素膜の塩素不純物量の低減を実現し、ウェットエッチ耐性の高い窒化珪素膜の形成を可能とした窒化珪素膜の製造方法及びこの製造方法を備えた半導体装置の製造方法を提供することを目的とする。

【解決手段】 基体の表面に窒化珪素膜を形成する窒化珪素膜の製造方法であって、珪素と塩素とを含む第1のガスを前記基体の表面に供給する第1の工程と、窒素を含む第2のガスを前記基体の表面に供給する第2の工程と、水素を含む第3のガスを前記基体の表面に供給する第3の工程と、をこの順に繰り返すことを特徴とする窒化珪素膜の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート電極材料膜形成時に形成されたゲート電極材料膜/高誘電率ゲート絶縁膜の界面における寄生低誘電率界面層を還元し、ゲート絶縁膜の薄膜化を実現する。

【解決手段】 シリコン基板1上に下部界面層4としてのシリコン酸窒化膜4を形成し、その上に高誘電率ゲート電極5としてのHfアルミネート膜を形成する。Hfアルミネート膜5上にゲート電極材料膜7としてのポリシリコン膜をLPCVD法により570℃以上の温度で形成する。その後、ゲートドーパント9を注入する前に、950℃以上1050℃未満の温度で熱処理(PGA処理)8を行う。

(もっと読む)

シリサイド領域を有する半導体デバイスの製造方法

【課題】本発明は、半導体デバイスの製造方法及び半導体デバイスを含む集積回路の製造方法を提供する。

【解決手段】本発明の半導体デバイス(100)を製造する方法は、とりわけ、基板(110)上にゲート構造(120)を形成するステップオ、及びゲート構造(120)の近くの基板(110)にソース/ドレイン領域(190)を形成するステップを含む。本方法は、更に、ゲート構造(120)及び基板(110)をドライエッチングするステップ、及びゲート構造(120)及び基板(110)をドライエッチングするステップに続いて、ソース/ドレイン領域にフッ素を配置して、フッ化したソース/ドレインを形成するステップを含む。その後、本方法は、ゲート構造(120)とフッ化したソース/ドレインに金属スイサイド領域(510,520)を形成するステップを含む。

(もっと読む)

半導体装置とその製造方法

【課題】 本発明は、従来の構造を有するM0S型トランジスタでは不可能であった30から50Vの耐圧をもつ高耐圧構造を有するMOS型トランジスタの小型化、集積化を図ることことを目的とする。

【解決手段】 トレンチエッチング技術を使用し溝を形成し絶縁膜を埋め込み、イオン注入法を行い溝の側面に低濃度領域を形成することによりゲート電極の一端部と高濃度拡散領域の一端部の距離を自由に変える事により耐圧が容易に変えることができ、また小面積で提供できることを特徴とする。

(もっと読む)

1,041 - 1,060 / 1,105

[ Back to top ]