Fターム[5F140BH15]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054) | LDD(Lightly doped dorain−source) (1,105)

Fターム[5F140BH15]に分類される特許

1,081 - 1,100 / 1,105

金属ゲート集積化のためのゲートスタック及びゲートスタックのエッチングシーケンス

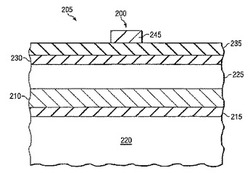

【課題】本発明は半導体デバイス(205)における金属ゲートスタック(200)を製作するためのプロセスを提供する。

【解決手段】本願の方法は、半導体基板(220)上に位置するゲート誘電体層(215)の上に金属層(210)を堆積させる段階を含む。本方法は、金属層(210)上にポリシリコン層(225)を形成する段階と、そのポリシリコン層(225)上に保護層(230)を生成する段階とを更に含む。本方法はは、また、保護層(230)上に無機反射防止被覆(235)を配置する段階を含む。他の実施形態では、金属ゲートスタックの前駆構造体及び集積回路の製造方法を含む。

(もっと読む)

ゲート型電界効果デバイス及びその製法

本発明はゲート型電界効果デバイスに関し、その製法にも関する。一例では、ゲート型電界効果デバイスはソース/ドレーン領域ペアを含み、チャンネル領域をそれらの間に有している。ゲートはソース/ドレーン領域間でチャンネル領域に近接して受領される。ゲートはソース/ドレーン領域間にゲート幅部を有している。ゲート誘電体はチャンネル領域とゲートに近接して受領される。ゲート誘電体は少なくとも2つの異なる領域をゲートの幅部に沿って有している。これら異なる領域はそれぞれ異なる誘電率kを有する2つの異質領域を提供するように異なる材料で提供される。 (もっと読む)

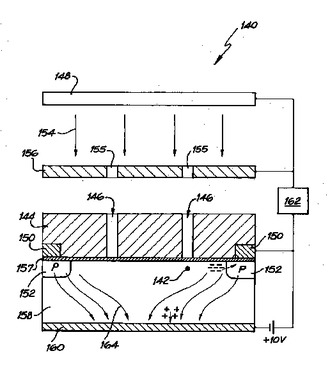

注入され計数されたドーパントイオン

本発明は、実質的に真性な半導体の基板(158)の領域に注入された、計数された数のドーパントイオン(142)を有する汎用タイプの半導体装置に関する。基板(158)の一つ以上のドープされた表面領域は、金属化され、電極(150)が形成される。計数された数のドーパントイオン(142)が、実質的に真性な半導体の領域に注入される。

【その他】

原文には、請求項11及び請求項11Aが存在する。請求項11Aは、オンライン手続上、請求項11内に記載した。

(もっと読む)

(もっと読む)

分離トレンチ

分離トレンチ(209)をウェハ(201)に形成するプロセスである。このプロセスでは、(例えば、異方性堆積法により)第1誘電体材料(307)をトレンチ(209)の中に堆積させ、次に第2誘電体材料(309)を(例えば、異方性堆積法により)トレンチ(209)内の第1誘電体材料(307)を覆うように堆積させる。第3材料(501)をトレンチ(209)内に、かつ第2誘電体材料(309)の上に堆積させる。第2材料(309)及び第3材料(501)の内の一方の材料は、他方の材料をエッチングしないように選択的にエッチングすることができる。一の例では、第1材料(307)は第2材料(309)よりも小さい誘電率を有する。  (もっと読む)

(もっと読む)

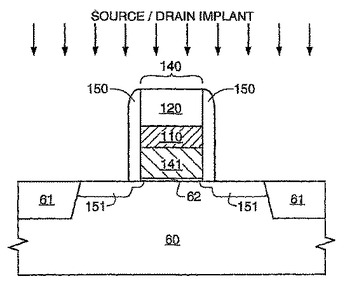

サイドウォールスペーサの形成方法

本発明により、基板(201)上のフィーチャ(206)に隣接するサイドウォールスペーサ(217、218)を形成することができる。フィーチャ(206)は1つ以上の保護層(220、207)に覆われる。スペーサ材料層(211)はフィーチャ(206)上に蒸着され、異方性エッチングされる。異方性エッチングに使用されるエッチング液はスペーサ材料を選択的に除去することに適しており、一方で1つ以上の保護層(220、207)はこのエッチング液による影響を実質的に受けない。その結果、1つ以上の層(220、207)はフィーチャがエッチング液にさらされるのを保護する。  (もっと読む)

(もっと読む)

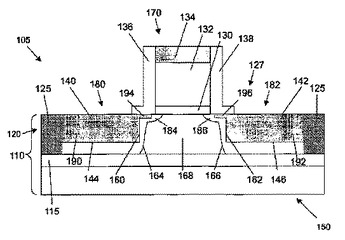

半導体装置及び半導体装置の製造方法

本発明は、半導体装置(105)及びこの装置の製造方法に関する。本発明の好ましい実施例は、シリコン半導体基板(110)、酸化膜層(115)及び活性層(120)を含む半導体装置(105)である。活性層では、絶縁領域(125)及び活性領域(127)が形成された。活性領域(127)は、ソース(180)、ドレイン(182)及び基体(168)を含む。ソース(180)及びドレイン(182)は、ソースエクステンション(184)及びドレインエクステンション(186)も含む。活性層(120)はゲート(170)を有する。ゲート(170)の両側にL字型側壁スペーサが位置する。ソース(180)及びドレイン(182)は、シリサイド領域(190、192)も含む。これらの領域の特徴は、側壁(136、138)の下に位置されたエクステンション(194、196)を有することである。これらのエクステンション(194、196)は、半導体装置(105)の性能を著しく改善するように、ソース(194)及びドレイン(196)の直列抵抗を大きく低減する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

シリコン基板101とポリシリコンゲート電極104とを電気的に絶縁する高誘電率ゲート絶縁膜102として、Hf、Zr又はAlの少なくとも一つの構成元素を含有する金属酸化物薄膜又は金属シリケート薄膜が設けられている。この半導体装置について、ポリシリコンゲート電極104を加工した後に、高誘電率ゲート絶縁膜102の側面又は表面が露出した状態で、分子中に酸素原子を含む酸化剤雰囲気中で熱処理を施す。この熱処理により、高誘電率ゲート絶縁膜102とポリシリコンゲート電極104との界面の電気的欠陥105が消失する。 (もっと読む)

MIS型電界効果トランジスタ

下地SiGe層1上に歪みSi層2をエピタキシャル成長させ、ゲート絶縁膜3aとゲート電極4aを形成した後、ゲート電極4aをマスクにして、下地SiGe層1及び歪みSi層2に不純物をイオン注入し(図2(a))、活性化のための熱処理を行ってソース・ドレイン領域6を形成する(図2(b)、(c))。このとき、歪みSi層2の膜厚は、最終的なMISFETのソース・ドレイン領域6の不純物濃度が最大となる深さをTp(=Rp)としたとき、2Tp以下にする。 (もっと読む)

半導体装置および半導体集積回路装置

pチャネルMOSトランジスタおよびnチャネルMOSトランジスタの各々においてチャネル方向を<100>方向に設定し、STI型素子分離構造に、引っ張り応力を蓄積した第1の応力補償膜を形成し、さらにシリコン基板上に素子分離構造を覆うように引っ張り応力を蓄積した第2の応力補償膜を形成する。 (もっと読む)

固相エピタキシャル再成長を用いてドーピングプロファイルの深さを低減した半導体基板及び同半導体基板の生産方法

半導体デバイスの生産方法であって、a)半導体基板を準備し、b)半導体基板の最上面上に絶縁層を設け、c)適当な注入によって、前記半導体基板の最上層中にアモルファス層を作り、d)所定のドーピングプロファイルを伴う前記アモルファス層を作るための前記絶縁層を通して、前記半導体基板中へドーパントを、前記ドーピングプロファイルが前記絶縁層内に位置するピーク値を持つように注入し、e)前記アモルファス層を再成長させ、前記ドーパントを活性化する固相エピタキシャル再成長作用を適用することを含む半導体デバイスの生産方法。  (もっと読む)

(もっと読む)

半導体装置の製造方法およびその方法で得られる半導体装置

本発明は、シリコンの半導体本体がその表面に拡張領域を含む第1の導電型のソース領域及びドレイン領域と、前記ソース領域と前記ドレイン領域の間に前記第1の導電型とは反対の第2の導電型のチャネル領域と、前記チャネル領域上のゲート誘電体により前記半導体本体の表面から分離されているゲート領域と、を有し、第2の導電型で前記チャネル領域より高濃度のドーピング濃度であるポケット領域が前記拡張領域の下に形成され、前記ポケット領域は前記半導体本体に重イオンを注入することで形成され、注入後適温での第1のアニール処理およびより高い温度で早い立ち上がりの第2のアニール処理が行われる電界効果トランジスタを備える半導体装置の製造方法に関する。本発明によれば、その方法は、2つのアニール処理の間に、半導体本体の表面からポケット注入領域まで延びる半導体本体の表面領域にアモルファスシリコンを意図的に存在させることを特徴とする。これは、例えば適時に第1のアニール処理を中断すること、または第1と第2のアニール処理の間に不活性イオンを注入することで適切な領域をアモルファス化することにより得られる。このようにして、将来のCMOS装置の利点であるポケット領域7のきわめて急峻かつ狭いドーピングプロファイルが得られる。  (もっと読む)

(もっと読む)

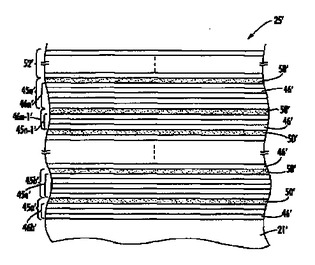

完全に量子井戸が空乏化した低出力のマルチチャネルCMOSFET

マルチチャネル半導体デバイスは、完全に、または部分的に量子井戸が空乏化(排除)(depleted)されており、CMOSFETのようなULSIデバイスにおいて特に役立つ。マルチチャネル領域(15)は、最上部のチャネル領域上に、例えばゲート絶縁膜(14c)により分離されるゲート電極が形成された状態で、基板(12)上に形成される。マルチチャネル領域(15)およびゲート電極(16)の垂直方向の積み重なりが、デバイスによって占有されるシリコン領域を増加させることなく、半導体デバイス中の駆動電流を増加させることができる。  (もっと読む)

(もっと読む)

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

マスキング方法

本発明はマスキング方法を包含する。1つの実施において、ホウ素ドープアモルファスカーボンを含むマスキング材料が、半導体基板上に形成されたフィーチャーを覆って形成される。マスキング材料は少なくとも約0.5原子パーセントのホウ素を含む。マスキング材料は実質的に異方的にエッチングされ、ここでそのエッチングはホウ素ドープアモルファスカーボンを含む異方的にエッチングされたサイドウォールスペーサをフィーチャーのサイドウォール上に形成するのに有効である。次に、スペーサに最も近い基板が、ホウ素ドープアモルファスカーボンを含むスペーサをマスクとして用いながら加工される。スペーサに最も近い基板を加工した後、ホウ素ドープアモルファスカーボンを含むスペーサが基板からエッチングされる。他の実施および面も考えられる。 (もっと読む)

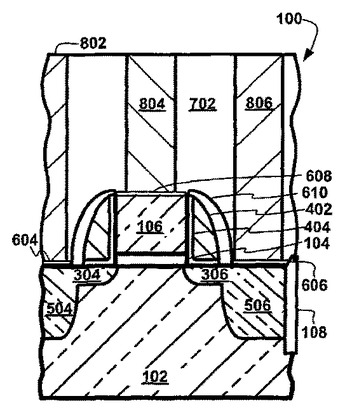

集積回路技術におけるシリサイド化スペーサ

集積回路(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に誘電体層(702)をたい積する。その後、誘電体層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

LDMOSトランジスタを有する電子装置

本発明のLDMOSトランジスタは、段付きシールド構造及び/又は第1及び第2ドレイン延長領域を具備し、前記第1ドレイン延長領域は、前記第2ドレイン延長領域よりも高いドーパント濃度を有し、前記シールドによって被われている。

(もっと読む)

(もっと読む)

窒化シリコン酸化物ゲート誘電体を製造する方法

【課題】 ウェハ内における相対的に均一な厚さ及び窒素濃度を有するSiOxNy層を製造する方法を提供すること。

【解決手段】 基板を準備するステップと、該基板の上面に二酸化シリコン層を形成するステップと、還元雰囲気内でプラズマ窒化を実行し、該二酸化シリコン層を酸窒化シリコン層に変換するステップとを含む、ゲート誘電体層を製造する方法である。このように形成された誘電体層を、MOSFETの製造において用いることができる。

(もっと読む)

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

バンド設計超格子を有する半導体装置を製作する方法

複数の積層された層群を有する超格子を形成するステップによって、半導体装置を製作する方法である。また当該方法は、前記超格子を通って、前記積層された層群と平行な方向に、電荷キャリアの輸送が生じる領域を形成するステップを有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。前記エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取りこまれた、少なくとも一つの非半導体分子層を有し、前記超格子は、超格子が存在しない場合に比べて、前記平行な方向において大きな電荷キャリア移動度を有する。また前記超格子は、共通のエネルギーバンド構造を有しても良い。

(もっと読む)

(もっと読む)

バンド設計超格子を有するMOSFETを有する半導体装置

半導体装置は、基板と、該基板に隣接する少なくとも一つのMOSFETとを有する。MOSFETは、超格子チャンネルを有し、該超格子チャンネルは、複数の積層された層群を有する。またMOSFETは、超格子チャンネルと水平方向に隣接するソースおよびドレイン領域と、超格子上に設置されたゲートと、を有し、超格子チャンネルを通って、積層された層群と平行な方向に電荷キャリアの輸送が生じる。超格子チャンネルの各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取り込まれた、少なくとも一つの非半導体分子層を有し、超格子チャンネルは、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

1,081 - 1,100 / 1,105

[ Back to top ]