Fターム[5F140BK17]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域の形成 (4,176) | 成長 (733)

Fターム[5F140BK17]の下位に属するFターム

選択成長 (541)

Fターム[5F140BK17]に分類される特許

181 - 192 / 192

トランジスタ及びこれの製造方法

【課題】 超高集積を有して形成することができ、改善された構造の不純物領域を有する半導体装置のトランジスタ及びトランジスタを製造する方法が開示されている。

【解決手段】 超高集積を有して形成することができながら改善された構造の不純物領域を有する半導体装置のトランジスタにおいて、前記トランジスタは表面、表面より低い高さを有する{100}面である底面、及び表面と底面とを連結する{111}面である側面を有する半導体基板を含む。ゲート構造物が表面上に形成される。エピタキシャル層が底面と側面上に形成される。不純物領域がゲート構造物の両側に形成される。急なPN接合を形成することができるので、不純物領域の間で短チャンネル効果の発生を抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】電流容量の増大とラッチアップ耐量の向上を図ることができる横型IGBTなどの半導体装置およびその製造方法を提供する。

【解決手段】貼り合わせ酸化膜2を介して支持基板1上にn型半導体層3が形成されたSOI基板100のn型半導体層3に貼り合わせ酸化膜2に接するように形成されるp型ベース層4と、このp型ベース層4と離してn型半導体層3に貼り合わせ酸化膜2に接するように形成されるnバッファ層5と、p型ベース層4内に形成される第1トレンチ6と、n型バッファ層内に形成される第2トレンチ7と、p型ベース層4の表面層に第1トレンチ6の開口部近傍に接するように形成されるn型エミッタ層10と、n型バッファ層5の表面層に第2トレンチ7と接するように形成されるp型コレクタ層11と、n型エミッタ層10とn型半導体層3に挟まれたp型ベース層4上にゲート酸化膜12を介して形成されるゲート電極13と、第2トレンチ6内部を充填して形成されるエミッタ電極14と、第2トレンチ7内部を充填して形成されるコレクタ電極15とを有する構成とする。

(もっと読む)

半導体素子及びその製造方法

【課題】素子の電流駆動力を向上させ、ショットチャンネル効果を改善させることができる半導体素子及びその製造方法を提供する。

【解決手段】本発明は、Si−エピ層20,120を食刻して下部の埋込絶縁膜50,200を露出させ、一側のLDD40,180領域から他側のLDD領域40,180まで互いに平行して延長される開口部140を1つ以上形成し、ゲート電極がSi−エピ層20,120の表面を取り囲むようにした。

(もっと読む)

性能が向上されたCMOS素子及びその製造方法

【課題】 性能が向上されたCMOS素子及びその製造方法を提供する。

【解決手段】 本発明のCMOS素子は、第1の幅領域と、該第1の幅より広い第2の幅領域を有するとともにコンタクト形成領域になる少なくとも一つの多幅アクティブ領域対と、を含む第1のアクティブ領域と、第1のアクティブ領域上に配列された第1のゲートと、第1のアクティブ領域内に形成された第1の導電型ソース/ドレーン領域と、を含む第1の導電型MOSトランジスタ、および、第1の幅より広い第3の幅を有する第2のアクティブ領域と、第2のアクティブ領域上に配列された第2のゲートと、第2のアクティブ領域内に形成された第2の導電型ソース/ドレーン領域と、を含む第2の導電型MOSトランジスタを備える。そして、CMOS素子の製造方法もまた提供される。これにより、電子と正孔の移動度の均衡が得られてCMOS素子の性能を向上することができる。

(もっと読む)

半導体装置

【課題】高耐圧化と低オン抵抗化を図ることができる半導体装置を提供する。

【解決手段】半導体基板1上に形成されたpウエル領域であるP−well35と、このP−well35の表面層に形成されるpオフセット領域であるP−off5と、P−off5の表面からP−well35に達するように形成したトレンチ19と、このトレンチ19の側壁にゲート酸化膜20を介して形成したゲート電極21と、トレンチ底に形成した拡張ドレイン領域である拡張ドレイン領域であるN−body6と、このN−body6と接するようにトレンチ19内部上方に向かって形成されたドレイン領域となるnエピタキシャル層30と、Pwell35の表面層に形成したソース領域となる上部のn+ 領域8とで構成する。この構成では、タングステン層23を形成する箇所にドレイン領域となるnエピタキシャル層30を形成するために、トレンチ19を広げることなく、ゲート電極21とドレイン領域となるnエピタキシャル層30の間隔を広げることができるために、高耐圧化と、低オン抵抗化を図ることができる。

(もっと読む)

メモリデバイス、トランジスタ、メモリセル並びにそれらの製造方法

メモリデバイスはメモリセルのアレイと周辺デバイスを含んでいる。少なくとも一部の個別メモリセルはSiCを含む炭酸化部分を含んでいる。少なくとも一部の周辺デバイスは炭酸化部分を含まない。トランジスタは第1ソース/ドレーン、第2ソース/ドレーン、第1ソース/ドレーンと第2ソース/ドレーンとの間にSiCを含む半導体基板の炭酸化部分を含んだチャンネル、及びチャンネルの両側と作動式に関係するゲートを含んでいる。 (もっと読む)

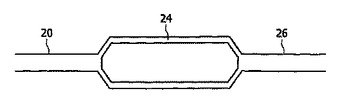

ナノスケールFET

トランジスタデバイスは、ソース領域、ドレイン領域、およびソース領域とドレイン領域の間のチャネル領域を有する連続リニアナノ構造体で形成される。ソース領域(20)とドレイン領域(26)はナノワイヤで形成され、チャネル領域(24)はナノチューブの形である。ソース領域とドレイン領域の間のチャネル領域における伝導を制御するためにチャネル領域(24)に隣接する絶縁ゲート(32)が提供される。  (もっと読む)

(もっと読む)

改良した歪みシリコンCMOSデバイスおよび方法

【課題】 デバイス・チャネルに一軸性歪みを生成してキャリア移動度を向上させた半導体デバイスを提供する。

【解決手段】 本発明は、半導体デバイスのデバイス・チャネルに一軸性歪みを生成する半導体デバイスおよびその形成方法を提供する。一軸性歪みは、引張り性または圧縮性とすることができ、デバイス・チャネルに平行な方向である。一軸性歪みは、歪み誘発ライナ、歪み誘発ウェル、またはそれらの組み合わせによって、二軸性歪み基板表面において生成することができる。一軸性歪みは、歪み誘発ウェルおよび歪み誘発ライナの組み合わせによって、緩和基板において生成することも可能である。また、本発明は、歪み誘発分離領域によって二軸性歪みを増大させるための手段も提供する。更に、本発明が提供するCMOSデバイスにおいては、CMOS基板のデバイス領域を別個に処理して、圧縮性または引張り性の一軸性歪み半導体表面を提供する。

(もっと読む)

完全に量子井戸が空乏化した低出力のマルチチャネルCMOSFET

マルチチャネル半導体デバイスは、完全に、または部分的に量子井戸が空乏化(排除)(depleted)されており、CMOSFETのようなULSIデバイスにおいて特に役立つ。マルチチャネル領域(15)は、最上部のチャネル領域上に、例えばゲート絶縁膜(14c)により分離されるゲート電極が形成された状態で、基板(12)上に形成される。マルチチャネル領域(15)およびゲート電極(16)の垂直方向の積み重なりが、デバイスによって占有されるシリコン領域を増加させることなく、半導体デバイス中の駆動電流を増加させることができる。  (もっと読む)

(もっと読む)

減少されたゲート高さを有するトランジスタを製造する方法

【課題】減少されたゲート高さを有する集積回路トランジスタを形成する方法およびシステムを開示すること。

【解決手段】本方法は、基板、基板の上のゲート導体(13)、およびゲート導体(13)の上の少なくとも1つの犠牲層(14〜16)を有する積層構造を形成する。このプロセスは、積層構造を基板から延びる少なくとも1つのゲート・スタックにパターン形成し、ゲート・スタックに隣接してスペーサ(60)を形成し、ゲート・スタックに隣接してソースおよびドレイン領域(71)を形成するようにスペーサで保護されていない基板の領域にドーピングし、そして、スペーサ(60)および犠牲層(14〜16)を除去する。

(もっと読む)

マスキング方法

本発明はマスキング方法を包含する。1つの実施において、ホウ素ドープアモルファスカーボンを含むマスキング材料が、半導体基板上に形成されたフィーチャーを覆って形成される。マスキング材料は少なくとも約0.5原子パーセントのホウ素を含む。マスキング材料は実質的に異方的にエッチングされ、ここでそのエッチングはホウ素ドープアモルファスカーボンを含む異方的にエッチングされたサイドウォールスペーサをフィーチャーのサイドウォール上に形成するのに有効である。次に、スペーサに最も近い基板が、ホウ素ドープアモルファスカーボンを含むスペーサをマスクとして用いながら加工される。スペーサに最も近い基板を加工した後、ホウ素ドープアモルファスカーボンを含むスペーサが基板からエッチングされる。他の実施および面も考えられる。 (もっと読む)

半導体基板におけるドーパントの拡散を低速化する方法およびこれにより製造されたデバイス

【課題】 ひずみSi/Si1-XGeXデバイス基板において、極めて浅い接合を形成する方法およびそれによって得られる半導体構造を提供する。

【解決手段】 半導体デバイスを形成する方法(およびその結果として得られる構造)は、基板上に、ドーパントおよび少なくとも1つの種を注入するステップと、基板をアニールするステップであって、少なくとも1つの種が、基板のアニールの間のトーパントの拡散を遅らせるステップと、を含む。

(もっと読む)

181 - 192 / 192

[ Back to top ]