Fターム[5F140BK17]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域の形成 (4,176) | 成長 (733)

Fターム[5F140BK17]の下位に属するFターム

選択成長 (541)

Fターム[5F140BK17]に分類される特許

61 - 80 / 192

半導体装置及びその製造方法

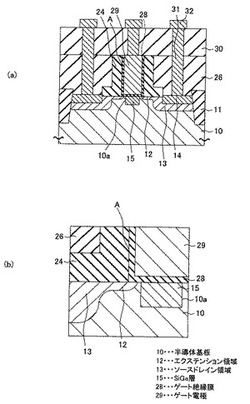

【課題】接合リークを抑制しながら、キャリアの移動度向上とチャネル中でのキャリア速度の増加を実現することができるトランジスタを提供する。

【解決手段】半導体基板10のチャネル形成領域にチャネル方向に第1の幅を有するSiGe層15が埋め込まれ、チャネル形成領域上にゲート絶縁膜28が形成され、ゲート絶縁膜上に、第1の幅より大きい第2の幅を有してSiGe層の形成領域からはみ出す領域を有するゲート電極29が形成され、チャネル形成領域を挟む半導体基板においてエクステンション領域12を有するソースドレイン領域13が形成されて、電界効果トランジスタが構成されており、エクステンション領域と半導体基板の接合面から伸びる空乏層がSiGe層に達しないようにエクステンション領域とSiGe層が離間されている。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】 ゲート電極下部のダメージを低減することによって高いデバイス特性が得られることができる半導体装置の製造方法を提供する。

【解決手段】 基板101上にGaN緩衝層102を形成する工程と、GaN緩衝層102上にun−AlGaN障壁層103を形成する工程と、un−AlGaN障壁層103上に再成長用マスク110を形成する工程と、un−AlGaN障壁層103上に、n−InAlNコンタクト層109を再成長させる工程と、un−AlGaN障壁層103上の再成長用マスク110を除去する工程と、n−InAlNコンタクト層109上にソース電極107及びドレイン電極108を形成する工程と、再成長用マスク110が除去されたun−AlGaN障壁層103上の領域に、ゲート電極106を形成する工程と、によって半導体装置を製造する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

埋め込み拡張領域を有するSOIトランジスタ、及びその形成方法

【課題】 改善された拡張部の抵抗及びチャネルの歪み特性を有するシリコン・オン・インシュレータ(SOI)トランジスタ及びそうしたSOIトランジスタを形成する方法を提供する。

【解決手段】 シリコン・オン・インシュレータ(SOI)トランジスタ・デバイスは、バルク基板の上に形成された埋め込み絶縁体層と、埋め込み絶縁体層上に形成されたSOI層と、トランジスタ・デバイスのソース及びドレイン領域に対応する、ゲート導体の対向する側に隣接して配置された一対のシリコン含有エピタキシャル領域とを含み、エピタキシャル領域の部分は、埋め込み絶縁体内に埋め込まれ、かつ、トランジスタ・デバイスのチャネル領域の対向する端部におけるソース及びドレイン拡張領域に対応するSOI層の垂直面及び底面の両方と接触している。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高品質な特性を有する電界効果トランジスタ及びその方法を提供する。

【解決手段】素子分離領域106間のソース/ドレイン領域114、及びポケット領域116を含んでいる半導体基板102と、素子分離領域間の半導体基板の上面のトレンチ110内にあって、(100)面を有する底面及び上面と、2つ以上の平面を有する側面とを有するシリコンゲルマニウム層112と、ゲート絶縁層120、ゲート電極122、及びサイドスペーサ128を含むシリコンゲルマニウム層上のゲート構造と、ゲート構造によって覆われていないシリコンゲルマニウム層及び半導体基板の上部分上のメタルシリサイド124とを備え、シリコンゲルマニウム層は、チャネル長方向において、ゲート構造の下で側面を有していない。

(もっと読む)

不純物活性化方法、半導体装置の製造方法

【課題】低いシート抵抗を得る不純物活性化方法、および、ソース・ドレイン拡張部を均一な深さで再現性よく形成する製造方法を提供。

【解決手段】半導体基板21において半導体基板21よりも不純物濃度が高いボロンイオン注入層43が形成されており、ボロンイオン注入層43にパルス幅が10〜1000フェムト秒のパルスレーザー光を照射して、ボロンイオン注入層43を活性化させる。パルスレーザー光におけるパルス幅、レーザーフルーエンスおよび照射パルス数を含む照射条件を変更することにより、パルスレーザー光照射後のボロンイオン注入層43のシート抵抗を制御する。

(もっと読む)

半導体装置

【課題】チャネル領域に歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】第一半導体からなる半導体基板1と、半導体基板1上に形成されたゲート絶縁膜2と、ゲート絶縁膜2上に形成されたゲート電極3と、ゲート絶縁膜2を介したゲート電極3下のチャネル領域4と、チャネル領域4に隣接する不純物原子が注入されたソース/ドレイン拡散層領域5,6と、を有し、ソース/ドレイン拡散層領域5,6に第一半導体と格子定数の異なる第二半導体の結晶からなる一軸歪み誘発層7を含み、一軸歪み誘発層7の底部と半導体基板1との界面で格子不整合が起こっており、一軸歪み誘発層7を形成した際に生じる半導体基板1との格子整合に起因する歪みが緩和している。

(もっと読む)

電界効果トランジスタ

【課題】高いしきい値電圧と大きい動作電流とを両立した電界効果トランジスタを提供すること。

【解決手段】基板と、前記基板上に形成され、窒化物系化合物半導体からなり、チャネル層を含む半導体層と、前記チャネル層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層上において前記ゲート電極を挟むように配置されたソース電極およびドレイン電極と、を備え、前記チャネル層の表面の、少なくとも前記ゲート電極直下の領域が、窒素極性の表面を含む。

(もっと読む)

低温炭素及び/又は分子炭素注入された歪み薄膜上の隆起型ソース/ドレインの形成

半導体構造のチャネル領域に引張応力を増大する方法が開示される。この方法は、1つ以上の低温炭素又は分子炭素イオン注入ステップを実行することを含み、炭素イオンを半導体構造中に注入して、チャネル領域の両側に歪み層を生成する。次に、隆起型ソース/ドレイン領域が歪み層上に形成され、続いて隆起型ソース/ドレイン領域をドープするためにイオン注入ステップが用いられる。ミリ秒アニールステップは、歪み層及び隆起型ソース/ドレイン領域を活性化する。歪み層は半導体構造のチャネル領域中のキャリア移動度を増大させる。一方、隆起型ソース/ドレイン領域は、隆起型ソース/ドレイン領域にその後ドーパントイオンを注入することによって引き起こされる、歪み層中のひずみの低減を最小化する。 (もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

電界効果トランジスタ

【課題】耐電圧を高めて、大電流を安定して継続的に流すことができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ10は、III族窒化物半導体から成る半導体活性層11の表面領域に形成されたソース16s及びドレイン16dと、半導体活性層11上にゲート酸化膜12を介して形成されたゲート電極13とを備える。電界効果トランジスタ10は、ゲート電極13とドレイン16dとの間の半導体活性層11内に形成された電界緩和層20を有する。電界緩和層20は、正の電荷が生じる第1の層21と負の電荷が生じる第2の層22とが、膜厚方向に交互に配置される積層構造を有する。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

垂直置換ゲートトランジスタと集積可能な容量の構造及び作製法

【課題】垂直MOSFETデバイス及び容量に関連したプロセス及び構成を提供する。

【解決手段】半導体デバイスは半導体材料の第1の層と、第1の層中に形成された第1のソース/ドレイン領域を有する電界効果トランジスタを含む。チャネル領域は、第1の層上に形成され、第2のソース/ドレイン領域235はチャネル領域上に形成される。集積回路構造は底部プレート266、誘電体層258及び最上部容量プレート259を有する容量を更に含む。作製方法において、電界効果トランジスタのソース領域及びドレイン領域から成るグループから選択された第1のデバイス領域が、半導体層上に形成される。第1の電界効果トランジスタゲート領域265が、第1のデバイス領域上に形成される。間にはさまれた誘電体層を有する最上部及び底部層も、半導体層上に形成される。別の実施例において、容量層は半導体層中に形成された溝又は窓内に形成される。

(もっと読む)

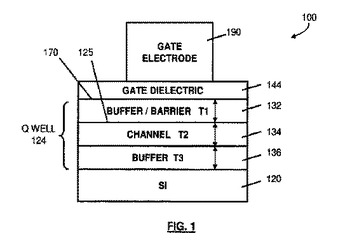

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

半導体装置

【課題】トランジスタの集積化を妨げることなく、トランジスタの駆動力を向上させる半導体装置を提供する。

【解決手段】所定の結晶からなる半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、ゲート幅方向に凸部を有して前記半導体基板内に形成され、前記所定の結晶とは異なる格子定数を有するエピタキシャル結晶が埋め込まれたソース・ドレイン領域と、を具備するトランジスタと、前記凸部以外の前記ソース・ドレイン領域に接続されたコンタクトプラグと、を備えた半導体装置を提供する。

(もっと読む)

電界効果トランジスタ

【課題】オン動作時における耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成されたキャリア走行層と、キャリア走行層上に形成され、キャリア走行層とは反対の導電型を有し、キャリア走行層に到る深さまで形成されたリセス部によって分離したキャリア供給層と、分離した各キャリア供給層上にリセス部を挟んで形成されたソース電極およびドレイン電極と、分離した各キャリア供給層上にわたってリセス部内におけるキャリア走行層の表面を覆うように形成されたゲート絶縁膜と、リセス部においてゲート絶縁膜上に形成されたゲート電極と、を備え、ソース電極側のキャリア供給層は、該ソース電極直下に位置するソースコンタクト領域と、ゲート電極の下方に位置し、ソースコンタクト領域よりもキャリア濃度が低いソース電界緩和領域とを有する。

(もっと読む)

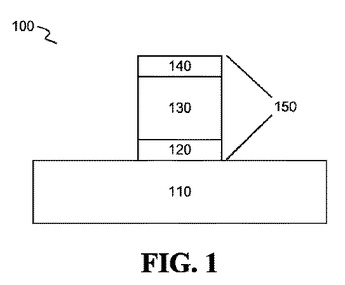

歪み半導体デバイス用のゲルマニウム含有量が漸次変化した高ゲルマニウム化合物膜

ゲルマニウム含有量が漸次変化した高ゲルマニウム化合物領域を供する装置及び方法に係る実施例が全体として記載されている。他の実施例も記載及びクレームされている。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】微細化された3次元的なデバイスを実現し得る、半導体装置の製造方法を提供する。

【解決手段】開示される、本発明の一実施形態による、半導体装置の製造方法によれば、ライン・アンド・スペース状の第2の層12を、第2の層12が延在する方向と交わる方向に延びるライン・アンド・スペース状の第8の層25をマスクとしてエッチングすることにより、二次元的に配列される第2の層12を得、これにより下地層をエッチングすることにより、二次元的に配列されるピラーを形成することができる。

(もっと読む)

61 - 80 / 192

[ Back to top ]