Fターム[5F140BK29]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極の形成 (2,400) | PVD (795)

Fターム[5F140BK29]に分類される特許

21 - 40 / 795

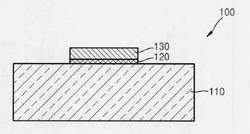

グラフェンを含む電極構造体及び電界効果トランジスタ

【課題】グラフェンを含む電極構造体及び電界効果トランジスタを提供する。

【解決手段】半導体層上のグラフェンと、グラフェン上の電極メタルと、を備え、該グラフェンは、半導体層と直接的に接触し、電極メタルは、グラフェンと直接的に接触する電極構造体である。半導体層は、シリコン、ゲルマニウム、シリコン・ゲルマニウム、III−V族半導体、及びII−VI族半導体を含むグループから選択された一つで形成される。グラフェンは、単層または二層のグラフェンで形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 寄生ダイオードの逆回復時間を短縮でき、スイッチング損失の低減が図れるLDMOSトランジスタを低コストで提供する。

【解決手段】 LDMOSトランジスタT1が、p型半導体基板1内にp型ボディ領域2とp型埋め込み拡散領域3とn型ドリフト領域6を、ボディ領域2内にn型ソースコンタクト領域4とp型ボディコンタクト領域5を、ドリフト領域6内にn型ドレインコンタクト領域7を、ソースコンタクト領域7とドリフト領域6間のボディ領域2の上方にゲート絶縁膜8を、ゲート絶縁膜8上にゲート電極9を夫々備えて形成され、ドリフト領域6とボディ領域2は相互に接触し、埋め込み拡散領域3が、ボディ領域2の底面と接触するボディ領域2よりも深い位置に、半導体基板1の表面に平行な方向に、少なくともボディ領域2からドレインコンタクト領域7のボディ領域2から最も離間した遠方端の下方まで延在している。

(もっと読む)

半導体装置及びその製造方法、電源装置、高周波増幅器

【課題】放置時間が長くても、化合物半導体積層構造の表面のダングリングボンドがフッ素で終端された状態が維持されるようにし、閾値電圧の変動を抑制して、信頼性を向上させる。

【解決手段】半導体装置は、化合物半導体積層構造6と、化合物半導体積層構造6の表面を覆うフッ素含有バリア膜9と、化合物半導体積層構造6の上方にフッ素含有バリア膜9を挟んで設けられたゲート電極8とを備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】GaとSiとの反応を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、Si基板1と、Si基板1の表面に形成されたSi酸化層3と、Si酸化層3上に形成され、Si酸化層3の一部を露出する核形成層2と、Si酸化層3及び核形成層2上に形成された化合物半導体積層構造9と、が設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

電界効果トランジスタ

【課題】高耐圧性をより確実に実現することができる電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成されたキャリア走行層と、前記キャリア走行層上に形成され、前記キャリア走行層とは反対の導電型を有し、前記キャリア走行層内部に到る深さまで形成されたリセス部によって分離したキャリア供給層と、前記分離した各キャリア供給層上に前記リセス部を挟んで形成されたソース電極およびドレイン電極と、前記分離した各キャリア供給層上にわたって前記リセス部内における前記キャリア走行層の表面を覆うように形成されたゲート絶縁膜と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極と、を備え、前記リセス部の前記キャリア供給層上面からの深さが、前記キャリア供給層の層厚より大きく200nm以下である。

(もっと読む)

半導体装置

【課題】低オン抵抗であって、かつ、ノーマリーオフの電界効果型トランジスタを提供する。

【解決手段】基板10の上に形成された電子走行層11と、電子走行層11の上に、電子走行層11よりもバンドギャップの広い半導体により形成された電子供給層12と、電子供給層12の上に、電子供給層よりもバンドギャップの狭い半導体により形成されたバリア形成層13と、バリア形成層13の上に、不純物のドープされた半導体により形成された上部チャネル層14と、バリア形成層13及び上部チャネル層14を除去することにより形成されたバリア形成層13及び上部チャネル層14の側面と、側面に形成された絶縁膜20と、絶縁膜20を介し形成されたゲート電極21と、上部チャネル層14と接続されるソース電極22と、電子供給層12または電子走行層11と接続されるドレイン電極23と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

高電子移動度トランジスタとその製造方法

【課題】高電子移動度トランジスタにおいて、ゲート部のドレイン側端部における電界集中を緩和する。

【解決手段】高電子移動度トランジスタ10は、導電体部23と第1抵抗部R1と第2抵抗部R2を備えている。導電体部23は、ドレイン電極21とゲート部26の間に設けられている。第1抵抗部R1は、一端がドレイン電極21に電気的に接続されており、他端が導電体部23に電気的に接続されている。第2抵抗部R2は、一端がソース電極28に電気的に接続されており、他端が導電体部23に電気的に接続されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とチャネル層との間の障壁層に低抵抗領域を備えた構成において、ゲートリーク電流を防止することによりドレイン電流の最大値の向上を図ることが可能な半導体装置を提供する。

【解決手段】化合物半導体で構成されたチャネル層14と、チャネル層14上に設けられた上部障壁層15とを備え、上部障壁層15における表面層には、不純物を含有することにより周囲よりも低抵抗に保たれた低抵抗領域15gが設けられている。また、この低抵抗領域15gを挟んだ位置において上部障壁層15に接続されたソース電極17sおよびドレイン電極17dを備えている。さらに、低抵抗領域15g上に設けられたゲート絶縁膜18と、このゲート絶縁膜18を介して低抵抗領域15g上に設けられたゲート電極19とを備えている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

窒化物系半導体装置

【課題】ゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、ノーマリオフの双方向動作が可能な窒化物系半導体装置を提供する。

【解決手段】窒化物系半導体素子10は、第1MOSFET部30及び第2MOSFET部31を備えており、第1ゲート電極26と第2ゲート電極27との間に設けられた第1SBD金属電極28及び第2SBD金属電極29がAlGaN層20とショットキー接合されている。第1SBD金属電極28と第1電極24とが接続されており、電気的に短絡していると共に、第2SBD金属電極29と第2電極25とが接続されており、電気的に短絡している。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】バッファ層を有する半導体素子において、チャネルの基準電位を固定する半導体素子及びその製造方法を提供する。

【解決手段】基板10と、基板上に設けられ、エネルギーギャップの異なる複数種類の窒化物半導体が積層された積層体を少なくとも1層有するバッファ層20と、バッファ層上に設けられた窒化物半導体のチャネル層30と、バッファ層の側面に電気的に接続された側面電極60と、チャネル層の上方に形成され、チャネル層と電気的に接続されたチャネル電極52,56とを備える半導体素子。

(もっと読む)

スイッチング素子及びこれを用いた電源装置

【課題】ソース電極とドレイン電極間の容量を低減し、スイッチングロスを減らすことができるスイッチング素子、及び該スイッチング素子を搭載した効率が向上した電源装置の提供。

【解決手段】Si基板1と、該Si基板1上に形成されたソース電極8及びドレイン電極9を有してなり、ソース電極8及びドレイン電極9の配置方向と直交する方向の層中であって、ソース電極8及びドレイン電極9のいずれか一方のみと接している領域に、p型領域とn型領域が接している部分24であるpn接合を少なくとも1つ有するスイッチング素子である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

テラヘルツ波素子

【課題】テラヘルツ波を発生又は検出するテラヘルツ波素子において、単色性が良いテラヘルツ波を効率良く出射する。

【解決手段】テラヘルツ波素子は、基板101の上に形成された第1の半導体層102と、第1の半導体層102の上に形成された第2の半導体層104と、第2の半導体層104の上に形成されたゲート電極106と、第2の半導体層104の上にゲート電極106を挟んで対向するように形成されたソース電極107及びドレイン電極108と、第2の半導体層104の上におけるゲート電極106とソース電極107との間及びゲート電極106とドレイン電極108との間に形成され、複数の金属膜109が周期的に配置された周期構造を有する周期金属膜109A,109Bと、ゲート電極106及び複数の金属膜109の上方に配置された第1のミラー111と、基板101の下に形成された第2のミラー112とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】寄生抵抗が低く、接合リーク電流が抑制されたトランジスタを容易に形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態にかかる半導体装置の製造方法は、シリコン基板中のチャネル領域上にゲート絶縁膜を介してゲート電極を形成し、シリコン基板に所望の不純物を注入することにより、チャネル方向に沿ってチャネル領域を挟むようにシリコン基板中にソース領域とドレイン領域とを形成し、ソース領域及びドレイン領域の表面をアモルファス化することにより、それぞれの表面に不純物を含むアモルファス領域を形成し、アモルファス領域の上にニッケル膜を形成し、マイクロ波を照射して、アモルファス領域とニッケル膜とを反応させてニッケルシリサイド膜を形成しつつ、アモルファス領域を固相成長させてアモルファス領域に含まれる不純物を活性化し、未反応のニッケル膜を除去する。

(もっと読む)

半導体基板製品の製造方法、これに用いられる薄膜除去液

【課題】白金(Pt)化合物の薄膜を、他の部材を過度に酸化・腐食することなしに除去する半導体基板製品の製造方法、これに用いられる薄膜除去液を提供する。

【解決手段】白金化合物の薄膜を有する半導体基板を準備する工程と、薄膜除去液を準備する工程と、前記半導体基板に前記薄膜除去液を適用して前記白金化合物の薄膜を除去する工程とを含む半導体基板製品の製造方法であって、前記薄膜除去液が、ハロゲン分子、ハロゲンイオン、及び水を組み合わせて含む半導体基板製品の製造方法。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】歩留まりを向上可能な半導体装置の製造方法および半導体装置を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、半導体基板上に形成される検査用トランジスタおよび製品用トランジスタのソースおよびドレインを活性化させるアニール処理を行うアニール工程と、アニール工程後における検査用トランジスタのゲート、ソースおよびドレインをシリサイド化させる検査用サリサイド工程と、検査用サリサイド工程後における検査用トランジスタの特性を測定する測定工程と、測定工程によって測定された特性と所望の特性との差分とに基づいて製品用トランジスタの特性を所望の特性へ近付ける特性調整アニール処理を行う特性調整アニール工程と、特性調整アニール工程後における製品用トランジスタのゲート、ソースおよびドレインをシリサイド化させる本サリサイド工程とを含む。

(もっと読む)

21 - 40 / 795

[ Back to top ]