Fターム[5F140BK31]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極の形成 (2,400) | CVD (207) | 選択CVD (24)

Fターム[5F140BK31]に分類される特許

1 - 20 / 24

半導体装置およびその製造方法

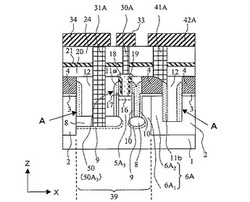

【課題】ゲート電極の断線による縦型トランジスタの故障を改善すること。

【解決手段】半導体装置は、第1の方向(Y)に互いに隙間を空けて形成された複数の半導体ピラー(5A1〜5A5)から成る半導体ピラー群(5)を含む。半導体ピラー群(5)の内、両端部を除く中間部に位置する半導体ピラー(5A2〜5A4)のいずれか1つである特定の半導体ピラー(5A3)と隣接して、ダミーピラー(6)が第1の方向(Y)と直交する第2の方向(X)に設けられている。ゲート絶縁膜(10)が、複数の半導体ピラー(5A1〜5A5)の各々の外周面とダミーピラー(6)の外周面の一部とに形成されている。ゲート絶縁膜(10)を介して、複数の半導体ピラー(5A1〜5A5)の間の隙間と特定の半導体ピラー(5A3)とダミーピラー(6)との間の隙間とを埋めるように、ゲート電極(11)が、複数の半導体ピラーの側面とダミーピラーの側面とに形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク基板上に形成されたフィン型トランジスタにおいて、ソース/ドレインボトム領域での接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上に形成されたシリサイドとの接触抵抗を低減する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】3次元形の半導体素子において、オン抵抗をより効果的に低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、ドレイン層と、ドレイン層内に選択的に設けられたドリフト領域と、ドリフト領域内に選択的に設けられたベース領域と、ベース領域内に選択的に設けられたソース領域と、ソース領域又はドレイン層の少なくとも一方の内部に、ソース領域又はドレイン層の少なくとも一方に選択的に設けられた第1,第2の金属層と、ドレイン層の表面に対して略平行な方向に、ソース領域の一部から、ソース領域の少なくとも一部に隣接するベース領域を貫通して、ドリフト領域の一部にまで到達するトレンチ状のゲート電極と、第1の金属層に接続されたソース電極と、ドレイン層又は第2の金属層に接続されたドレイン電極と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ低抵抗の半導体装置およびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された半導体層と、前記半導体層上に形成され、該半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極と、を備える。また、基板上に半導体層を形成する半導体層形成工程と、前記半導体層上に、前記半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極を形成する電極形成工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極、ソース電極またはドレイン電極にタングステン膜を用いた半導体装置において、nMOSとpMOS間での抵抗差を低減可能な半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極14a,14bとソース/ドレイン拡散層16a,16bとを有するnMOS及びpMOSを形成し、ゲート電極14a,14b及びソース/ドレイン拡散層16a,16b上に、タングステン膜17を選択的に形成し、タングステン膜17を覆うように、絶縁膜(エッチングストップシリコン酸化膜18、シリコン窒化膜19)を形成し、pMOS領域12bの絶縁膜を除去し、pMOS領域12bのタングステン膜17上に、タングステン膜20を選択的に形成する。

(もっと読む)

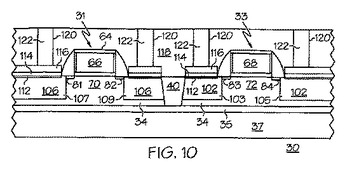

歪みが強化された半導体デバイスとその製造方法

歪みが強化された半導体デバイス30とその製造方法が提供される。1つの方法において、デバイスチャネル70、72に歪みを誘発するために、デバイスのソース領域103、107とドレイン領域105、109とに歪み誘発半導体材料102、106が埋め込まれる。誘発された歪みを緩和しないように、ソースおよびドレイン領域に対して薄い金属シリサイドコンタクト112が形成される。導電性材料114、116の層が薄い金属シリサイドコンタクトに接触して選択的に蒸着され、金属化されたコンタクト122が導電性材料に対して形成される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】DRAM素子の微細化を進めた場合における、周辺回路側のトランジスタの短チャネル効果を抑制すると共に、コンタクト抵抗を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1と、半導体基板1の表面に形成されたMOSトランジスタTr2と、MOSトランジスタTr2のソース108A及びドレイン108Bにそれぞれ接続されるコンタクトプラグ11Aとを具備してなり、コンタクトプラグ11Aが、ソース108A及びドレイン108B上に形成されて不純物が拡散されたエピタキシャル成長層を含んでなることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置

【課題】nチャネルMISトランジスタとpチャネルMISトランジスタとが接続するドレイン領域において、トランジスタ特性を悪化させる不具合が生じないCMOSデバイスを含む半導体装置を提供する。

【解決手段】基板11上の半導体領域に形成されたソース領域18Aと、ドレイン領域17Aとを有するnチャネルMISトランジスタと、半導体領域に形成されたソース領域18Bと、ドレイン領域17Bと有するpチャネルMISトランジスタとを具備する。ドレイン領域17Aと17Bとが接続するように配置されると共に、同一の材料で形成され、ソース領域18A,18Bの少なくともいずれかがドレイン領域17A,17Bと異なる材料で形成されている。

(もっと読む)

半導体装置の製造方法

【課題】所望の仕事関数を有するフルシリサイドゲート電極を形成する。

【解決手段】半導体基板上にゲート絶縁膜を介してポリシリコンを形成して(ステップS1)、ボロンやヒ素等の不純物をイオン注入した後(ステップS2)、そのポリシリコンにレーザを照射する(ステップS3)。このレーザ照射後のポリシリコンをフルシリサイド化し(ステップS4)、フルシリサイドゲート電極を形成する。イオン注入後のレーザ照射により、不純物を固溶限界の制限を受けずにゲート電極材料内に分布させることが可能になるため、導入した不純物の量に応じた仕事関数を有するフルシリサイドゲート電極を形成することが可能になる。

(もっと読む)

半導体装置

【課題】埋め込み特性や膜特性に優れたシリコン酸化膜を高アスペクト比を有する凹部に形成することが可能な半導体装置を提供すること。

【解決手段】半導体装置は、半導体基板の主表面側に形成された凹部を有する下地領域と、前記下地領域の凹部内全体に埋め込まれた塩素を含有するシリコン酸化膜とを有することを特徴とする。

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域上に膜厚及び膜質の均一なシリサイド層を形成することができ、MOS構造における接合リークを低く抑えることができ、且つシリサイド層と金属配線との良好な電気的接続を確保する。

【解決手段】ソース・ドレイン領域の上部にシリサイド層を備えたMOS構造の半導体装置の製造方法であって、シリサイド層を形成すべきソース・ドレイン領域121の表面に2.5×1013cm-2以上5×1014cm-2以下のAs原子を化学吸着させた後、ソース・ドレイン領域上に金属膜を堆積し、次いで熱処理を施すことによって金属膜をシリサイド化する。

(もっと読む)

半導体装置の製造法

【課題】本発明の目的は、ゲート絶縁膜中への不純物混入の抑制と元素欠陥を除去することができ、ゲート絶縁膜の固定電荷フリ−とリ−クの発生等を抑制できる半導体装置の製造法を提供することにある。

【解決手段】本発明は、シリコン単結晶基板上に、ゲート絶縁膜を形成する半導体装置の製造法において、前記ゲート絶縁膜を、水酸化アンモニウムガスと、ハフニウムの化合物ガスとを用いてOH基に交換されたシリコン単結晶基板表面に特定の反応によって形成された金属の酸化−水酸化物を酸化性雰囲気中で熱処理してSiとHfとの複合酸化物からなる膜を形成することを特徴とする。

(もっと読む)

接続部構造及びその製造方法

【課題】シリサイド上に接続孔を形成する際のエッチングで、高抵抗の変質層が発生することを防止する。

【解決手段】 基板中もしくは基板上に導電層を形成する。次に、導電層上を含む基板上に第1の金属膜を形成する。次に、基板に対して熱処理を行なって第1の金属膜と導電層とを反応させ、導電層上に選択的にシリサイド膜を形成する。次に、選択CVD法によりシリサイド膜上のみに第2の金属膜を形成する。次に、第2の金属膜上を含む基板上に絶縁膜を形成する。次に、絶縁膜の所定領域を開口して、第2の金属膜に到達するコンタクトホールを形成する。次に、コンタクトホール内を洗浄して、コンタクトホール底面における第2の金属膜表面に形成された変質層を除去する。

(もっと読む)

半導体装置の製造方法

【課題】浅い接合領域上に、低抵抗で均一なニッケルモノシリサイド層を形成する。

【解決手段】絶縁膜およびシリコン領域が形成されたシリコン基板上に金属ニッケル膜を、前記絶縁膜およびシリコン領域を覆うように形成し、前記シリコン基板を熱処理し、前記シリコン領域表面および前記金属ニッケル膜の表面に、組成が主としてNi2Siで表される第1のニッケルシリサイド層を形成し、前記第1のニッケルシリサイド層形成工程の後、前記金属ニッケル膜をウェットエッチング処理により除去し、前記第1のニッケルシリサイド層を、シランガス中における熱処理により、ニッケルモノシリサイド(NiSi)を主とする第2のニッケルシリサイド層に変換する。

(もっと読む)

半導体素子の製造方法

【課題】金属シリサイド膜を有する半導体素子の製造方法を提供する。

【解決手段】半導体基板100上にゲートスタック110が配置され、基板100の上部及びゲートスタック110の側壁にゲートスペーサ膜120が配置され、ゲートスタック120の間に絶縁膜130が配置される構造体を形成する。絶縁膜130を取り除いてゲートスペーサ膜120を露出させる。ゲートスペーサ膜120上に犠牲絶縁膜を形成する。ゲートスタック120側壁のゲートスペーサ膜120上の犠牲絶縁膜は残り、基板100上部のゲートスペーサ膜120上の犠牲絶縁膜は取り除かれるように犠牲絶縁膜の一部を取り除く。基板100上のゲートスペーサ膜120を取り除き、ゲートスタック120の間の基板100を露出させる。ゲートスタック120の間の基板100の露出面上に金属シリサイド膜を形成する。

(もっと読む)

多層配線基板の製造方法、半導体装置の製造方法、及び電子デバイス

【課題】 カーボンナノチューブを用いた配線を高価なエッチング装置などを用いることなく、簡易な方法で実現することができる配線技術を提供する。

【解決手段】 基板11の表面にAlなどからなる下層配線12を形成した後(図2(a)参照)、下層配線12のうちカーボンナノチューブ16を配置すべき箇所に触媒金属含有層14を形成する。次に、熱CVD法などにより触媒金属含有層14の上にカーボンナノチューブ16を形成し、触媒金属含有層14からカーボンナノチューブ16を垂直方向に選択的に成長させる(図2(b)参照)。さらに、カーボンナノチューブ16を選択成長させた基板11の上に塗布法を用いて層間絶縁膜13を形成した後(図2(c)参照)、スパッタ法などによりカーボンナノチューブ16の上端部及び層間絶縁膜13を覆う上層配線層15を形成する(図2(d)参照)。

(もっと読む)

半導体装置およびその製造方法

【課題】従来のサリサイド法により、活性領域、ゲート電極上にシリサイド層を形成すると、Siがシリサイド化反応により消費されるため、シリサイド層が活性領域のソース・ドレインを突き抜けたり、ゲート電極の抵抗が高くなったりする。

【解決手段】シリコン基板11上にゲート電極14用のポリシリコン膜を形成するとともにシリコン基板11にソース・ドレイン領域16を形成し、次いでソース・ドレイン領域16においてニッケル膜との熱反応で選択的なエピタキシャル成長によるニッケルジシリサイド層17を形成し、次いでゲート電極14用のポリシリコン膜においてニッケル膜との熱反応で選択的なエピタキシャル成長によるニッケルモノシリサイド層18を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、シリサイドプロセスを適用したMOSFETにおいて、シリサイド膜をより大きく形成できるようにする。

【解決手段】たとえば、シリコン基板11の表面上に設けられたゲート電極16の側面には、それぞれ、内側ゲート側壁膜18および外側ゲート側壁膜21が形成されている。一方、ゲート電極16の形成位置を除く、シリコン基板11の表面部には、浅い低濃度拡散層17、および、二段構造の浅い高濃度拡散層19と深い高濃度拡散層22とが形成されている。そして、浅い高濃度拡散層19および深い高濃度拡散層22に対応するシリコン基板11の表面部には、それぞれの高濃度拡散層19,22の深さに応じて厚さの異なる二段構造のシリサイド膜23が形成されている。

(もっと読む)

1 - 20 / 24

[ Back to top ]