Fターム[5F152LL08]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 気相 (1,473) | PVD (427) | 蒸着 (45)

Fターム[5F152LL08]に分類される特許

1 - 20 / 45

シリコン単結晶膜およびその製造方法

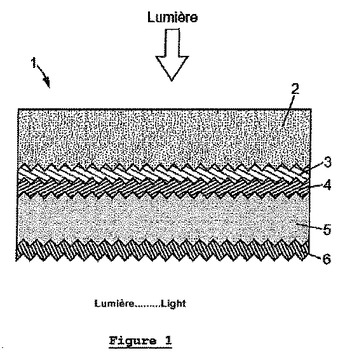

【課題】薄層化された自立性のシリコン単結晶膜を提供し、また、剥離時の熱処理温度を格段に低減することができる新たなシリコン単結晶膜の形成方法を提供する。

【解決手段】シリコン単結晶膜6は、Siの含有率が、90原子%以上であり、厚みが、50μm以下であり、自立性がある。

(もっと読む)

半導体膜蒸着装置および半導体膜蒸着方法

【課題】半導体膜の表面欠陥の発生を抑制する半導体膜蒸着装置および半導体膜蒸着方法を提供する。

【解決手段】

半導体原料を収容するるつぼ2と、るつぼ2と対向して基板5を支持する基板支持器6と、るつぼ2と基板5との間でるつぼ2の開口を覆って配置されるマスク4と、るつぼ2およびマスク4を加熱する加熱器3と、るつぼ2、基板支持器6、およびマスク4を収容する真空チャンバ7とを備える半導体膜蒸着装置。るつぼ2から飛散した半導体分子はマスク4内部を衝突しながら通過することで基板5上に表面欠陥が抑制された状態で成膜される。

(もっと読む)

窒化物半導体装置および窒化物半導体装置の製造方法

【課題】オン抵抗が低く、かつ、Vth(閾値電圧)が高い窒化物半導体装置の提供。

【解決手段】アクセプタになるアクセプタ元素を含み、窒化物半導体で形成されたバックバリア層106と、バックバリア層106上に窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップが大きい窒化物半導体で形成された電子供給層112と、チャネル層108と電気的に接続された第1主電極116、118と、チャネル層108の上方に形成された制御電極120と、を備え、バックバリア層106は、制御電極120の下側の領域の少なくとも一部に、アクセプタの濃度がバックバリア層の他の一部の領域より高い高アクセプタ領域126を有する窒化物半導体装置100。

(もっと読む)

半導体材料、半導体材料の製造方法及び半導体素子

【課題】pn接合のI−V特性を向上させる半導体材料を提供すること。

【解決手段】本発明に係る半導体材料は、酸化亜鉛の結晶を含有する粒子を備え、酸化亜鉛の結晶子の大きさが5〜50nmであり、酸化亜鉛の結晶における窒素の含有率が500〜10000質量ppmである。

(もっと読む)

単結晶シリコン薄膜の製造方法、単結晶シリコン薄膜デバイスの製造方法及び太陽電池デバイスの製造方法並びに単結晶シリコン薄膜及びそれを用いた単結晶シリコン薄膜デバイス及び太陽電池デバイス

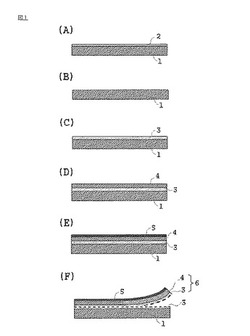

【課題】 ELOを利用して単結晶シリコン薄膜を製造するに際し、犠牲層のエッチングを容易にする単結晶シリコン薄膜の製造方法、単結晶シリコン薄膜デバイスの製造方法及び太陽電池デバイスの製造方法並びに単結晶シリコン薄膜及びそれを用いた単結晶シリコン薄膜デバイス及び太陽電池デバイスを提供する。

【解決手段】 単結晶シリコン基板1の表面にシリコンに対してエッチング選択性を有し且つエピタキシャルな関係にある犠牲層2を設け、該犠牲層2上に単結晶シリコン薄膜40をエピタキシャル成長させ、該単結晶シリコン薄膜40に複数の貫通孔42を形成すると共に当該貫通孔42を介して前記犠牲層2をエッチングし、単結晶シリコン薄膜4を分離する。

(もっと読む)

半導体装置およびその製造方法

【課題】基板の材質に関係なく半導体回路部分への高熱処理が可能な半導体装置の製造方法を提供する。

【解決手段】樹脂基板2上にシリコーン樹脂で密度が0.7g/cm3以下の多孔質構造体層4を設ける。ここでシリコーン樹脂は95質量%以上がシルセスキオキサンまたはシロキサンからなり、シルセスキオキサンはメチルシルセスキオキサンまたはフェニルシルセスキオキサンであることが好ましい。この多孔質構造体層上に半導体素子層3を設け、この半導体素子層側からのみ間欠的に光または電子線により加熱する。

(もっと読む)

ナノ/微小球リソグラフィによって製造されるナノ/マイクロワイヤ太陽電池

【課題】 ナノ/微小球リソグラフィによって製造されるナノ/マイクロワイヤ太陽電池を提供する。

【解決手段】 ナノワイヤ/マイクロワイヤ・ベースの太陽電池を製造する技術が提供される。一実施形態において、太陽電池を製造する方法が提供される。本方法は、以下のステップを含む。ドープ基板を準備する。基板の上に球の単層を堆積させる。球は、ナノ球、微小球、又はそれらの組み合わせを含む。球をトリミングして単層内の個々の球の間に空間を設ける。トリミングされた球をマスクとして用いて、基板内にワイヤをパターン形成する。ワイヤは、ナノワイヤ、マイクロワイヤ、又はそれらの組み合わせを含む。ドープ・エミッタ層をパターン形成されたワイヤ上に形成する。上部コンタクト電極をエミッタ層の上に堆積させる。底部コンタクト電極を基板のワイヤとは反対の側に堆積させる。

(もっと読む)

III族窒化物半導体成長用基板、III族窒化物半導体エピタキシャル基板、III族窒化物半導体素子およびIII族窒化物半導体自立基板、ならびに、これらの製造方法

【課題】成長温度が1050℃以下のAlGaNやGaNやGaInNだけでなく、成長温度が高い高Al組成のAlxGa1-xNにおいても結晶性の良いIII族窒化物半導体エピタキシャル基板、III族窒化物半導体素子、III族窒化物半導体自立基板およびこれらを製造するためのIII族窒化物半導体成長用基板、ならびに、これらを効率よく製造する方法を提供する。

【解決手段】少なくとも表面部分がAlを含むIII族窒化物半導体からなる結晶成長基板と、前記表面部分上に形成されたスカンジウム窒化物膜とを具えることを特徴とする。

(もっと読む)

窒化物単結晶の製造方法、テンプレート基板、および窒化物単結晶基板

【課題】窒化物単結晶膜におけるクラックの発生を抑制する窒化物単結晶膜の製造方法、クラックの発生が抑制された窒化物単結晶基板、およびクラックの発生が抑制された窒化物単結晶膜を備えるテンプレート基板を提供する。

【解決手段】窒化物単結晶膜の製造方法は、(11−20)面からのオフ角が5°以下である下地基板1を準備する工程と、上記下地基板1の主表面上に窒化物単結晶膜3を形成する工程とを備える。前記下地基板1はSiCまたはサファイアからなることが好ましく、また、前記窒化物単結晶膜3を形成する工程における成膜温度範囲は1700℃以上2400℃以下であることが好ましい。これにより、前記テンプレート基板4の窒化物単結晶膜3はクラックの密度が低く、また、前記テンプレート基板4から下地基板1を取り除いた窒化物単結晶基板についても同様に、クラックの密度が低くなる。

(もっと読む)

トップゲート型の電界効果型トランジスタ及びその製造方法並びにそれを備えた表示装置

【課題】活性層としてIn−Ga−Zn−O系酸化物半導体を用い、移動度が高く、かつ、製造が容易な電界効果型トランジスタ及びその製造方法並びにそれを備えた表示装置を提供する。

【解決手段】In2−XGaXZnO4(0.6<X<0.8)からなる活性層12と、前記活性層を介して導通可能なソース電極16A及びドレイン電極16Bと、前記活性層、前記ソース電極、及び前記ドレイン電極を覆う絶縁層18と、前記絶縁層を介して前記活性層に対向配置されたゲート電極20と、前記活性層と前記絶縁層との間に介在する酸化インジウムを含む層14と、有することを特徴とするトップゲート型の電界効果型トランジスタ22。好ましくは、前記酸化インジウムは、活性層から析出されたものである。

(もっと読む)

グラフェン層が成長された基板およびそれを用いた電子・光集積回路装置

【課題】グラフェン層成膜の大面積化や基板材質の選択自由度の拡大、製造の低コスト化を実現するグラフェン層が成長された基板およびそれを用いた電子・光集積回路装置を提供する。

【解決手段】本発明に係るグラフェン層が成長された基板は、単層または複数層からなるグラフェン層が成長された基板であって、前記グラフェン層は前記基板の表面に対して略平行に成長しており、前記グラフェン層に対向する前記基板の最表面には金属酸化物の原子層が存在し、前記グラフェン層の前記基板に隣接する層と前記金属酸化物の原子層との層間距離が0.34 nm以下であることを特徴とする。また、前記金属酸化物の原子層の算術平均表面粗さRaが1 nm以下であることが好ましい。

(もっと読む)

ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置

【課題】格子定数が広範囲にわたり可変であり、且つ結晶性に優れた基板およびその製造方法を提供する。また上記基板上に形成された半導体素子を提供する。

【解決手段】6回対称軸をを有する結晶からなる第1の層11と、該結晶上に形成される金属酸窒化物結晶からなる第2の層12を有し、第2の層12が、In、Ga、Si、Ge及びAlからなる群から選択される少なくとも1つの元素と、NとOとZnとを主要元素として含み、且つ第2の層12が面内配向性を有する積層構造体を備えたウルツ鉱型結晶成長用基板。

(もっと読む)

多層膜構造体およびその形成方法

【課題】半導体素子用の多層膜構造体を基板上に形成する多層膜構造体であって、大きな伸張歪を半導体層に印加できる多層膜構造体の形成方法を提供する。

【解決手段】半導体素子用の多層膜構造体10を基板上に形成する際に、基板11上に、当該基板11を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、圧縮歪を有する圧縮歪半導体層12を形成する。その圧縮歪半導体層12の上方に、圧縮歪半導体層12を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、無歪の無歪半導体層13を積層する。圧縮歪半導体層12の圧縮歪を緩和させることにより、無歪半導体層13に伸張歪を印加する。それにより、大きな伸張歪を無歪半導体層13に印加することができる。

(もっと読む)

マイクロヒーターアレイ及びマイクロヒーターアレイを備えたpn接合、並びにその形成方法

【課題】ガラス基板などの低価で且つ用意し易い基板上に高品質のpn接合を形成することができ、pn接合を大面積化することができるマイクロヒーターアレイ及びpn接合の形成方法を提供する。

【解決手段】本発明による一実施の形態によるマイクロヒーターアレイは、基板上に互いに交差して設けられる、または互いに並設される第1及び第2マイクロヒーターを含む。また、一実施の形態によるpn接合の形成方法は、上記マイクロヒーターアレイに電圧を印加し第1及び第2加熱部からの発熱を利用して第1及び第2加熱部の間にpn接合を形成する。このようにマイクロヒーターを利用してpn接合を形成する場合、ガラス基板上の大面積にわたって高品質のpn接合を形成することができる。

(もっと読む)

結晶基板およびGaN系結晶膜の製造方法

【課題】GaN系半導体デバイスの結晶成長用に適した、欠陥密度の小さい高品質のGaN系結晶膜連続膜を備えた結晶基板を得る。

【解決手段】GaN系半導体デバイス形成用基板として用いる結晶基板において、表面がC面のサファイア基板101と、該サファイア基板101上に形成されたGaNバッファ層102と、該GaNバッファ層102上に形成されたエピタキシャル成長GaN層103と、該エピタキシャル成長層103上に形成された、複数の開口部105を有するSiO2膜104と、該SiO2膜104の開口部105にGaN系化合物の選択再結晶化により形成された複数の島状GaN系結晶11と、該島状GaN系結晶11を核とするGaN系結晶の成長により形成されたGaN系結晶連続膜12とを備えた。

(もっと読む)

結晶成長シミュレーター

【課題】次世代の光半導体デバイス開発の基礎になるものと期待されている、量子ドットの形成過程について、従来の静的な計算結果ではなく、動的過程を解明するための有効な計算方法を提供する。

【解決手段】対象を三領域に分割し、そのそれぞれで別系統の計算手法を適用することにより、マルチスケールかつハイブリッドな計算機シミュレーションの方法を実現している。それらのうち、最上部の表面層領域における原子拡散により引き起こされた歪みの効果を、中間部のサブメッシュ上の分離力学計算領域に伝え、この領域で緩和をおこなった結果を、下部領域にある有限要素法の計算部分に伝達することにより、隔たった領域間の歪みの相互作用の効果を、中間部を通じて表面領域にフィードバックさせるようなアルゴリズムが構成できる。また、そのアルゴリズムを実現するシステムを構築する。

(もっと読む)

炭化珪素基板の表面処理方法および半導体装置

【課題】より広い幅を有するテラスを形成することができる炭化珪素基板の表面処理方法およびその炭化珪素基板の表面処理方法により表面処理された炭化珪素基板を用いて製造された半導体装置を提供する。

【解決手段】炭化珪素基板の表面上に固体状シリコンを設置する工程と、固体状シリコン上に蓋材を設置する工程と、蓋材の設置後に固体状シリコンが設置された炭化珪素基板を固体状シリコンの融点以上の温度に加熱して固体状シリコンを溶融させる工程と、固体状シリコンの溶融後に固化した固化シリコンから炭化珪素基板を分離する工程とを含む炭化珪素基板の表面処理方法とその炭化珪素基板の表面処理方法により表面処理された炭化珪素基板を用いて製造された半導体装置である。

(もっと読む)

有機薄膜の製造方法

【課題】基板上に大面積の単結晶の有機薄膜を形成することができる有機薄膜の製造方法を提供する。

【解決手段】基板上に第1の有機分子からなる規則的な分子配列を有する第1の有機分子層を形成する工程と、前記第1の有機分子層の上にエピタキシャル成長する第2の有機分子層を形成する工程と、前記第1の有機分子層を昇華、蒸発あるいは溶解して前記第2の有機分子層から除去する工程を有する有機薄膜の製造方法。前記第1の有機分子がアントラセン、前記第2の有機分子がペンタセンであることが好ましい。

(もっと読む)

CVDまたはPVDによってホウ素化合物を蒸着させるためのプロセス

本発明は、支持材上への、化学気相蒸着(CVD)または物理気相蒸着(PVD)による蒸着のためのプロセスに関し、前記プロセスは少なくとも1つのホウ素化合物を使用する。このプロセスは光起電力太陽電池を製造するために特に有用である。本発明は、CVDまたはPVD蒸着プロセスにおいて、材料に光学的および/または電気的特性を与えるためにホウ素化合物を使用することにも関する。このプロセスは、光起電力太陽電池を製造するためにも特に有用である。  (もっと読む)

(もっと読む)

鉄シリサイド形成方法

【課題】簡便な方法により単相の鉄シリサイドが形成できるようにする。

【解決手段】シリコン基板(シリコン層)101の上に、例えば膜厚1.8nmのシリコン酸化層102が形成された状態とする。次に、所定の膜厚の鉄層103がシリコン酸化層102の上に形成された状態とする。以上のようにして、シリコン基板101の上にシリコン酸化層102を介して鉄層103が形成された状態とした後、これらを所定の温度条件で加熱することで、鉄層103の鉄をシリコン酸化層102を介してシリコン基板101のシリコンと反応させてシリサイドを形成させることで、シリコン基板101の上に単相(α相)のFeSi2(α−FeSi2)かなる鉄シリサイド層104が形成された状態とする。

(もっと読む)

1 - 20 / 45

[ Back to top ]